Duty Cycle And Vox Correction For Complementary Signals

Tang; Tianyu ; et al.

U.S. patent application number 15/875400 was filed with the patent office on 2019-04-11 for duty cycle and vox correction for complementary signals. This patent application is currently assigned to SanDisk Technologies LLC. The applicant listed for this patent is SanDisk Technologies LLC. Invention is credited to Srinivas Rajendra, Venkatesh Ramachandra, Tianyu Tang.

| Application Number | 20190109584 15/875400 |

| Document ID | / |

| Family ID | 65993523 |

| Filed Date | 2019-04-11 |

View All Diagrams

| United States Patent Application | 20190109584 |

| Kind Code | A1 |

| Tang; Tianyu ; et al. | April 11, 2019 |

DUTY CYCLE AND VOX CORRECTION FOR COMPLEMENTARY SIGNALS

Abstract

A correction system is configured to correct for duty cycle distortion and/or cross-point distortion in a pair of sample signals. A slope adjustment circuit is configured to generate a plurality of pairs of intermediate signals according to a plurality of drive strengths. A measurement circuit is configured to measure for duty cycle distortion and/or cross-point distortion, and the slope adjustment circuit is configured to set the plurality of drive strengths based on the measurement. The setting of the drive strengths may reduce certain rising and falling slopes of certain transitions of the plurality of intermediate signals, which in turn may reduce duty cycle distortion and/or cross-point distortion in the sample signals.

| Inventors: | Tang; Tianyu; (Milpitas, CA) ; Ramachandra; Venkatesh; (San Jose, CA) ; Rajendra; Srinivas; (Milpitas, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | SanDisk Technologies LLC Plano TX |

||||||||||

| Family ID: | 65993523 | ||||||||||

| Appl. No.: | 15/875400 | ||||||||||

| Filed: | January 19, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 62571109 | Oct 11, 2017 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H03K 17/687 20130101; H03M 1/66 20130101; H03K 5/1565 20130101; H03K 17/6871 20130101; H03K 3/017 20130101 |

| International Class: | H03K 3/017 20060101 H03K003/017; H03K 17/687 20060101 H03K017/687; H03M 1/66 20060101 H03M001/66 |

Claims

1. A circuit comprising: a complementary signal path circuit configured to receive a pair of complementary input signals and generate a pair of complementary output signals, wherein the complementary signal path circuit comprises: a plurality of pairs of circuit stages, wherein each pair of circuit stages is configured to generate a respective one of a plurality of pairs of complementary intermediate signals; and a control circuit configured to: measure a duty cycle distortion of a pair of complementary sample signals; and in response to the measurement, set drive strengths of the plurality of pairs of circuit stages.

2. The circuit of claim 1, wherein the control circuit is further configured to: in response to the measurement of the duty cycle distortion, select a target drive strength value from among a plurality of drive strength values, the target drive strength value indicating a plurality of drive strength amounts; and set each pair of circuit stages of the plurality of pairs of circuit stages to a respective one of the plurality of drive strength amounts indicated by the drive strength value.

3. The circuit of claim 2, wherein the control circuit is further configured to: set each pair of circuit stages of the plurality of pairs of circuit stages also to an initial drive strength amount, wherein each of the plurality of drive strength amounts indicated by the drive strength value is lower than the initial drive strength amount.

4. The circuit of claim 2, wherein the target drive strength value corresponds to a digital-to-analog converter (DAC) code indicating whether to activate or deactivate each of a plurality of branches of the set of circuit stages.

5. The circuit of claim 1, wherein branches of the circuit stages of the plurality of pairs of circuit stages comprise a binary-weighted configuration.

6. The circuit of claim 1, wherein a circuit stage of the plurality of pairs of circuit stages comprises a plurality of drive strength sub-branches and a plurality of stability sub-branches, wherein a respective stability sub-branch is configured to bias a respective drive strength sub-branch in response to an associated drive strength sub-signal output at a level to deactivate the drive strength sub-branch.

7. The circuit of claim 1, wherein a circuit stage of the plurality of pairs of circuit stages comprises: a plurality of drive strength transistors configured to set a pull-up drive strength of a pull-up portion of the circuit stage or a push-down drive strength of a push-down portion of the circuit stage; and a plurality of input transistors connected in parallel with each other, the plurality of input transistors configured to receive an input signal of the complementary input signals or an intermediate signal of the plurality of pairs of complementary intermediate signals, wherein a length of a first physical connection that connects together terminals of the plurality of drive strength transistors is shorter than a length of a second physical connection that connects together terminals of the plurality of drive strength transistors.

8. The circuit of claim 1, wherein the pair of complementary sample signals comprises the pair of complementary output signals.

9-20. (canceled)

21. A circuit comprising: means for receiving a pair of complementary input signals; means for generating a plurality of pairs of complementary intermediate signals according to drive strengths; means for measuring a duty cycle distortion of a pair of complementary sample signals; and means for setting the drive strengths in response to the means for measuring the duty cycle distortion.

22. A method comprising: generating, with a complementary signal path circuit, a pair of complementary output signals in response to receiving a pair of complementary input signals; generating, with a plurality of pairs of circuit stages of the complementary signal path circuit, a plurality of pairs of complementary intermediate signals; measuring, with a control circuit, a duty cycle distortion of a pair of complementary sample signals; and in response to the measuring, set drive strengths of the plurality of pairs of circuit stages.

23. The method of claim 22, further comprising: in response to the measuring, selecting, with the control circuit, a target drive strength value from among a plurality of drive strength values, the target drive strength value indicating a plurality of drive strength amounts; and setting, with the control circuit, each pair of circuit stages of the plurality of pairs of circuit stages to a respective one of the plurality of drive strength amounts indicated by the drive strength value.

24. The method of claim 23, further comprising: setting, with the control circuit, each pair of circuit stages of the plurality of pairs of circuit stages also to an initial drive strength amount, wherein each of the plurality of drive strength amounts indicated by the drive strength value is lower than the initial drive strength amount.

25. The method of claim 23, wherein the target drive strength value corresponds to a digital-to-analog converter (DAC) code indicating whether to activate or deactivate each of a plurality of branches of the set of circuit stages.

26. The method of claim 22, wherein branches of the circuit stages of the plurality of pairs of circuit stages comprise a binary-weighted configuration.

27. The method of claim 22, wherein a circuit stage of the plurality of pairs of circuit stages comprises a plurality of drive strength sub-branches and a plurality of stability sub-branches, the method further comprising: biasing, with a respective stability sub-branch, a respective drive strength sub-branch in response to an associated drive strength sub-signal output at a level to deactivate the drive strength sub-branch.

28. The method of claim 22, wherein a circuit stage of the plurality of pairs of circuit stages comprises: setting, with a plurality of drive strength transistors of a circuit stage of the plurality of pairs of circuit stages, a pull-up drive strength of a pull-up portion of the circuit stage or a push-down drive strength of a push-down portion of the circuit stage; and receiving, with a plurality of parallel-connected input transistors of the circuit stage, an input signal of the complementary input signals or an intermediate signal of the plurality of pairs of complementary intermediate signals, wherein a length of a first physical connection that connects together terminals of the plurality of drive strength transistors is shorter than a length of a second physical connection that connects together terminals of the plurality of drive strength transistors.

29. The method of claim 22, wherein the pair of complementary sample signals comprises the pair of complementary output signals.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of U.S. Provisional Application No. 62/571,109, filed Oct. 11, 2017. The contents of U.S. Provisional Application No. 62/571,109 are incorporated by reference in their entirety.

BACKGROUND

[0002] In memory applications, a storage device may include a controller that sends a complementary pair of clock signals to a memory die in order to read data from the memory die. In response to the clock signals, the memory die may align data pulses of data signals to the edges of the clock signals and send the aligned data signals along with clocks signals back to the controller. The controller may then process the data signals using the clock signals.

[0003] Typically, the clocks signals have a 50% duty cycle. In an ideal situation, the controller generates the clock signals with the 50% duty cycle, and the duty cycle remains at 50% throughout the read process. That is, the memory die retrieving the data for the controller receives the clock signals with the 50% duty cycle, maintains the duty cycle at 50% while aligning the data, and transmits the clocks signals with a 50% duty cycle back to the controller.

[0004] However, in actual implementation, due to process-voltage-temperature (PVT) variations and silicon interface impact between the controller die and the memory die, the controller may not generate the clock signals with a 50% duty cycle and/or the duty cycle of clocks signals may shift away from the 50% duty cycle when the memory die aligns the data with the clock signals. Consequently, data valid window generated by these non-50% duty clock signals may shrink such that when the controller receives the data signals and the clock signals from the memory die, the controller may make errors in latching the data. For example, if the clock signals and the data signals are not properly aligned, the controller may miss sampling certain data pulses while sampling others twice. In addition or alternatively, if the duty cycle is sufficiently far from 50%, the controller's resistor-capacitor (RC) components may filter out or attenuate the edges of the clock signals. In turn, the controller may miss sampling certain data pulses because it failed to recognize a clock edge as occurring. In view of the errors that can result when the clock signals are generated away from 50% and/or when the duty cycle shifts away from 50% during data retrieval processes, duty cycle correction schemes that correct the duty cycle and move the duty cycle back to 50% are desirable for high speed data transfer.

BRIEF DESCRIPTION OF THE DRAWINGS

[0005] The accompanying drawings, which are incorporated in and constitute a part of this specification illustrate various aspects of the invention and together with the description, serve to explain its principles. Wherever convenient, the same reference numbers will be used throughout the drawings to refer to the same or like elements.

[0006] FIG. 1 is a block diagram of an example duty cycle correction circuit.

[0007] FIG. 2A shows a timing diagram of a pair of complementary output signals having duty cycle distortion.

[0008] FIG. 2B shows a timing diagram of the pair of complementary output signals having no duty cycle distortion.

[0009] FIG. 3 is a block diagram of an example configuration of a slope adjustment circuit of the example duty cycle correction circuit of FIG. 1.

[0010] FIG. 4 is a block diagram of an example RE stage and an example BRE stage of the configuration of FIG. 3.

[0011] FIG. 5 is a block diagram of example configurations of pull-up and push-down portions of the RE and BRE stages of FIG. 4.

[0012] FIG. 6 is a partial circuit schematic diagram of example configurations of the RE and BRE stages of FIG. 3.

[0013] FIG. 7 is a circuit diagram of an example configuration of a pull-up portion and a push-down portion for the RE and BRE stages of FIG. 3.

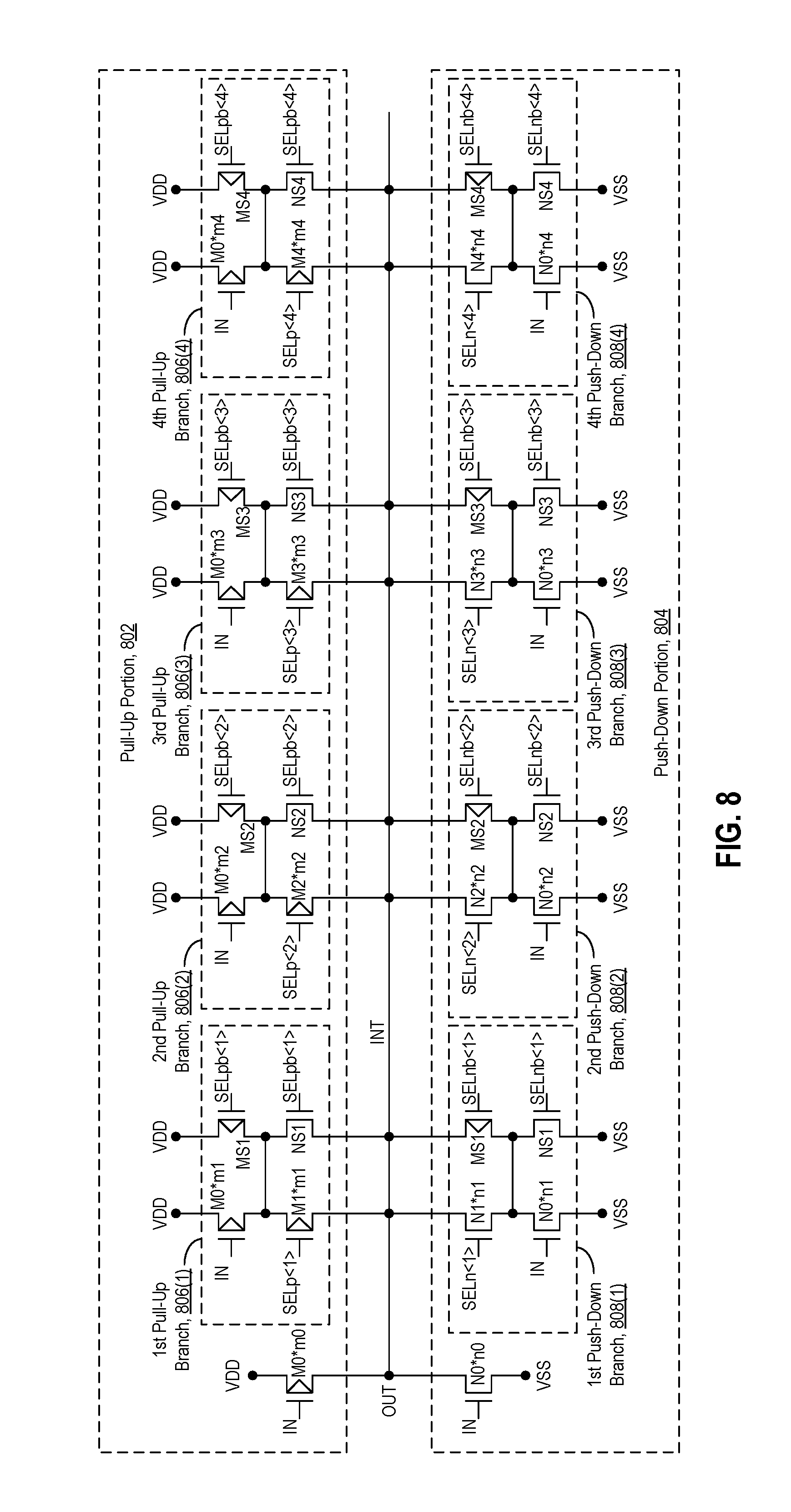

[0014] FIG. 8 is a circuit diagram of another example configuration of a pull-up portion and a push-down portion for the RE and BRE stages of FIG. 3.

[0015] FIG. 9 is a circuit diagram of another example configuration of a pull-up portion and a push-down portion of the RE and BRE stages of FIG. 3.

[0016] FIG. 9 is a block diagram of an example configuration of the adjustable drive strength circuit of FIG. 1.

[0017] FIG. 10A is a timing diagram of output signals having duty cycle distortion before slope adjustment is performed.

[0018] FIG. 10B is a timing diagram of input signals having duty cycle distortion before slope adjustment is performed.

[0019] FIG. 10C is a timing diagram of a pair of complementary signals with reduced slopes that correspond to an output signal to have its duty cycle increased.

[0020] FIG. 10D is a timing diagram of a pair of complementary signals with reduced slopes that correspond to an output signal to have its duty cycle decreased.

[0021] FIG. 10E is a timing diagram of a last pair of intermediate signals with duty cycle distortion eliminated.

[0022] FIG. 10F is a timing diagram of the pair of output signals of FIG. 10 with duty cycle distortion eliminated.

[0023] FIG. 11 is a block diagram of the RE and BRE stages of FIG. 3, with their respective pull-up and push-down portions identified as selected or unselected in response to an identification that a duty cycle of a second output signal is initially higher than a duty cycle of a first output signal.

[0024] FIG. 12 is a block diagram of the RE and BRE stages of FIG. 3, with their respective pull-up and push-down portions identified as selected or unselected in response to an identification that a duty cycle of a first output signal is initially higher than a duty cycle of a second output signal.

[0025] FIG. 13 is a block diagram of an example cross-point correction system.

[0026] FIG. 14A is a timing diagram of a pair of output signals without cross-point distortion.

[0027] FIG. 14B is a timing diagram of a pair of output signals with cross-point distortion having a negative polarity.

[0028] FIG. 14C is a timing diagram of a pair of output signals with cross-point distortion having a positive polarity.

[0029] FIG. 15A is a timing diagram of a pair of output signals with cross-point distortion having a negative polarity before slope reduction is performed.

[0030] FIG. 15B is a timing diagram of a pair of intermediate signals having their rising slopes reduced.

[0031] FIG. 15C is a timing diagram of a pair of intermediate signals having their falling slopes reduced.

[0032] FIG. 15D is a timing diagram of a last pair of intermediate signals with cross-point distortion eliminated.

[0033] FIG. 15E is a timing diagram of the output signals of FIG. 16A with the cross-point distortion eliminated.

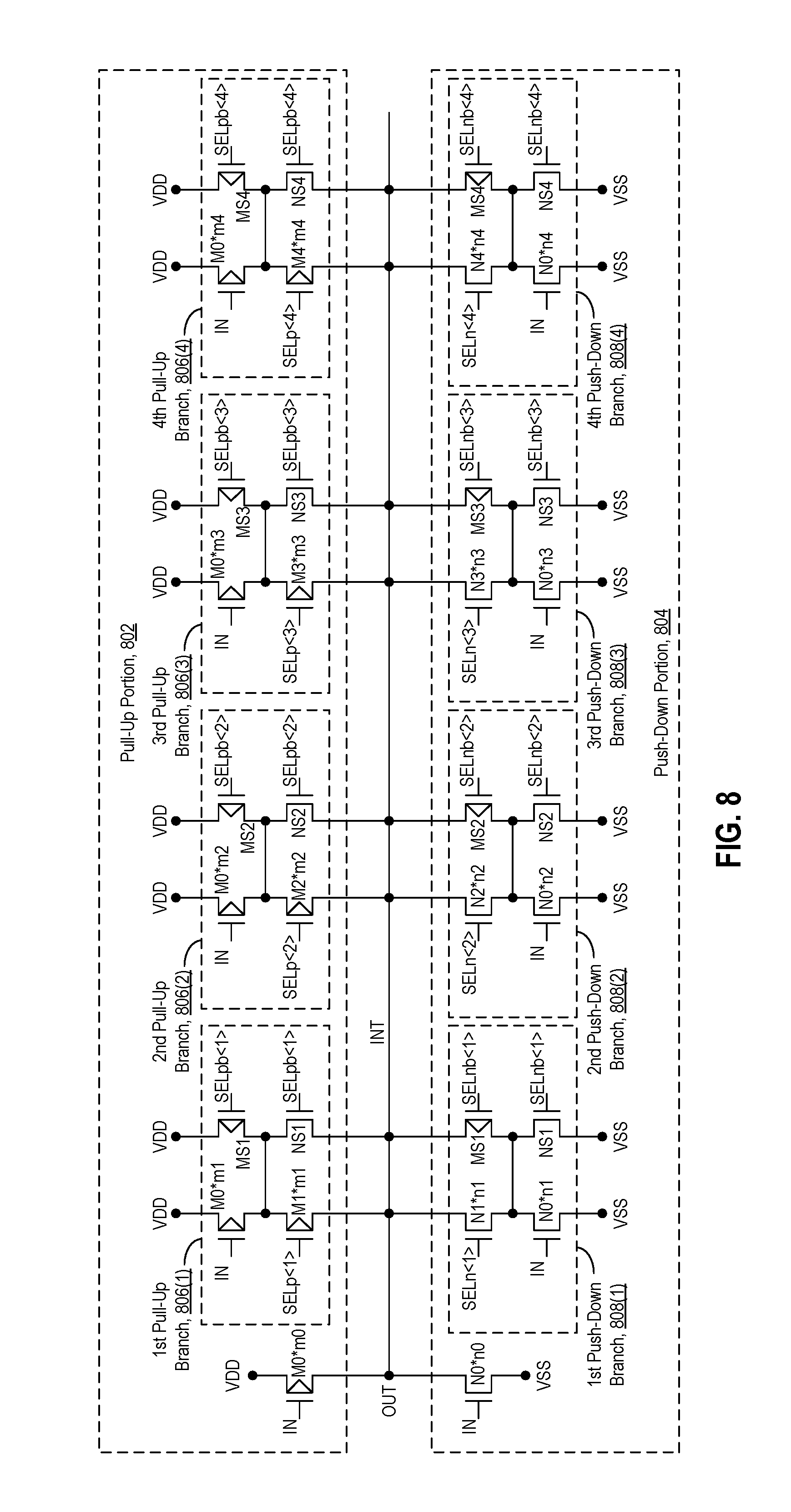

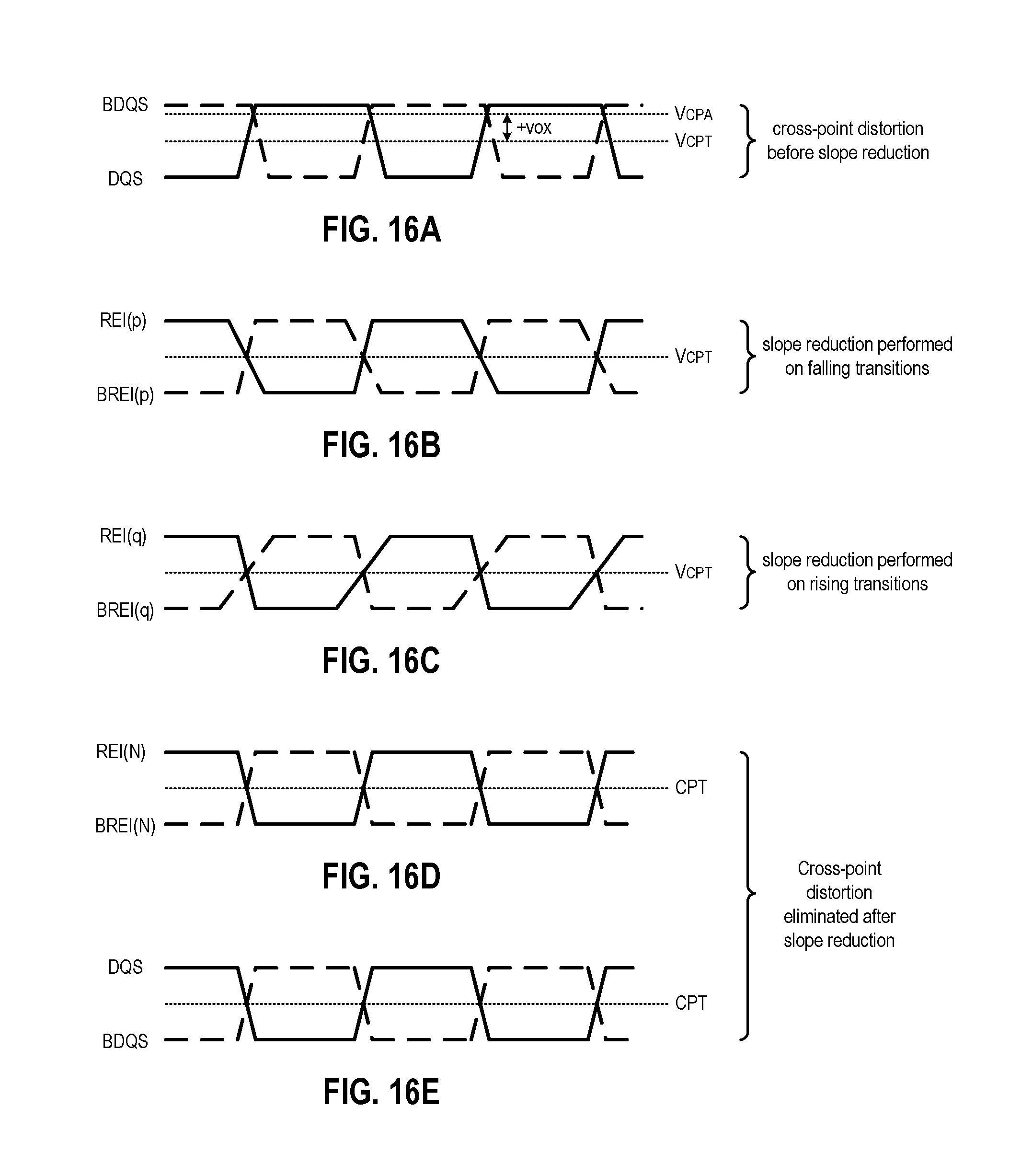

[0034] FIG. 16A is a timing diagram of a pair of output signals with cross-point distortion having a positive polarity before slope reduction is performed.

[0035] FIG. 16B is a timing diagram of a pair of intermediate signals having their falling slopes reduced.

[0036] FIG. 16C is a timing diagram of a pair of intermediate signals having their rising slopes reduced.

[0037] FIG. 16D is a timing diagram of a last pair of intermediate signals with cross-point distortion eliminated.

[0038] FIG. 16E is a timing diagram of the output signals of FIG. 16A with the cross-point distortion eliminated.

[0039] FIG. 17 is a block diagram of the RE and BRE stages of FIG. 3, with their respective pull-up and push-down portions identified as selected or unselected in response to an identification that a cross-point distortion has an initially negative polarity.

[0040] FIG. 18 is a block diagram of the RE and BRE stages of FIG. 3, with their respective pull-up and push-down portions identified as selected or unselected in response to an identification that a cross-point distortion has an initially positive polarity.

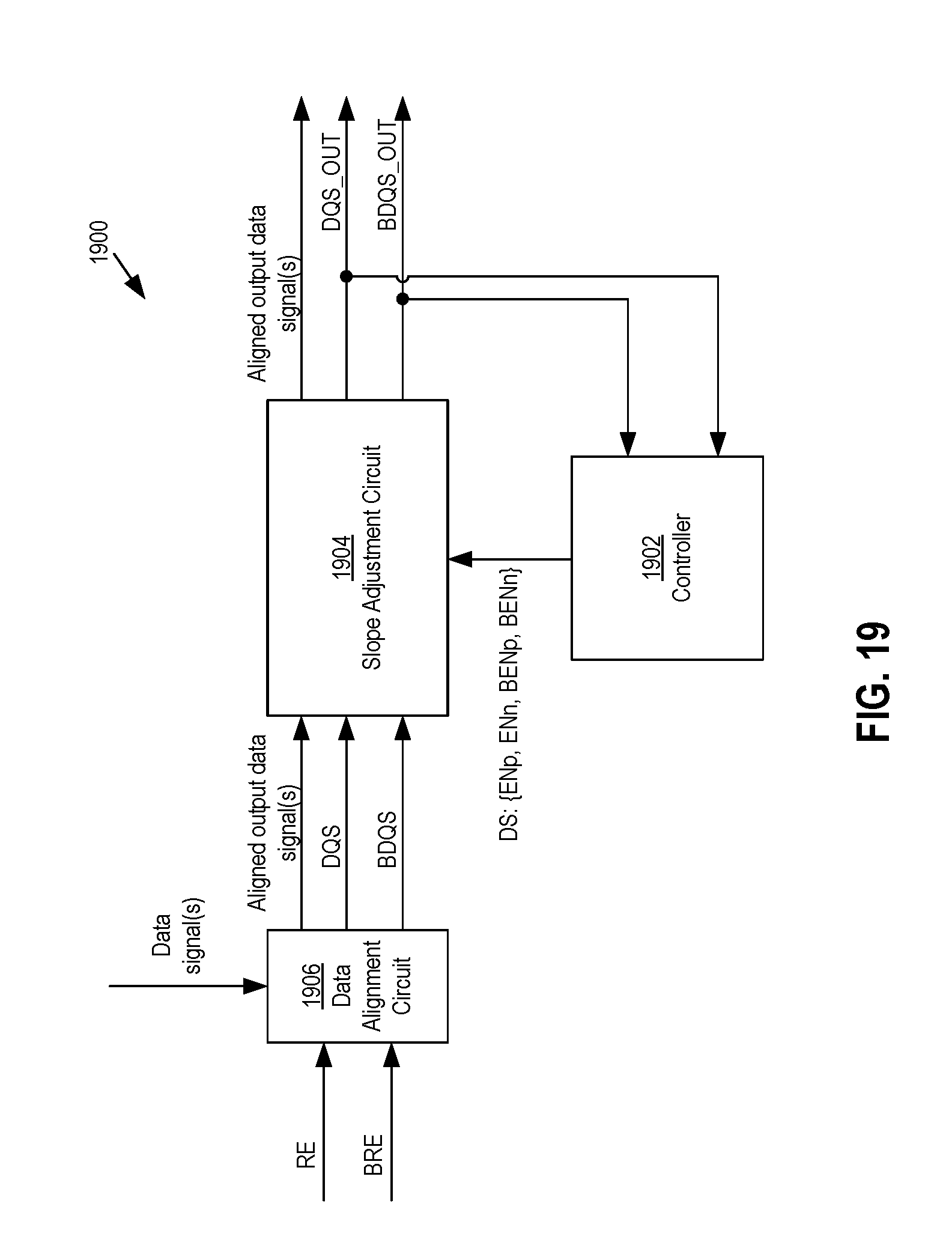

[0041] FIG. 19 is a block diagram on an example correction system with a slope adjustment circuit configured downstream from a data alignment circuit.

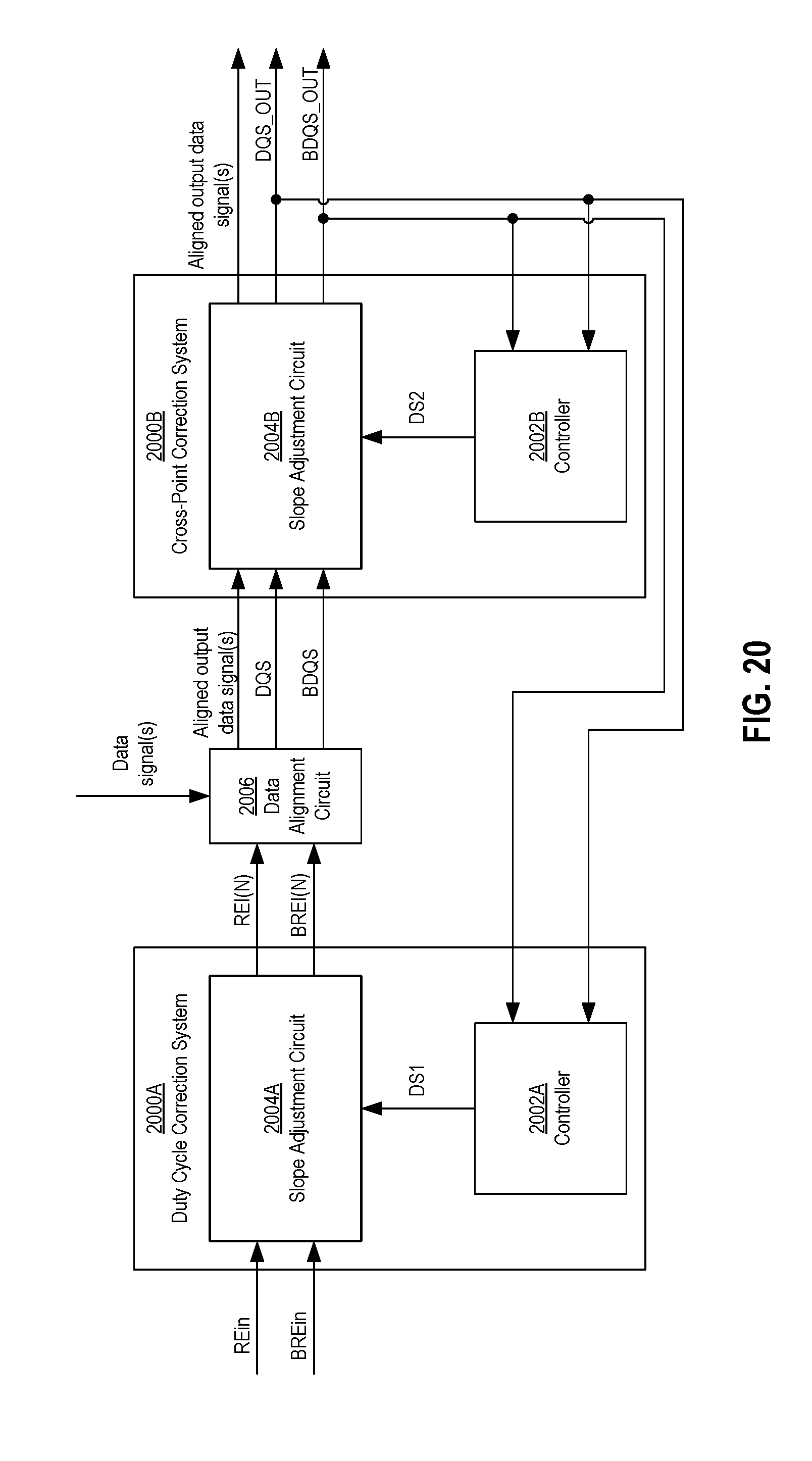

[0042] FIG. 20 is a block diagram of another example correction system with a slope adjustment circuit of a duty cycle correction system configured upstream from a data alignment circuit and a slope adjustment circuit of a cross-point correction system configured downstream from the data alignment circuit.

[0043] FIG. 21 is block diagram of another example correction system with slope adjustment circuits of both a duty cycle correction system and a cross-point correction system configured upstream from a data alignment circuit.

[0044] FIG. 22 is a block diagram of an example memory system configured with a correction system.

DETAILED DESCRIPTION

[0045] Overview

[0046] The following embodiments describe various apparatuses, devices, systems, circuits, and methods for performing duty cycle correction and/or cross-point correction. In one embodiment, a circuit includes a complementary signal path circuit and a control circuit. The complementary signal path circuit is configured to receive a pair of complementary input signals and generate a pair of complementary output signals. Additionally, the complementary signal path circuit includes: a plurality of pairs of circuit stages, where each pair of circuit stages is configured to generate a respective one of a plurality of pairs of complementary intermediate signals. The control circuit is configured to: measure a duty cycle distortion of a pair of complementary sample signals, and in response to the measurement, set drive strengths of the plurality of pairs of circuit stages.

[0047] In some embodiments, the control circuit is further configured to: in response to the measurement of the duty cycle distortion, select a target drive strength value from among a plurality of drive strength values, where the target drive strength value indicates a plurality of drive strength amounts; and set each pair of circuit stages of the plurality of pairs of circuit stages to a respective one of the plurality of drive strength amounts indicated by the drive strength value.

[0048] In some embodiments, the control circuit is further configured to set each pair of circuit stages of the plurality of pairs of circuit stages also to an initial drive strength amount, where each of the plurality of drive strength amounts indicated by the drive strength value is lower than the initial drive strength amount.

[0049] In some embodiments, the target drive strength value corresponds to a digital-to-analog converter (DAC) code indicating whether to activate or deactivate each of a plurality of branches of the set of circuit stages.

[0050] In some embodiments, branches of the circuit stages of the plurality of pairs of circuit stages have a binary-weighted configuration.

[0051] In some embodiments, a circuit stage of the plurality of pairs of circuit stages includes a plurality of drive strength sub-branches and a plurality of stability sub-branches, where a respective stability sub-branch is configured to bias a respective drive strength sub-branch in response to an associated drive strength sub-signal output at a level to deactivate the drive strength sub-branch.

[0052] In some embodiments, a circuit stage of the plurality of pairs of circuit stages includes a plurality of drive strength transistors, and a plurality of input transistors connected in parallel with each other. The plurality of drive strength transistors is configured to set a pull-up drive strength of a pull-up portion of the circuit stage or a push-down drive strength of a push-down portion of the circuit stage. The plurality of input transistors is configured to receive an input signal of the complementary input signals or an intermediate signal of the plurality of pairs of complementary intermediate signals. Also, a length of a first physical connection that connects together terminals of the plurality of drive strength transistors is shorter than a length of a second physical connection that connects together terminals of the plurality of drive strength transistors.

[0053] In some embodiments, the pair of complementary sample signals comprises the pair of complementary output signals.

[0054] In another embodiment, a system includes an output circuit, a measurement circuit, a search circuit, and a plurality of pairs of digital-to-analog (DAC) circuits. The output circuit is configured to generate a pair of output signals based on a plurality of intermediate signals. The measurement circuit is configured to a measure duty cycle mismatch of a plurality of complementary output signals during a predetermined number of iterations. The search circuit is configured to search through an array of digital-to-analog converter (DAC) codes in response to the duty cycle mismatch during the predetermined number of iterations. The plurality of pairs of DAC circuits is configured to: generate the plurality of intermediate signals, and during the predetermined number of iterations, adjust slopes of rising and falling transitions of the plurality of intermediate signals in response to the searching through the array of DAC codes.

[0055] In some embodiments, the measurement circuit is configured to measure the duty cycle mismatch of the pair of complementary output signals a predetermined number of times over the predetermined number of iterations, and the search circuit is configured to select a new one of a plurality of target DAC codes from the array of DAC codes in each of the predetermined number of iterations in response to a respective measurement of the duty cycle mismatch.

[0056] In some embodiments, the plurality of pairs of DAC circuits are configured to adjust the drive strengths in increasingly smaller amounts in response to each selection of the plurality of target DAC codes.

[0057] In some embodiments, each of the plurality of DAC codes includes a respective plurality of portions, where each portion indicates a drive strength amount for a corresponding pair of DAC circuits. Also, the plurality of DAC codes comprises a first set of DAC codes and a second set of DAC codes, where each of the DAC codes of the first set includes respective portions that all indicate the same drive strength amount, and where each of the DAC codes of the second set includes at least two respective portions that indicate different drive strength amounts. The search circuit is further configured to: select a first number of the plurality of target DAC codes from the first set of DAC codes in a first number of the predetermined number of iterations, and select a second number of the plurality of DAC codes from the second set of DAC codes in a second number of the predetermined number of iterations.

[0058] In some embodiments, the first number of the predetermined number of iterations is greater than the second number of the predetermined number of iterations.

[0059] In some embodiments, the search circuit is further configured to, in response to an initial measurement of the duty cycle mismatch, begin selecting target DAC codes from among the array of DAC codes in a selection direction corresponding to decreasing drive strength amounts.

[0060] In another embodiment, a circuit includes a slope adjustment circuit and a control circuit. The slope adjustment circuit includes a plurality of portions configured to generate a plurality of pairs of intermediate signals, where each portion of the plurality of portions includes a pull-up portion or a push-down portion. Also, the plurality of portions includes a first set of portions and a second set of portions. The first set of portions is configured to pull up and push down voltage levels of the plurality of pairs of intermediate signals with an initial drive strength amount. The second set of portions is configured to pull up and push down the voltage levels of the plurality of pairs of intermediate signals with associated reduced drive strength amounts relative to the initial drive strength amount. The control circuit is configured to measure an initial duty cycle distortion in a pair of complementary sample signals; and identify a configuration of the first set of portions and the second set of portions dependent on the initial duty cycle distortion.

[0061] In some embodiments, the control circuit is further configured to: in response to the initial the duty cycle distortion: identify a first sample signal of the pair of complementary sample signals to have an associated first duty cycle decreased, and identify a second sample of the pair of complementary sample signals to have an associated second duty cycle increased. Also, for the configuration, identify the second set as including selected pull-up portions and selected push-down portions of the plurality of pairs of circuit stages in response to the identification of the first sample signal to have the first duty cycle decreased and the identification of the second sample signal to have the second duty cycle increased. Also, the control circuit is configured to output drive strength signals to reduce drive strengths of the selected pull-up portions and the selected push-down portions.

[0062] In some embodiments, a plurality of pairs of circuit stages includes the plurality of portions, and the control circuit is configured to identify the selected pull-up portions and the selected push-down portions further based on a correspondence mapping that maps each circuit stage of the plurality of pairs of circuit stages to the first sample signal or to the second sample signal.

[0063] In some embodiments, the control circuit is further configured to: for the configuration, identify the first set as comprising unselected pull-up portions and unselected push-down portions of the plurality of pairs of circuit stages based on the identification of the first sample signal to have the first duty cycle decreased, the identification of the second sample signal to have the second duty cycle increased, and the correspondence mapping.

[0064] In some embodiments, each circuit stage of a pair of circuit stages of the plurality of pairs of circuit stages includes a respective pull-up portion and a respective push-down portion, and where for each pair of circuit stages, the control circuit is configured to identify a selected pull-up portion of a first circuit stage of a respective pair of circuit stages and selected push-down portion of a second circuit stage of the respective pair of circuit stages.

[0065] In some embodiments, the circuit includes a first path of circuit stages and a second path of circuit stages. For each pair of circuit stages of the plurality of pairs of circuit stages, a first circuit stage of a respective pair is configured in the first path and a second circuit stage of the respective pair is configured in the second path. For two consecutive circuit stages in the first path, one of the consecutive stages includes a selected pull-up portion and the other of the consecutive stages comprises a selected push-down portion.

[0066] In another embodiment, a circuit includes: means for receiving a pair of complementary input signals; means for generating a plurality of pairs of complementary intermediate signals according to drive strengths; means for measuring a duty cycle distortion of a pair of complementary sample signals; and means for setting the drive strengths in response to the means for measuring the duty cycle distortion.

[0067] Other embodiments are possible, and each of the embodiments can be used alone or together in combination. Accordingly, various embodiments will now be described with reference to the attached drawings.

Embodiments

[0068] The present description describes various embodiments of apparatuses, devices, systems, circuits, and methods for performing duty cycle correction and/or cross-point correction. The embodiments may include or utilize a slope adjustment circuit that is configured to adjust one or more slopes of complementary signals generated in a complementary signal path. In some examples, the slope adjustment circuit is configured to adjust slopes by adjusting drive strengths of branches it uses to generate the complementary signals.

[0069] A control circuit may be configured to measure duty cycle distortion or cross-point distortion in a pair of complementary sample signals of interest. Based on the measurement, the control circuit may set drive strengths in the slope adjustment circuit. The control circuit may measure the duty cycle distortion and/or cross-point distortion, and set the drive strengths over a plurality of iterations of a duty cycle correction process and/or a cross-point correction process. Over the course of the iterations, the control circuit may set and/or adjust the drive strengths within the slope adjustment circuit, which in turn, may have the effect of reducing duty cycle distortion and/or cross-point distortion in the signal or complementary signals of interest.

[0070] As used herein, two signals of a pair are complementary in that when one of the signals is at an associated high level the other is at an associated low level. The waveforms of two complementary signals are considered to inversely track each other in that when one signal performs a rising transition, the other signal performs a falling transition. In addition or alternatively, two signals that are complementary are 180-degrees out of phase with each other or have waveforms representative of two signals that are 180-degrees out of phase with each other.

[0071] Also, as used herein, a level of a signal at a given point in time is a magnitude value, such as a voltage magnitude value or a current magnitude value. In general, a high level and a low level are both magnitude values where the high level is higher in magnitude than the low level. A high level of a signal may be a single high level, a level that is within a set or range of high levels, a maximum high level or a minimum high level of a set or range of high levels, or an average high level of a set or range of high levels. Similarly, a low level of a signal may be a single low level, a level that is within a set or range of low levels, a maximum low level or a minimum low level of a set or range of low levels, or an average low level of a set or range of low levels.

[0072] In addition or alternatively, a given signal may transition between a high level and a low level according to a swing requirement that sets or identifies a minimum high level and a maximum low level. A signal that transitions according to the swing requirement may transition to a high level that is at or above the minimum high level of the swing requirement, and may transition to a low level that is at or below the maximum low level of the swing requirement.

[0073] In addition or alternatively, for a given voltage that is applied to a gate terminal of a p-channel metal-oxide-semiconductor field-effect transistor (PMOS transistor), the high level of the given voltage is a level that turns off or is capable of turning off the PMOS transistor, and the low level of the given voltage is a level that turns on or is capable of turning on the PMOS transistor. Similarly, for a given voltage that is applied to a gate terminal of an n-channel metal-oxide-semiconductor field-effect transistor (NMOS transistor), the high level of the given voltage is a level that turns on or is capable of turning on the NMOS transistor, and the low level of the given voltage is a level that turns off or is capable of turning off the NMOS transistor.

[0074] In addition, a signal may perform a rising transition when the signal transitions from its low level to its high level, and may perform a falling transition when the signal transitions from its high level to its low level. For a pair of complementary signals, when a first signal of the pair is performing a rising transition, a second signal of the pair is performing a falling transition, or in the event that the rising and falling transitions are not occurring concurrently, then the transition of the second signal that is occurring closest in time to the rising transition of the first signal is a falling transition. Similarly, when the first signal of the pair is performing a falling transition, the second signal is performing a rising transition, or in the event that the rising and falling transitions are not occurring concurrently, then the transition of the second signal that is occurring closest in time to the falling transition of the first signal is a rising transition. A rising edge of a signal's waveform denotes a rising transition, and a falling edge of a signal's waveform denotes a falling transition.

[0075] In addition, each signal may include pulses that are formed or defined by the rising and falling transitions of the signal. In particular example configurations, the pulses of a signal may correspond to the high level of a signal, in that each pulse is defined by a rising transition followed by a period where the signal is maintained at its high level, and then followed by a falling transition.

[0076] Additionally, a pair of complementary signals may perform their respective rising and falling transitions according to an associated frequency or rate. The pulses of the signals may occur according to the frequency of the signal. Each period or cycle of the signals may include a first portion and a second portion. During the first portion, a first signal of the pair is at the high level and a second signal of the pair is at the low level. During the second portion, the first signal is at the low level and the second signal is at the high level. In addition, each signal of the pair may have an associated duty cycle. As used herein, a duty cycle of a signal is the percentage or fraction of one period that the signal is at its high level. In addition or alternatively, the duty cycle of a signal is the ratio of a pulse width of a pulse in a single period of the signal to a total duration of the period.

[0077] Also, in at least some example configurations, a pair of complementary signals is a pair of clock signals. A clock signal has repetitive cycles. Within each period, the first portion occurs first in time and the second portion occurs second in time--i.e., after the first portion. After the second portion of one cycle occurs, the first portion of a next cycle occurs. As clock signals, the rising and falling edges of the signals may be used for timing purposes, such as for temporarily aligning data pulses of data signals and/or for indicating when to sample or otherwise identify levels of the data pulses, as described in further detail below.

[0078] FIG. 1 is a block diagram of an example of duty cycle correction circuit 100 may include a controller or control circuit 102 and a slope adjustment circuit (alternatively referred to as an adjustable drive strength circuit) 104. The duty cycle correction circuit 100 may further include, or alternatively be in communication with, a data alignment circuit 106. The data alignment circuit 106 may be configured to receive one or more data signals and output one or more aligned output data signals that correspond to the one or more data signals it receives. A data signal may include a series of data pulses, with each data pulse corresponding to a bit of a bit sequence. The level, such as a voltage level, of each data pulse, may correspond to and/or indicate a single bit logic value, such as a logic 1 value or a logic 0 value. Accordingly, each data pulse of the data signal may indicate whether a corresponding bit of the bit sequence represented by the data signal has a logic 1 value or a logic 0 value. Other configurations, such as those where the levels of the data pulses indicate multi-bit logic values, may be possible.

[0079] The slope adjustment circuit 104 may be configured to receive a pair of complementary input signals REin, BREin, and in response, generate one or more pairs of complementary intermediate signals REI, BREI, including a last or Nth pair of complementary intermediate signals REI(N), BREI(N). The data alignment circuit 106 may be configured to receive the Nth pair of intermediate REI(N), BREI(N), and in response, generate and output a pair of complementary output signals DQS, BDQS. In this context, the slope adjustment circuit 104 and the data alignment circuit 106 may form a complementary signal path circuit extending from the input of the slope adjustment circuit 104 to the output of the data alignment circuit 106. As a whole, the complementary signal path circuit is configured to receive the pair of complementary input signals REin, BREin, and generate the pair of complementary output signals DQS, BDQS in response to receipt of the pair of complementary input signals REin, BREin and according to a plurality of drive strengths of circuit stages of the complementary signal path circuit. In the complementary signal path, the adjustable drive strength circuit 104 generates the one or more pairs of complementary intermediate signals REI, BREI, including a last pair of intermediate signals REI(N), BREI(N), according to the drive strengths. The data alignment circuit 106 aligns the data signal(s) with the last intermediate signals REI(N), BREI(N), and outputs the output signals DQS, BDQS in response to the alignment process.

[0080] The data alignment circuit 106 may be configured to generate and output the output signals DQS, BDQS each with a respective target or predetermined duty cycle or a duty cycle that is within an acceptable range of duty cycles. The acceptable range may include and/or be centered around the predetermined duty cycle. For example, the acceptable range may be a set of duty cycles defined by the predetermined duty cycle plus-or-minus a predetermined error amount or plus-or-minus a certain percentage of the predetermined duty cycle. A duty cycle that is away from the predetermined duty cycle and/or outside of the acceptable range of duty cycles is referred to as a distorted duty cycle. Conversely, a duty cycle that is at the predetermined duty cycle or within the acceptable range of duty cycles is referred to as an undistorted duty cycle. For a given signal, an amount of duty cycle distortion of the signal is a difference between an actual duty cycle of the signal and the predetermined duty cycle.

[0081] Additionally, two complementary signals of a pair may have an amount of duty cycle mismatch, which is the difference between a duty cycle of one signal and the duty cycle of the other. A pair of complementary signals may have a target or predetermined amount of duty cycle mismatch. Where the duty cycles of the two complementary signals are the same, then the amount of duty cycle mismatch is zero. Similarly, where the predetermined duty cycles of the two complementary signals are the same, then the amount of predetermined duty cycle mismatch is zero. Two complementary signals of a pair have undistorted duty cycles when their duty cycle mismatch is at the predetermined amount of duty cycle mismatch, or within an acceptable range of duty cycle mismatch values. The acceptable range may be centered around the predetermined amount of duty cycle mismatch. For example, the acceptable range may be a set of duty cycles mismatch values defined by the predetermined duty cycle mismatch amount plus-or-minus a predetermined error amount or plus-or-minus a certain percentage of the predetermined duty cycle mismatch amount. A pair of complementary signals has undistorted duty cycles when their duty cycle mismatch is at the predetermined duty cycle mismatch amount or within the acceptable range of duty cycle mismatch. Alternatively, a pair of complementary signals has distorted duty cycles when their duty cycle mismatch deviates from the predetermined duty cycle mismatch amount or outside of the range of acceptable duty cycle mismatch values. For a given pair of complementary signals, an amount of duty cycle distortion is a difference between an actual duty cycle mismatch of the complementary signals and the predetermined duty cycle mismatch amount.

[0082] An amount of duty cycle mismatch may be an instantaneous value that indicates a difference of the instantaneous duty cycle of one signal and the instantaneous duty cycle of another signal for a single period or cycle of the signals. Alternatively, the duty cycle mismatch may be an average value that indicates a difference of an average duty cycle of one signal and the average duty cycle of another signal for a predetermined number of cycles or periods and/or over a plurality of periods or cycles occurring over a predetermined period of time.

[0083] Similarly, an amount of duty cycle distortion for a single signal may be an instantaneous value that indicates a difference of the instantaneous duty cycle of the signal for a single period or cycle and the predetermined duty cycle of the signal. Alternatively, the amount of duty cycle distortion for a single signal may be an average value that indicates a difference of the average duty cycle of the signal for a predetermined number of cycles or periods and/or over a plurality of periods or cycles occurring over a predetermined period of time. Likewise, the amount of duty cycle distortion for a pair of complementary signals may be an instantaneous value that indicates a difference of an instantaneous amount of duty cycle mismatch between the two signals and a predetermined duty cycle mismatch amount, or an average value that indicates a difference of an average amount of duty cycle mismatch between the two signals for a predetermined number of cycles or a plurality of periods or cycles occurring over a predetermined period and the predetermined duty cycle mismatch amount.

[0084] In the event that the pair of input signals REin, BREin or any of the pairs of intermediate signals REI, BREI have duty cycles that cause the pair of complementary output signals DQS, BDQS to have distorted duty cycles, the duty cycle correction circuit 100 may be configured to perform a duty cycle correction process that adjusts or modifies one or more characteristics of the complementary intermediate signals REI, BREI so that the pair of output signals DQS, BDQS are output with undistorted duty cycles. As described in further detail below, non-limiting example characteristics of the intermediate signals that are adjusted or modified may include the slopes of rising and/or falling transitions, cross-point, or duty cycle. In some example configurations, the predetermined duty cycle is 50%, although other predetermined duty cycle percentages may be possible.

[0085] FIG. 2A shows a timing diagram of the pair of complementary output signals DQS, BDQS having duty cycle distortion. FIG. 2B shows a timing diagram of the pair of complementary output signals DQS, BDQS having no duty cycle distortion. The waveforms in FIG. 2A represent example waveforms of output signals DQS, BDQS at the start of an example duty cycle correction process, and the waveforms in FIG. 2B represent example waveforms of the output signals DQS, BDQS at the end of an example duty cycle correction process.

[0086] FIGS. 2A and 2B show a cycle of the output signals DQS, BDQS occurring during a total time period T, which includes a first time period portion t1 followed by a second time period portion t2. During the first time period portion t1, a first output signal DQS of the pair DQS, BDQS may be at a low level, and a second output signal BDQS of the pair DQS, BDQS may be at a high level. During the second time period portion t2, the first output signal DQS may be at a high level and the second output signal BDQS may be at a low level during a second time period t2.

[0087] FIG. 2A shows duty cycle distortion between the output signals DQS, BDQS in that the first output signal DQS is at its high voltage level for a longer time period than it is at its low voltage level, and the second output signal BDQS is at its low voltage level for a longer time period than it is at its high voltage level, which corresponds to the first output signal DQS having a higher duty cycle than the second output signal BDQS, and which corresponds to the second time period portion t2 being longer than the first time period portion t1.

[0088] In contrast, FIG. 2B shows no duty cycle distortion or duty cycle distortion having been minimized or eliminated in that for both output signals DQS, BDQS, the durations at which they are at their respective high and low levels are the same, which corresponds to each output signal DQS, BDQS having the same 50% duty cycles, and which corresponds to the first time period portion t1 and the second time period portion t2 having the same durations.

[0089] Referring back to FIG. 1, the data alignment circuit 106 may be configured to receive the last pair of intermediate signals REI(N), BREI(N) from the slope adjustment circuit 104. The data alignment circuit 106 may be configured to perform an alignment process with the last pair of intermediate signals REI(N), BREI(N) and the data signal(s) it receives such that the output data signal(s) are aligned with the pair of output signals DQS, BDQS. By being aligned, the data pulses of the output data signal(s), such as the rising and falling transitions of the data pulses, occur at certain times relative to the rising and falling transitions or edges of the pair of complementary output signals DQS, BDQS. In some example configurations, the output data signal(s) may be aligned with the pair of complementary output signals DQS, BDQS in that their rising and falling transitions occur at the same time or about the same time that the complementary output signals DQS, BDQS perform their respective rising and falling transitions. In other example configurations, the output data signal(s) may be aligned with the pair of complementary output signals DQS, BDQS in that their rising and falling transitions occur at a certain, predetermined offset relative to the times that the pair of complementary output signals DQS, BDQS perform their respective rising and falling transitions. For example, the rising and falling transitions of the data signal(s) may occur at midpoints between consecutive rising and falling transitions of the pair of complementary output signals DQS, BDQS. In other words, the data signal(s) may be delayed or phase shifted 90-degrees relative to the pulses of the pair of complementary output signals DQS, BDQS. In addition or alternatively, the data signals and the complementary output signals DQS, BDQS may be aligned in accordance with a signaling or communication scheme, such as a single data rate (SDR) or a double data rate (DDR) communication scheme. The data alignment circuit 106 may include any of various types of circuits to perform the alignment process, including logic circuitry, combinational logic circuitry, flip-flops, and multiplexers, as non-limiting examples.

[0090] The controller 102 may be a feedback circuit that forms a feedback path for the slope adjustment circuit 104 and the data alignment circuit 106. As shown in FIG. 1, the controller 102 may be coupled to the output of the data alignment circuit 106 and be configured to receive the complementary output signals DQS, BDQS. In response to receipt of the complementary output signals DQS, BDQS, the controller 102 may be configured to perform a duty cycle correction process, which includes determining or measuring duty cycle distortion in the pair of output signals DQS, BDQS by measuring or detecting a duty cycle mismatch between the complementary output signals DQS, BDQS. Based on or in response to the measured or detected duty cycle distortion or mismatch, the controller 102 may be configured to set, control, and/or adjust drive strengths of stages of the slope adjustment circuit 104, as described in further detail below. The controller 102 may set, control, and/or adjust the drive strengths of the stages by determining a control code CC and outputting drive strength signals ENp, ENn, BENp, BENn, collectively referred to as drive strength signals DS, to the slope adjustment circuit 104 according to and/or at levels corresponding to the control code CC. In response to receipt of the drive strength signals DS, the slope adjustment circuit 104 may set, maintain, and/or adjust drive strengths of its internal circuit components used to generate the intermediate signals REI, BREI. As described in further detail below, the slope adjustment circuit 104, in response to adjusting its drive strength(s), may cause corresponding adjustments in the duty cycles, duty cycle mismatch, and/or duty cycle distortion of or between one or more of the intermediate signals REI, BREI and/or of or between the output signals DQS, BDQS.

[0091] For some example configurations, the slope adjustment circuit 104 is configured to include a plurality of paths, including a first or RE path and a second or BRE path. The RE path may be configured to receive the RE input signal REin, and in response, generate a plurality of RE intermediate signals REI. Collectively, the RE input signal REin and the RE intermediate signals REI may referred to as RE path signals. The BRE path may be configured to receive the BRE input signal BREin, and in response, generate a plurality of BRE intermediate signals BREI. The BRE input signal BREin and the BRE intermediate signals may be collectively referred to as BRE path signals. Additionally, each ith pair of intermediate complementary signals includes an associated RE intermediate signal REI(i) generated with the RE path and an associated BRE intermediate signal BREI(i) generated with the BRE path.

[0092] FIG. 3 shows a block diagram of an example configuration of the slope adjustment circuit 104. In the example configuration, the slope adjustment circuit 104 includes two circuit paths, including a first or RE path 302 and a second or BRE path 304. The RE signal path 302 is configured to receive the RE input signal REin, and in response, generate the RE intermediate signals REI. Similarly, the BRE signal path 304 is configured to receive the BRE input signal, and in response, generate the BRE intermediate signals BREI.

[0093] In addition, the RE path 302 and the BRE 304 path may each include a plurality or an N-number of circuit stages (or simply stages). The stages of the RE path 302 are referred to as RE stages 306, and the stages of the BRE path 304 are referred to as BRE stages 308. Additionally, in the example configuration shown in FIG. 3, the RE path 302 and the BRE path 304 each include four stages (i.e., N=4). Accordingly, the Nth pair of intermediate signals is shown in FIG. 3 as a fourth pair of intermediate signals REI(4), BREI(4). In other example configurations, numbers other than four may be possible, and in general, the number of stages in each of the RE path 302 and the BRE path 304 may be two or more. Hereafter, for clarity, the terms "last pair of intermediate signals," "Nth pair of intermediate signals," "output pair of intermediate signals" and "fourth pair of intermediate signals" are used interchangeably to refer to the pair of complementary signals output from the slope adjustment circuit 104 (or specifically the RE path 302 and the BRE path 304) to the data alignment circuit 106.

[0094] In the example configuration shown in FIG. 3, the RE stages 306 of the RE path 302 and the BRE stages 308 of the BRE path 304 are each configured as a chain of stages. Herein, the terms "path" and "chain" are interchangeably. In a given path, each of the stages has a relative or respective position with respect to the other stages in the given path, starting with a first stage that receives the input signal to the path and a last stage that outputs the output signal of the path. An input of the first stage that receives the input signal to the path may be considered an input of the path as whole, and an output of the last stage that outputs the output signal of the path may be considered an output of the path as a whole.

[0095] Also, herein, the stages in a given path are consecutively numbered--e.g., first stage, second stage, third stage, etc.--corresponding to their relative positions in a respective path. In general, the lower a stage is numbered, the closer it is positioned to the input of the path, and the higher a stage is numbered, the closer it is positioned to the output of the path. Also, the stages are numbered such that an ith stage in a given path indicates that the path includes an (i-1)-number of stages between the ith stage and the input of the path. For a given ith stage, stages that are closer to the input of a path--i.e., the (i-1)th stage and lower--are referred to as prior or upstream stages of the ith stage. Likewise, for a given ith stage, stages that are closer to the output of the path--i.e., the (i+1)th stage and higher--are referred to as subsequent or downstream stages of the ith stage. The (i-1)th stage is referred to as the immediately prior stage of the ith stage, and the (i+1)th stage is referred to as the next or immediately subsequent stage of the ith stage.

[0096] Additionally, an ith stage in a path indicates that it is the ith stage in the path to generate an intermediate signal based on the input signal to the path. Otherwise stated, for a given ith stage in a path, an (i-1)-number of stages generated and outputted respective intermediate signals based on the input signal to the path before the ith stage generated and outputted its respective ith intermediate signal. Further, except for the first stage of the given path, each ith stage has an input coupled to an output of a prior (i-1)th stage, and is configured to receive an immediately prior, (i-1)th intermediate signal of the immediately prior (i-1)th stage as its input signal, and generate an ith intermediate signal in response to receipt of the immediately prior (i-1)th intermediate signal. Also, except for the last or Nth stage of a given chain, each ith stage has an output coupled to an input of a next (i+1)th stage, and is configured to output an ith intermediate signal to the input of the next or immediately subsequent (i+1)th stage.

[0097] Accordingly, with respect to the RE path 302, a first RE stage 306(1) is configured to receive the RE input signal REin; generate a first RE intermediate signal REI(1) in response to receipt of the RE input signal REin; and output the first RE intermediate signal REI(1) to a next, second RE stage 306(2). The second RE stage 306(2) is configured to receive the first RE intermediate signal REI(1) from the first RE stage 306(1); generate a second RE intermediate signal REI(2) in response to receipt of the first RE intermediate signal REI(1); and output the second RE intermediate signal REI(2) to a third RE stage 306(3). The third RE stage 306(3) is configured to receive the second RE intermediate signal REI(2) from the second RE stage 306(2); generate a third RE intermediate signal REI(3) in response to receipt of the second RE intermediate signal REI(2); and output the third RE intermediate signal REI(3) to a fourth RE stage 306(4). The fourth RE stage 306(4) is configured to receive the third RE intermediate signal REI(3) from the third RE stage 306(3); generate a fourth RE intermediate signal REI(4) in response to receipt of the third RE intermediate signal REI(3); and output the fourth RE intermediate signal REI(4) to the data alignment circuit 106.

[0098] Similarly, with respect to the BRE path 304, a first BRE stage 308(1) is configured to receive the BRE input signal BREin; generate a first BRE intermediate signal BREI(1) in response to receipt of the BRE input signal BREin; and output the first BRE intermediate signal BREI(1) to a next, second BRE stage 308(2). The second BRE stage 308(2) is configured to receive the first BRE intermediate signal BREI(1) from the first BRE stage 308(1); generate a second BRE intermediate signal BREI(2) in response to receipt of the first BRE intermediate signal BREI(1); and output the second BRE intermediate signal BREI(2) to a third BRE stage 308(3). The third BRE stage 308(3) is configured to receive the second BRE intermediate signal BREI(2) from the second BRE stage 308(2); generate a third BRE intermediate signal BREI(3) in response to receipt of the second BRE intermediate signal BREI(2); and output the third BRE intermediate signal BREI(3) to a fourth BRE stage 308(4). The fourth RE stage 308(4) is configured to receive the third BRE intermediate signal BREI(3) from the third BRE stage 308(3); generate a fourth BRE intermediate signal BREI(4) in response to receipt of the third BRE intermediate signal BREI(3); and output the fourth BRE intermediate signal BREI(4) to the data alignment circuit 106.

[0099] Also, the stages 306, 308 in the RE and BRE paths 302, 304, respectively, are numbered such that a given ith RE stage 306(i) in the RE path 302 and a given ith BRE stage 308(i) in the BRE path 304 have the same relative position within their respective paths 302, 304. Accordingly, a given ith RE stage 306(i) and a given ith BRE stage 308(i) as an ith pair of circuits stages (or simply stages) 306(i), 308(i), and in combination, the ith pair of RE and BRE circuit stages 306(i), 308(i) may be configured to generate and output an ith pair of intermediate signals REI(i), BREI(i). In this context, the RE path 302 and the BRE path 304, in combination, include a plurality of pairs of circuit stages, where each of the pairs of circuit stages is configured to generate a respective one of a plurality of pairs of complementary intermediate signals.

[0100] Also, for some example configurations, each RE stage 306 of the RE path 302 and each BRE stage 308 of the BRE path 304 may be configured as an inverter circuit that is configured to invert its input signal to generate its associated intermediate signal. In other words, each stage may be configured to generate and output its associated intermediate signal as an inverted version of its input signal. In general, two signals generated by an inverter, where a second signal generated with the inverter is an inverted version of a first signal received with the inverter, have the same or similar waveforms as those of a pair of complementary signals. The inverter responds to the first signal at an associated high level by generating and outputting the second signal at an associated low level, and responds to the first signal at an associated low level by generating and outputting the second signal at an associated high level. Likewise, the inverter generates and outputs the second signal to have transitions that inversely track the transitions of the first signal. Accordingly, in response to receipt of the first signal performing a rising transition, the inverter generates the second signal with a falling transition. In addition, in response to receipt of the first signal performing a falling transition, the inverter generates the second signal with a rising transition. Accordingly, the second signal generated by the inverter is 180-degrees out of phase with the first signal, plus any time delay associated with the inverter.

[0101] For other example configurations, at least some of the stages are non-inverter circuits in that they generate their respective intermediate signals to directly track their respective input signals. Accordingly, in response to a receipt of a first signal at an associated high level, a non-inverter generates and outputs a second signal at an associated high level, and in response to receipt of the first signal at an associated low level, the non-inverter generates and outputs the second signal at an associated high level. Likewise, the non-inverter generates and outputs the second signal to have transitions that directly track the transitions of the first signal. Accordingly, in response to receipt of the first signal performing a rising transition, the non-inverter generates the second signal with a rising transition. In addition, in response to receipt of the first signal performing a falling transition, the non-inverter generates the second signal with a falling transition. Accordingly, the second signal generated by the non-inverter is time-shifted relative to the first signal by a time delay associated with the non-inverter, but otherwise has a phase that matches the phase of the first signal.

[0102] In addition, each RE path signal and each BRE path signal may have an associated correspondence to one of the output signals DQS, BDQS. As described in further detail below, the controller 102 may be configured to control the adjustment of the duty cycles of the RE and BRE intermediate signals REI, BREI to reduce the duty cycle distortion in the output signals DQS, BDQS based on the correspondences between the output signals DQS, BDQS and the RE and BRE path signals. The correspondences may allow the controller 102 to control the duty cycle adjustments of the RE and BRE intermediate signals REI, BREI so that the higher duty cycle of the output signals DQS, BDQS is decreased, the lower duty cycle of the output signals DQS, BDQS is increased, and duty cycle distortion is reduced. For example, in the event that the first output signal DQS has a higher duty cycle than the second output signal BDQS, the correspondences may allow the controller 102 to determine how to control the adjustment of the duty cycles of the RE and BRE intermediate signals REI, BREI so that the duty cycle of the first output signal DQS is decreased and the duty cycle of the second output signal BDQS is increased to reduce their duty cycle distortion. Similarly, in the event that the first output signal DQS has a lower duty cycle than the second output signal BDQS, the correspondences may allow the controller 102 to determine how to control the adjustment of the duty cycles of the RE and BRE intermediate signals REI, BREI so that the duty cycle of the first output signal DQS is increased and the duty cycle of the second output signal BDQS is decreased to reduce their duty cycle distortion.

[0103] The correspondences between the output signals DQS, BDQS and the RE path and BRE path signals may be based on relative duty cycle levels between given pairs of complementary signals. That is, for a given pair of complementary signals that has duty cycle distortion, a duty cycle of one of the signals of the pair may be higher than the duty cycle of the other signal of the pair. Between two given pairs of complementary signals received by or generated with the complementary signal path, the signal of a first pair having the higher duty cycle of the first pair may correspond to the signal of a second pair that has the higher duty cycle of the second pair, and the signal of the first pair having the lower duty cycle of the first pair corresponds to the signal of the second pair that has the lower duty cycle of the second pair.

[0104] For simplicity herein as a default correspondence, the RE input signal REin is considered to correspond to the first output signal DQS and the BRE input signal BREin is considered to correspond to the second output signal BDQS. Accordingly, in the event that RE input signal REin has a higher duty cycle than the BRE input signal BREin, absent duty cycle correction, the first output signal DQS would have correspondingly larger duty cycle than the second output signal BDQS. Likewise, in the event that RE input signal REin has a lower duty cycle than the BRE input signal BREin, absent duty cycle correction, the first output signal DQS would have correspondingly lower duty cycle than the second output signal BDQS. Thereafter, in the slope adjustment circuit 104, the RE and BRE intermediate signals REI, BREI may correspond to output signals DQS, BDQS based on whether the stages generating the RE and BRE intermediate signals REI, BREI are configured as inverter circuits or non-inverter circuits, and whether the prior signals received by the stages correspond to the first output signal DQS or the second output signal BDQS.

[0105] In further detail, for example configurations where a given jth stage is configured as an inverter, and where the jth stage receives a given RE or BRE path signal and generates an jth intermediate signal in response to receipt of the given RE or BRE path signal, the jth intermediate signal that the jth stage generates may correspond to the other of the output signals DQS, BDQS compared to the output signal to which the given RE or BRE path signal corresponds. For example, suppose the first RE stage 306(1) and the first BRE stage 308(1) are both configured as inverters. Given that the RE input signal REin corresponds to the first output signal DQS, the first RE intermediate signal REI(1) that the first RE stage 306(1) generates corresponds to the second output signal BDQS. Likewise, given that the BRE input signal BREin corresponds to the second output signal BDQS, the first BRE intermediate signal BREI(1) that the first BRE stage 308(1) generates corresponds to the first output signal DQS. Such a correspondence maintains the direct relationship between relative duty cycle levels of the pairs of complementary signals. For example, suppose the duty cycle of the first output signal DQS is higher than the duty cycle of the second output signal BDQS. Based on the default correspondence, the RE input signal REin would have a higher duty cycle than the duty cycle of the BRE input signal BREin. Then, based on the inverter configuration of the first RE and BRE stages 306(1), 308(1), the first RE and BRE stage 306(1), 308(1) would generate the first pair of intermediate signals REI(1), BREI(1) such that the first BRE intermediate signal BREI(1) would have the higher duty cycle, thus corresponding to the first output signal DQS, and the first RE intermediate signal REI(1) would have the lower duty cycle, thus corresponding to the second output signal BDQS.

[0106] In addition, for example configurations where a given jth stage is configured as a non-inverter, and where the jth stage receives a given RE or BRE path signal and generates a jth intermediate signal in response to receipt of the given RE or BRE path signal, the jth intermediate signal that the jth stage generates may correspond to the same output signal as the output signal to which the given RE or BRE path signal corresponds. For example, suppose the first RE stage 306(1) and the first BRE stage 308(1) are both configured as non-inverters. Given that the RE input signal REin corresponds to the first output signal DQS, the first RE intermediate signal REI(1) that the first RE stage 306(1) generates also corresponds to the first output signal DQS. Likewise, given that the BRE input signal BREin corresponds to the second output signal BDQS, the first BRE intermediate signal BREI(1) that the first BRE stage 308(1) generates also corresponds to the second output signal BDQS. Such a correspondence maintains the direct relationship between relative duty cycle levels of the pairs of complementary signals. For example, suppose the duty cycle of the first output signal DQS is higher than the duty cycle of the second output signal BDQS. Based on the default correspondence, the RE input signal REin would have a higher duty cycle than the duty cycle of the BRE input signal BREin. Then, based on the non-inverter configuration of the first RE and BRE stages 306(1), 308(1), the first RE and BRE stage 306(1), 308(1) would generate the first pair of intermediate signals REI(1), BREI(1) such that the first RE intermediate signal REI(1) would have the higher duty cycle, thus corresponding to the first output signal DQS, and the first BRE intermediate signal BREI(1) would have the lower duty cycle, thus corresponding to the second output signal BDQS.

[0107] In addition, for some example configurations, at least some of the RE stages 306 and/or the BRE stages 308 may be configured as push-pull circuits to generate their respective intermediate signals. In general, a push-pull circuit is a circuit that includes a pull-up portion configured to pull up a level (e.g., a voltage level) of its output signal to an associated high level and a push-down portion configured to push down the level of its output signal to an associated low level. The push-pull circuit may pull up the level of its output signal to generate the rising transitions of the output signal and may push down the level of its output signal to generate the falling transitions of the output signal. Push-pull circuits may be inverter circuits or non-inverter circuits. As an inverter circuit, a push-pull circuit may pull up the level of its output signal in response to a falling transition of its input signal, and may push down the level of its output signal in response to a rising transition of its input signal. As a non-inverter circuit, a push-pull circuit may pull up the level of its output signal in response to a rising transition of its input signal, and may push down the level of its output signal in response to a falling transition of its input signal.

[0108] In addition, a push-pull circuit may pull up the level of its output signal with an associated pull-up drive strength, and may push down the level of its output signal with an associated push-down drive strength. As used herein, a pull-up drive strength is a measure of an ability or a strength that a push-pull circuit has to pull up a level, such as a voltage level, of its output signal to an associated high level. Similarly, a push-down drive strength is a measure of an ability or a strength that a push-pull circuit has to push down a level, such as a voltage level, of its output signal to an associated low level.

[0109] For some example configurations, drive strength may correspond to current draw. In particular, a push-pull circuit may be configured to generate an associated pull-up current to pull up a level of its output signal to an associated high voltage level. The larger the level or amount of the pull-up current the push-pull circuit can generate, the greater the pull-up drive strength of the push-pull circuit. Alternatively, the smaller the level or amount of the pull-up current the push-pull circuit can generate, the smaller the pull-up drive strength of the push-pull circuit. Similarly, a push-pull circuit may be configured to generate an associated push-down current to push down a level of its output signal to an associated low voltage level. The larger the level or amount of the push-down current the push-pull circuit can generate the greater the push-down drive strength of the push-pull circuit. Alternatively, the smaller the level or amount of the push-down current the push-pull circuit can generate, the smaller the push-down drive strength of the push-pull circuit.

[0110] In general, the stronger the pull-up drive strength, the faster the rate at which the push-pull circuit can pull up the level of its output signal, and the weaker the pull-up drive strength, the slower the rate at which the push-pull circuit can pull up the level of its output signal. Likewise, the stronger the push-down drive strength, the faster the rate at which the push-pull circuit can push down the level of its output signal, and the weaker the push-down drive strength, the slower the rate at which the push-pull circuit can push down the level of its output signal.

[0111] Also, when the push-pull circuit pulls up the level of the output signal to generate a rising transition, the rising transition may have an associated slope, referred to as a rising slope. Accordingly, the push-pull circuit may generate the rising transition with an associated rising slope. Likewise, when the push-pull circuit pulls down the level of the output signal to generate a falling transition, the falling transition may have an associated slope. Accordingly, the push-pull circuit may generate the falling transition with an associated slope, referred to as a falling slope. From a graphical perspective, if a magnitude waveform of the output signal is plotted as a function of time, the slope of a given transition (rising or falling) is the slope of the magnitude as a function of time over a period of time during which the output signal is performing the transition.

[0112] Mathematically, slope is a measure of a steepness of a line. The steeper a slope, the higher the magnitude value of the slope, and the more gradual the slope, the lower the magnitude value of the slope. Also, an increasing slope has a positive polarity and a decreasing slope has a negative polarity. With respect to the rising and falling transitions of signals, a rising slope is an increasing slope and a falling slope is a decreasing slope.

[0113] Also, slopes may have an associated direction corresponding to whether it is an increasing slope or a decreasing slope. A rising (increasing) transition has a rising direction in that over the rising transition, the magnitude of the signal (or the signal's waveform) increases. A falling (decreasing) transition has a falling direction in that over the falling transition, the magnitude of the signal (or the signal's waveform) decreases. The rising direction and the falling direction are opposite directions to each other.

[0114] With respect to a push-pull circuit generating an output signal, the greater or stronger the pull-up drive strength of the push-pull circuit, the faster the push-pull circuit pulls up the voltage level to generate a rising transition of the output voltage, and the greater or steeper the slope of the rising transition. Alternatively, the lesser or weaker the pull-up drive strength of the push-pull circuit, the slower the push-pull circuit pulls up the voltage level to generate a rising transition of the output voltage, and the smaller or more gradual the slope of the rising transition. Similarly, the greater or stronger the push-down drive strength of the push-pull circuit, the faster the push-pull circuit pushes down the voltage level to generate a falling transition of the output voltage, and the greater or steeper the slope of the falling transition. Alternatively, the lesser or weaker the push-down drive strength of the push-pull circuit, the slower the push-pull circuit pushes down the voltage level to generate a falling transition of the output voltage, and the smaller or more gradual the slope of the falling transition.

[0115] A given ith stage of the RE path 302 or the BRE path 304 may be configured to pull up and push down the voltage level of the ith intermediate signal that the ith stage generates. In addition, the given ith stage may be configured to pull up the voltage level of the ith intermediate signal with an associated pull-up drive strength, and push down the voltage level of the ith intermediate signal with an associated push-down drive strength. At a given point in time, the associated pull-up and push-down drive strengths for the given ith stage may the same or different from each other. Also, the pull-up drive strength or push-down drive strength for the given ith stage may be the same or different at different points in time. For example, the ith stage may generate rising transitions of the ith intermediate signal with the same or different pull-up drive strengths at different points in time, and/or may generate falling transitions of the ith intermediate signal with the same different push-down drive strengths at different points in time.

[0116] Also, at a given point in time, different RE stages 306 of the RE path 302 may have the same or different pull-up drive strengths and/or may have the same or different push-down drive strengths. Similarly, at a given point in time, different BRE stages 308 of the BRE path 304 may have the same or different pull-up drive strengths and/or may have the same or different push-down drive strengths.

[0117] FIG. 4 shows a block diagram of example configurations of a jth RE stage 306(j) of the RE path 302 and a jth BRE stage 308(j) of the BRE path 304. The jth RE stage 306(j) and the jth BRE stage 308(j) shown in FIG. 4 may be representative of push-pull circuit configurations of any or all of the RE stages 306 and BRE stages 308, respectively, shown in FIG. 3.

[0118] As shown in FIG. 4, the jth RE stage 306(j) is configured to receive an input signal IN_REj, and generate a jth RE intermediate signal REI(j) at a jth RE output node OUT_R(j) in response to the input signal IN_REj. Similarly, the jth BRE stage 308(j) is configured to receive an input signal IN_BREj, and generate a jth BRE intermediate signal BREI(j) at a jth BRE output node OUT_B(j) in response to the input signal IN_BREj

[0119] The jth RE stage 306(j) may include a RE pull-up portion 402 and a RE push-down portion 404. The RE pull-up portion 402 is configured to pull-up the voltage level of the jth RE intermediate signal REI(j) to an associated high voltage level VDD and/or maintain the voltage level of the jth RE intermediate signal REI(j) at the associated high voltage level VDD. The RE push-down portion 404 is configured to push-down the voltage level of the jth RE intermediate signal REI(j) to an associated low voltage level VSS and/or maintain the voltage level of the jth RE intermediate signal REI(j) at the associated low voltage level VSS.