Semiconductor Device And Method Of Manufacturing The Same

Kim; Sung-Min ; et al.

U.S. patent application number 16/162428 was filed with the patent office on 2019-02-14 for semiconductor device and method of manufacturing the same. The applicant listed for this patent is Samsung Electronics Co., Ltd.. Invention is credited to Dong-Ho Cha, Ji-Su Kang, Sung-Min Kim, Yu-Ri Lee, Jae-Hyun Park, Byung-Chan Ryu.

| Application Number | 20190051566 16/162428 |

| Document ID | / |

| Family ID | 57630395 |

| Filed Date | 2019-02-14 |

View All Diagrams

| United States Patent Application | 20190051566 |

| Kind Code | A1 |

| Kim; Sung-Min ; et al. | February 14, 2019 |

SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

Abstract

A semiconductor device includes a first fin-type pattern and a second fin-type pattern which protrude upwardly from an upper surface of a field insulating film and extend in a first direction. A gate structure intersects the first fin-type pattern and the second fin-type pattern. A first epitaxial layer is on the first fin-type pattern on at least one side of the gate structure, and a second epitaxial layer is on the second fin-type pattern on at least one side of the gate structure. A metal contact covers outer circumferential surfaces of the first epitaxial layer and the second epitaxial layer. The first epitaxial layer contacts the second epitaxial layer.

| Inventors: | Kim; Sung-Min; (Incheon, KR) ; Kang; Ji-Su; (Seoul, KR) ; Ryu; Byung-Chan; (Seongnam-si, KR) ; Park; Jae-Hyun; (Osan-si, KR) ; Lee; Yu-Ri; (Suwon-si, KR) ; Cha; Dong-Ho; (Seongnam-si, KR) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 57630395 | ||||||||||

| Appl. No.: | 16/162428 | ||||||||||

| Filed: | October 17, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15211200 | Jul 15, 2016 | 10147650 | ||

| 16162428 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 29/161 20130101; H01L 29/41791 20130101; H01L 29/165 20130101; H01L 29/665 20130101; H01L 2029/7858 20130101; H01L 23/485 20130101; H01L 29/0847 20130101; H01L 21/823821 20130101; H01L 21/823871 20130101; H01L 29/1608 20130101; H01L 29/7848 20130101; H01L 21/823814 20130101; H01L 27/0924 20130101; H01L 21/76897 20130101 |

| International Class: | H01L 21/8238 20060101 H01L021/8238; H01L 29/16 20060101 H01L029/16; H01L 29/78 20060101 H01L029/78; H01L 29/165 20060101 H01L029/165; H01L 29/161 20060101 H01L029/161; H01L 29/08 20060101 H01L029/08; H01L 27/092 20060101 H01L027/092 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Jul 16, 2015 | KR | 10-2015-0100843 |

Claims

1. A semiconductor device comprising: a first fin-type pattern and a second fin-type pattern which protrude upwardly from an upper surface of a field insulating film, the first and second fin-type patterns each extending in a first direction; a gate structure that intersects the first fin-type pattern and the second fin-type pattern; a first epitaxial layer on the first fin-type pattern on at least one side of the gate structure; a second epitaxial layer on the second fin-type pattern on at least one side of the gate structure; and a metal contact which covers outer circumferential surfaces of the first epitaxial layer and the second epitaxial layer, wherein the first epitaxial layer directly contacts the second epitaxial layer.

2. The semiconductor device of claim 1, wherein the metal contact comprises a first portion which directly contacts side walls of the gate structure, and a second portion which is spaced apart from the side walls of the gate structure on top of the first portion.

3. The semiconductor device of claim 2, wherein at an interface between the first portion and the second portion, a width of the first portion is greater than a width of the second portion.

4. (canceled)

5. The semiconductor device of claim 2, wherein a part of the second portion is located below an upper surface of the gate structure.

6. The semiconductor device of claim 1, further comprising: a protruding space between the field insulating film and the first and second epitaxial layers, the protruding space comprising an insulating material, a metal material or an air gap.

7. (canceled)

8. The semiconductor device of claim 1, further comprising: a third epitaxial layer which completely covers the outer circumferential surfaces of the first and second the epitaxial layers, wherein the first epitaxial layer and the second epitaxial layer include the same material, and the third epitaxial layer comprises a material different from the first and second epitaxial layers.

9. A semiconductor device comprising: a first fin-type pattern extending in a first direction on a substrate; a gate structure which intersects the first fin-type pattern; a first epitaxial layer on the first fin-type pattern on at least one side of the gate structure; and a metal contact which includes a first portion that directly contacts side walls of the gate structure, and a second portion that is spaced apart from the side walls of the gate structure on top of the first portion, wherein the first portion directly contacts the first epitaxial layer, a width of the first portion is greater than a width of the second portion at an interface between the first portion and the second portion, and the first and second portions are materially of the same composition.

10. (canceled)

11. The semiconductor device of claim 9, further comprising: an interlayer insulating film which covers the gate structure and the first epitaxial layer, wherein the interlayer insulating film does not contact the first epitaxial layer.

12. (canceled)

13. The semiconductor device of claim 11, further comprising: a barrier metal which is between the metal contact and the first epitaxial layer and between the metal contact and the interlayer insulating film.

14. The semiconductor device of claim 13, wherein the barrier metal comprises a first part which is in contact with the first epitaxial layer, and a second part which is in contact with the interlayer insulating film, and the first part and the second part have compositions different from each other.

15. The semiconductor device of claim 9, wherein the metal contact completely surrounds the outer circumferential surface of the first epitaxial layer.

16. (canceled)

17. The semiconductor device of claim 15, wherein the first epitaxial layer comprises Si and/or SiC, and the semiconductor device is an NMOS transistor.

18. The semiconductor device of claim 9, further comprising: a second epitaxial layer which covers a first area of the first epitaxial layer, wherein the metal contact covers an upper surface of the second epitaxial layer.

19.-21. (canceled)

22. The semiconductor device of claim 9, further comprising: a second epitaxial layer which completely covers an outer circumferential surface of the first epitaxial layer, wherein the second epitaxial layer comprises a material different from the first epitaxial layer.

23.-24. (canceled)

25. The semiconductor device of claim 9, wherein, in the metal contact, the first portion and the second portion are integrally formed.

26. A semiconductor device comprising: a first fin-type pattern which protrudes upwardly from an upper surface of a field insulating film; a first epitaxial layer on the first fin-type pattern; an interlayer insulating film on the field insulating film that covers the first fin-type pattern and the first epitaxial layer; and a metal contact which includes a first portion and a second portion on the first portion, wherein the first portion extends along an outer circumferential surface of the first epitaxial layer within the interlayer insulating film, and directly contacts the field insulating film, an upper surface of the second portion being coplanar with an upper surface of the interlayer insulating film, and the first and second portions are materially of the same composition.

27. The semiconductor device of claim 26, further comprising: a barrier metal between the metal contact and the first epitaxial layer, and between the metal contact and the interlayer insulating film.

28. The semiconductor device of claim 27, wherein the barrier metal comprises a first area which is in contact with the first epitaxial layer, and a second area which is in contact with the interlayer insulating film, and the first area and the second area have compositions different from each other.

29. The semiconductor device of claim 26, further comprising: a second epitaxial layer which completely covers the outer circumferential surface of the first epitaxial layer, wherein the second epitaxial layer comprises a material different from the first epitaxial layer.

30. The semiconductor device of claim 29, wherein the metal contact completely covers the outer circumferential surface of the second epitaxial layer.

31.-39. (canceled)

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims priority under 35 U.S.C. .sctn. 120 as a continuation of U.S. patent application Ser. No. 15/211,200, filed Jul. 15, 2016, which in turn claims priority under 35 U.S.C. .sctn. 119 from Korean Patent Application No. 10-2015-0100843, filed on Jul. 16, 2015 in the Korean Intellectual Property Office. The entire content of each of the above applications is incorporated herein by reference.

BACKGROUND

[0002] One scaling technique for improving the density of a semiconductor device is the use of a multi-gate transistor in which a semiconductor fin is formed on a substrate and a gate is formed on a surface of the semiconductor fin. Since such a multi-gate transistor uses a three-dimensional channel, it is easy to perform scaling. Moreover, even if a gate length of the multi-gate transistor is not increased, the current control capability may be improved. Additionally, it is also possible to effectively suppress a short channel effect (SCE) in which the potential of the channel area is influenced by a drain voltage.

SUMMARY

[0003] An aspect of the inventive concepts provides a semiconductor device which may reduce the contact resistance and the contact size by forming the metal contact to wrap around source/drain areas.

[0004] Another aspect of the inventive concepts provides a method of manufacturing a semiconductor device capable of reducing the contact resistance and the contact size by forming a metal contact to wrap around the source/drain areas using a dummy epitaxial layer, without a silicide manufacturing process.

[0005] According to an aspect of the inventive concepts, there is provided a semiconductor device including a first fin-type pattern and a second fin-type pattern which protrude upwardly from an upper surface of a field insulating film, the first and second fin-type patterns each extending in a first direction, a gate structure that intersects the first fin-type pattern and the second fin-type pattern, a first epitaxial layer on the first fin-type pattern on at least one side of the gate structure, a second epitaxial layer on the second fin-type pattern on at least one side of the gate structure, and a metal contact which covers outer circumferential surfaces of the first epitaxial layer and the second epitaxial layer, wherein the first epitaxial layer contacts the second epitaxial layer.

[0006] In some embodiments, the metal contact comprises a first portion which contacts side walls of the gate structure, and a second portion which is spaced apart from the side walls of the gate structure on top of the first portion.

[0007] In some embodiments, at an interface between the first portion and the second portion, a width of the first portion is greater than a width of the second portion.

[0008] In some embodiments, the gate structure comprises a gate insulating film, a gate electrode on the gate insulating film, and a spacer on at least one side of the gate electrode, wherein the first portion is in contact with the spacer.

[0009] In some embodiments, a part of the second portion is located below an upper surface of the gate structure.

[0010] In some embodiments, a protruding space is provided between the field insulating film and the first and second epitaxial layers.

[0011] In some embodiments, the protruding space comprises an insulating material, a metal material or an air gap.

[0012] In some embodiments, an interlayer insulating film may be provided which covers the gate structure and the first and second epitaxial layers. The interlayer insulating film may contact a first area of the first and second epitaxial layers, and the metal contact may cover an outer surface of a second area of the first area of the first and second epitaxial layers.

[0013] In some embodiments, a third epitaxial layer may be provided which completely covers the outer circumferential surfaces of the first and second epitaxial layers, wherein the first and second epitaxial layers include the same material, and the third epitaxial layer comprises a material different from the first and second epitaxial layers.

[0014] According to another aspect of the inventive concepts, there is provided a semiconductor device including a substrate which includes a first area and a second area, a first fin-type pattern extending in a first direction on the first area, a second fin-type pattern extending in a second direction on the second area, a first gate structure which contacts the first fin-type pattern, the first gate structure extending in a third direction that intersects the first direction, a second gate structure which contacts the second fin-type pattern, the second gate structure extending in a fourth direction that intersects the second direction, a first epitaxial layer on the first fin-type pattern on at least one side of the first gate structure, a second epitaxial layer on the second fin-type pattern on at least one side of the second gate structure, a first metal contact which is on the first epitaxial layer and includes a first metal material, and a second metal contact which is on the second epitaxial layer and includes the first metal material, wherein the first metal contact completely surrounds an outer circumferential surface of the first epitaxial layer, and the second metal contact contacts only a part of an upper surface of the second epitaxial layer.

[0015] In some embodiments, the first metal contact may comprise a first portion which contacts side walls of the first gate structure, and a second portion which is spaced apart from the side walls of the first gate structure on top of the first portion.

[0016] In some embodiments, a width of the first portion may be greater than a width of the second portion at an interface between the first portion and the second portion.

[0017] In some embodiments, a lowermost surface of the second metal contact may be closer to an upper surface of the substrate than is an uppermost surface of the second epitaxial layer.

[0018] In some embodiments, a field insulating film may be provided on the substrate, wherein the first metal contact contacts the field insulating film, and the second metal contact does not directly contact the field insulating film.

[0019] In some embodiments, the lowermost surface of the first metal contact may be coplanar with the lowermost surface of the first epitaxial layer.

[0020] In some embodiments, the first area may comprise an NMOS transistor, and the second area may comprise a PMOS transistor.

[0021] In some embodiments, a first barrier metal may be provided which completely covers the outer circumferential surface of the first epitaxial layer, and a second barrier metal may be provided which is located only on a part of the second epitaxial layer.

[0022] In some embodiments, an area of the first barrier metal may be greater than an area of the second barrier metal.

[0023] In some embodiments, a first silicide layer may be provided which completely covers the outer circumferential surface of the first epitaxial layer, and a second silicide layer may be provided which is located only at the top of the second epitaxial layer.

[0024] In some embodiments, the first and second silicide layers may have different thicknesses.

[0025] In some embodiments, the first silicide layer may comprise a composition different from the second silicide layer.

[0026] In some embodiments, a third epitaxial layer may be provided which completely covers the outer circumferential surface of the second epitaxial layer, wherein the third epitaxial layer comprises a material different from the second epitaxial layer.

[0027] In some embodiments, the second metal contact may completely cover the outer circumferential surface of the third epitaxial layer.

[0028] According to still another aspect of the inventive concepts, there is provided a semiconductor device including a substrate which includes a first area and a second area, a first fin-type pattern extending in a first direction on the first area, a second fin-type pattern extending in a second direction on the second area, a first gate structure which is in contact with the first fin-type pattern and extends to intersect the first direction, a second gate structure which is contact with the second fin-type pattern and extends to intersect the second direction, a first epitaxial layer on the first fin-type pattern on at least one side of the first gate structure, a second epitaxial layer on the second fin-type pattern on at least one side of the second gate structure, a first metal contact which is on the first epitaxial layer and includes a metal, and a second metal contact which is on the second epitaxial layer and includes a metal, wherein the first metal contact includes a first portion which contacts side walls of the first gate structure, and a second portion which is spaced apart from the side walls of the first gate structure on top of the first portion.

[0029] In some embodiments, the gate structure may comprise a gate insulating film, a gate electrode on the gate insulating film, and a spacer on at least one side of the gate electrode, wherein the first portion contacts the spacer, and the second portion does not contact the spacer.

[0030] In some embodiments, the first portion may be in direct contact with the spacer or the first epitaxial layer.

[0031] In some embodiments, an interlayer insulating film may be provided which covers the gate structure and the first epitaxial layer, wherein the interlayer insulating film does not contact the first epitaxial layer.

[0032] In some embodiments, the first metal contact may completely surround the outer circumferential surface of the first epitaxial layer.

[0033] In some embodiments, a field insulating film may be provided on the substrate, and the first metal contact may contact the field insulating film.

[0034] In some embodiments, a third epitaxial layer may be provided which completely covers the outer circumferential surface of the first epitaxial layer, wherein the third epitaxial layer includes a material different from the first epitaxial layer.

[0035] According to still another aspect of the inventive concepts, there is provided a semiconductor device including a first fin-type pattern extending in a first direction on a substrate, a gate structure which intersects the first fin-type pattern, a first epitaxial layer on the first fin-type pattern on at least one side of the gate structure, and a metal contact which includes a first portion that contacts side walls of the gate structure, and a second portion that is spaced apart from the side walls of the gate structure on top of the first portion, wherein the first portion contacts the first epitaxial layer, and a width of the first portion is greater than a width of the second portion at an interface between the first portion and the second portion.

[0036] In some embodiments, the gate structure may comprise a gate insulating film, a gate electrode on the gate insulating film, and a spacer on at least one side of the gate electrode, wherein the first portion contacts the spacer.

[0037] In some embodiments, an interlayer insulating film may be provided which covers the gate structure and the first epitaxial layer, wherein the interlayer insulating film does not contact the first epitaxial layer.

[0038] In some embodiments, the interlayer insulating film may be disposed between the second portion and the gate structure.

[0039] In some embodiments, a barrier metal may be provided between the metal contact and the first epitaxial layer and between the metal contact and the interlayer insulating film.

[0040] In some embodiments, the barrier metal may comprise a first part which is in contact with the first epitaxial layer, and a second part which is in contact with the interlayer insulating film, and the first part and the second part have compositions different from each other.

[0041] In some embodiments, the metal contact may completely surround the outer circumferential surface of the first epitaxial layer.

[0042] In some embodiments, a field insulating film may be provided on the substrate, and the metal contact may contact the field insulating film.

[0043] In some embodiments, the first epitaxial layer may comprise Si and SiC, and the semiconductor device may operate as an NMOS transistor.

[0044] In some embodiments, a second epitaxial layer may be provided which covers a first area of the first epitaxial layer, wherein the metal contact covers an upper surface of the second epitaxial layer.

[0045] In some embodiments, the second epitaxial layer may comprise a material different from the first epitaxial layer.

[0046] In some embodiments, a field insulating film may be provided on the substrate, wherein a lower surface of the second epitaxial layer contacts the field insulating film, and an upper surface of the second epitaxial layer contacts the metal contact.

[0047] In some embodiments, an interlayer insulating film is provided which covers the gate structure and the first epitaxial layer, wherein the interlayer insulating film contacts an outer surface of a lower part of the first epitaxial layer, and the metal contact covers an outer surface of an upper part of the first epitaxial layer.

[0048] In some embodiments, a second epitaxial layer may be provided which completely covers an outer circumferential surface of the first epitaxial layer, wherein the second epitaxial layer comprises a material different from the first epitaxial layer.

[0049] In some embodiments, the first epitaxial layer may comprise SiGe, the second epitaxial layer may comprise Si or SiC, and the semiconductor device may operate as a PMOS transistor.

[0050] In some embodiments, a portion of the upper surface of the first fin-type pattern which overlaps the first epitaxial layer may be coplanar with a portion of the upper surface of the first fin-type pattern which overlaps the gate structure.

[0051] In some embodiments, the first portion and the second portion of the metal contact may comprise the same material and may be integrally formed.

[0052] According to still another aspect of the inventive concepts, there is provided a semiconductor device including a first fin-type pattern which protrudes upwardly from an upper surface of a field insulating film, a first epitaxial layer on the first fin-type pattern, an interlayer insulating film on the field insulating film that covers the first fin-type pattern and the first epitaxial layer, and a metal contact that extends along an outer circumferential surface of the first epitaxial layer within the interlayer insulating film, the metal contact contacting the field insulating film, an upper surface of the metal contact being coplanar with upper surface of the interlayer insulating film.

[0053] In some embodiments, a barrier metal may be provided between the metal contact and the first epitaxial layer and between the metal contact and the interlayer insulating film.

[0054] In some embodiments, the barrier metal may comprise a first area which is in contact with the first epitaxial layer, and a second area which is in contact with the interlayer insulating film, and the first area and the second area have compositions different from each other.

[0055] In some embodiments, a second epitaxial layer may be provided which completely covers the outer circumferential surface of the first epitaxial layer, wherein the second epitaxial layer comprises a material different from the first epitaxial layer.

[0056] In some embodiments, the metal contact may completely cover the outer circumferential surface of the second epitaxial layer.

[0057] In some embodiments, an upper surface of the first fin-type pattern which overlaps the first epitaxial layer may be coplanar with an upper surface of the first fin-type pattern which overlaps the gate structure.

[0058] According to still another aspect of the inventive concepts, there is provided a semiconductor device including a first fin-type pattern and a second fin-type pattern which protrude upwardly from an upper surface of a field insulating film and extend in a first direction, a gate structure which intersects the first fin-type pattern and the second fin-type pattern, a first epitaxial layer on the first fin-type pattern on at least one side of the gate structure, a second epitaxial layer on the second fin-type pattern on at least one side of the gate structure, and a metal contact which covers outer circumferential surfaces of the first epitaxial layer and the second epitaxial layer, wherein the metal contact comprises a first portion which contacts side walls of the gate structure, and a second portion which is spaced apart from the side walls of the gate structure on top of the first portion.

[0059] In some embodiments, the first epitaxial layer and the second epitaxial layer may be spaced apart from each other.

[0060] In some embodiments, a width of the first portion of the metal contact may be greater than a width of the second portion of the metal contact at an interface between the first and second portions of the metal contact.

[0061] According to another aspect of the inventive concepts, there is provided a method for manufacturing a semiconductor device, the method including forming a first fin-type pattern that extends in a first direction on a substrate, forming a gate structure that intersects the first fin-type pattern on the substrate, growing a first epitaxial layer on the first fin-type pattern on at least one side of the gate structure, growing a dummy epitaxial layer on the first epitaxial layer to cover an outer surface of the first epitaxial layer, forming an interlayer insulating film which covers the dummy epitaxial layer, forming a trench which passes through the interlayer insulating film so that at least a portion of the dummy epitaxial layer is exposed, etching the dummy epitaxial layer using an etching material having an etching selectivity with respect to the first epitaxial layer, and forming a metal contact by gap-filling a space between the interlayer insulating film and the first epitaxial layer with a metal material.

[0062] In some embodiments, the metal contact may completely cover an outer circumferential surface of the first epitaxial layer.

[0063] In some embodiments, when etching the dummy epitaxial layer, a remaining part of the dummy epitaxial layer is left on the substrate to surround a lower part of the first epitaxial layer, and the metal contact is formed to surround an upper surface of the remaining part of the dummy epitaxial layer and the top of the first epitaxial layer.

[0064] In some embodiments, the metal contact may include a first portion which is in contact with a side surface of the gate structure, and a second portion which is spaced apart from the side surface of the gate structure, and the interlayer insulation film may be between the second portion and the gate structure.

[0065] In some embodiments, a barrier metal may be formed on the interlayer insulating film and the first epitaxial layer after etching the dummy epitaxial layer and before forming the metal contact.

[0066] In some embodiments, a second epitaxial layer may be formed to cover the first epitaxial layer on the first epitaxial layer before the dummy epitaxial layer is formed.

[0067] According to another aspect of the inventive concepts, there is provided a method of manufacturing a semiconductor device, the method including forming a first fin-type pattern that extends in a first direction in a first area on a substrate; forming a first gate structure that intersects the first fin-type pattern on the substrate, forming a second fin-type pattern that extends in a second direction in a second area on the substrate; forming a second gate structure that intersects the second fin-type pattern on the substrate, growing a first epitaxial layer on the first fin-type pattern on at least one side of the first gate structure, growing a second epitaxial layer that is different from the first epitaxial layer on the second fin-type pattern of at least one side of the second gate structure, growing a dummy epitaxial layer to cover an outer surface of the first epitaxial layer, forming an interlayer insulating film which covers the first area and the second area, forming a first trench to expose at least a part of the dummy epitaxial layer, and a second trench to expose a part of the second epitaxial layer, forming a first photoresist film which covers the second area, etching the dummy epitaxial layer using an etching material having an etching selectivity with respect to the first epitaxial layer, removing the first photoresist film, and forming a first metal contact in the first trench and a second metal contact in the second trench.

[0068] In some embodiments, a lowermost surface of the second metal contact may be lower than an uppermost surface of the second epitaxial layer.

[0069] In some embodiments, the first metal contact may completely surround an outer circumferential surface of the first epitaxial layer, and the second metal contact may contact only a part of the upper surface of the second epitaxial layer.

[0070] In some embodiments, a first barrier metal may be formed to completely cover the outer circumferential surface of the first epitaxial layer, and a second barrier metal may be formed on only a part of the second epitaxial layer.

[0071] In some embodiments, a second photoresist layer may be formed to cover the first area after removing the first photoresist film, and a silicide layer may be formed at the top of the second epitaxial layer.

[0072] According to another aspect of the inventive concepts, a semiconductor device is provided that includes a semiconductor substrate; a field insulating layer on the semiconductor substrate; a first fin-type structure that extends in a first direction along a top surface of a semiconductor substrate, the first fin-type structure extending upwardly through the field insulating layer; a first gate structure that extends in a second direction along a top surface of the semiconductor substrate to intersect the first fin-type structure; a first epitaxial layer extending upwardly from the first fin-type structure; and a metal contact covering at least a portion of side surfaces of the first epitaxial layer, wherein portions of the metal contact that cover the side surfaces of the first epitaxial layer have a substantially constant thickness.

[0073] In some embodiments, the metal contact may contact the field insulating layer and may contact the first epitaxial layer.

[0074] In some embodiments, a barrier metal may be provided between the first epitaxial layer and the metal contact, between the metal contact and the field insulating layer, and between the metal contact and an interlayer insulating film that covers sidewalls of the metal contact.

[0075] In some embodiments, a second epitaxial layer may be provided on lower portions of the side surfaces of the first epitaxial layer, where the second epitaxial layer has a thickness that is substantially the same as the substantially constant thickness of the portions of the metal contact that cover the side surfaces of the first epitaxial layer

[0076] In some embodiments, a second epitaxial layer may be provided that completely covers the side surfaces and a top surface of the first epitaxial layer, the metal contact completely covering side surfaces and a top surface of the second epitaxial layer, wherein both the second epitaxial layer and the metal contact may contact the field insulating layer.

[0077] However, aspects of the inventive concepts are not restricted to those set forth herein. The above and other aspects of the inventive concepts will become more apparent to one of ordinary skill in the art to which the inventive concepts pertain by referencing the detailed description of the present concepts given below.

BRIEF DESCRIPTION OF THE DRAWINGS

[0078] The above and other aspects and features of the inventive concepts will become more apparent by the following description of example embodiments thereof with reference to the attached drawings, in which:

[0079] FIG. 1 is a layout diagram illustrating a semiconductor device according to an embodiment of the inventive concepts;

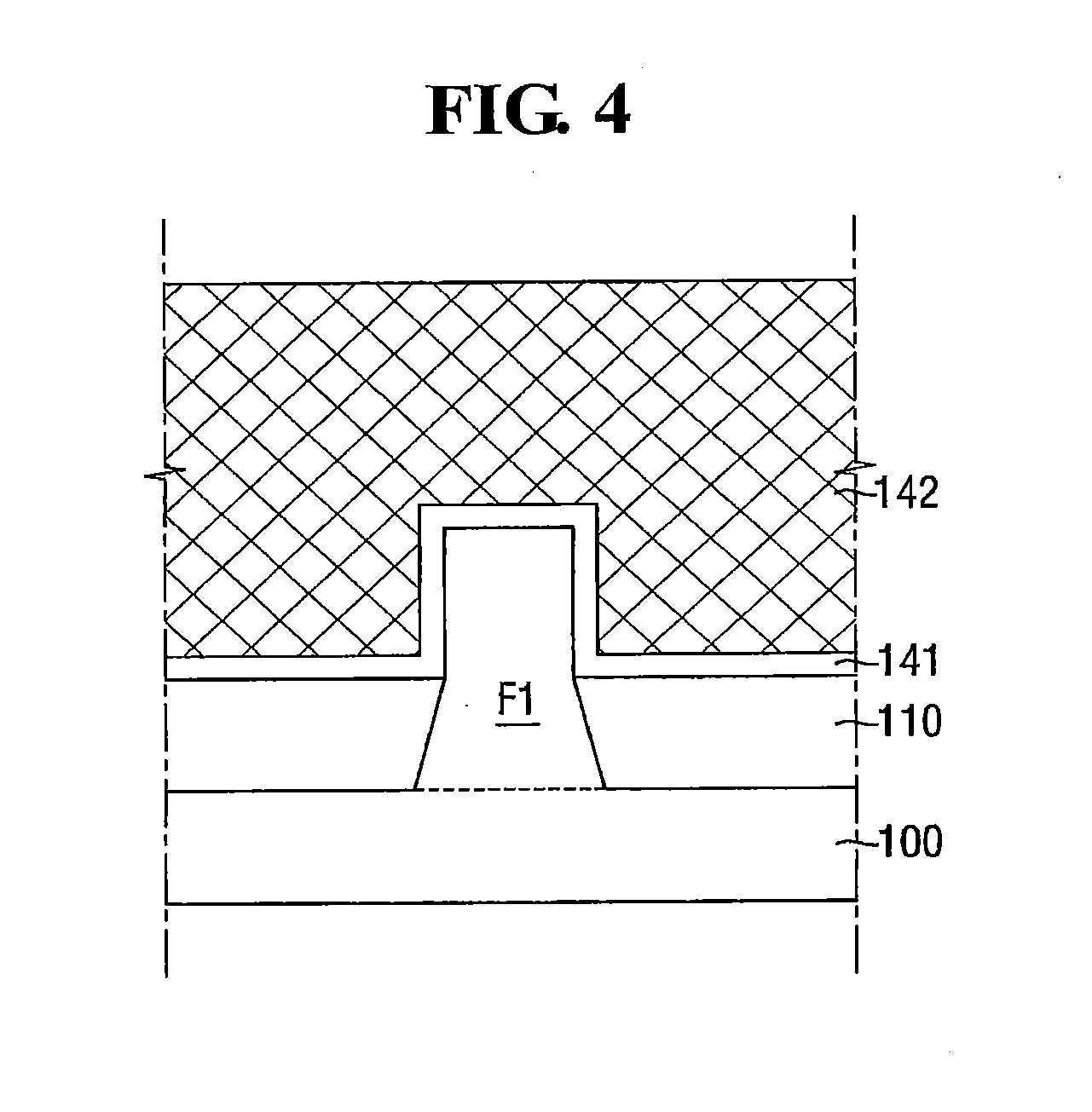

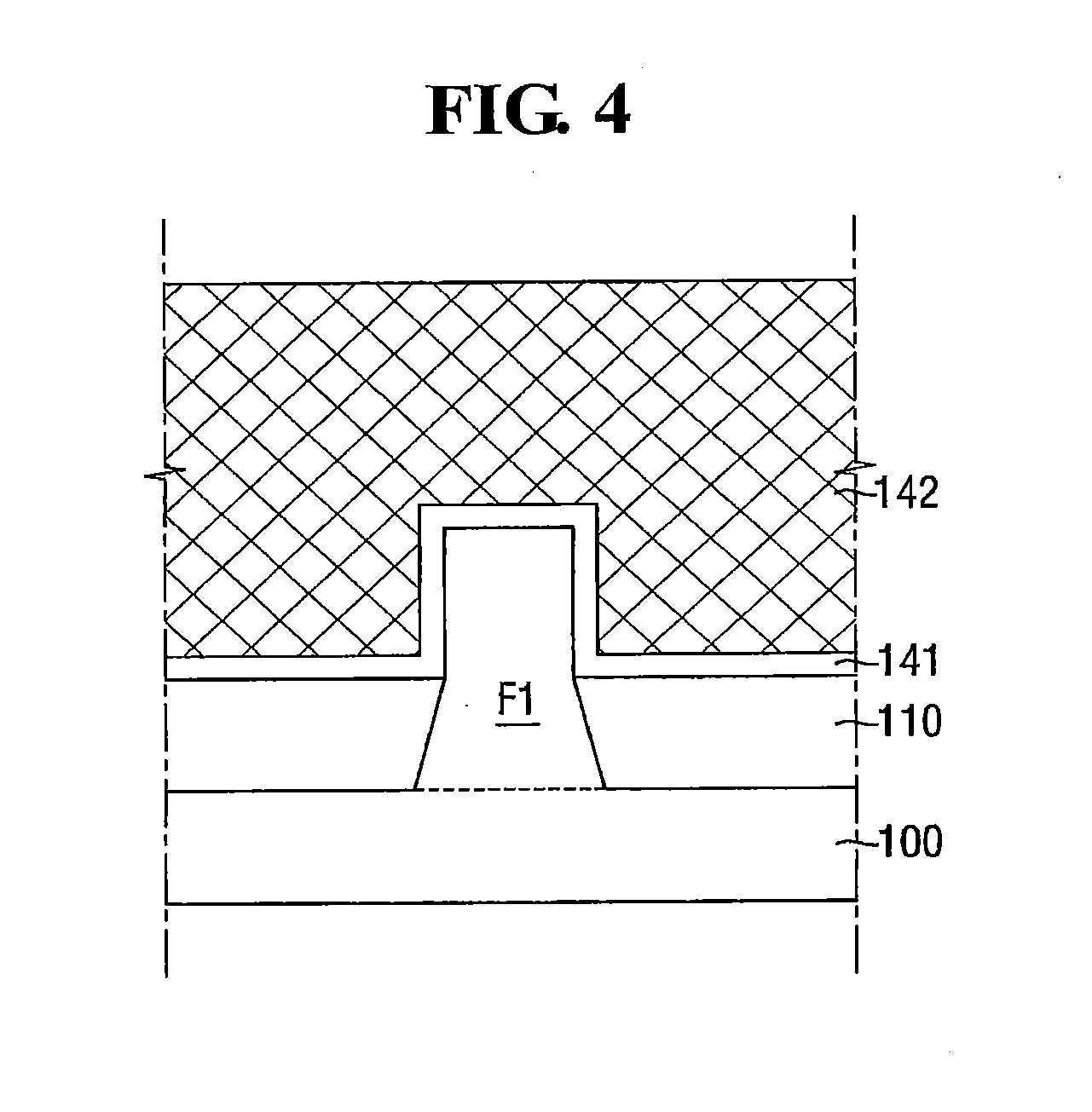

[0080] FIGS. 2, 3 and 4 are cross-sectional views taken along lines A-A, B-B and C-C, respectively, of the semiconductor device of FIG. 1;

[0081] FIG. 5 is a cross-sectional view illustrating a semiconductor device according to another embodiment of the inventive concepts;

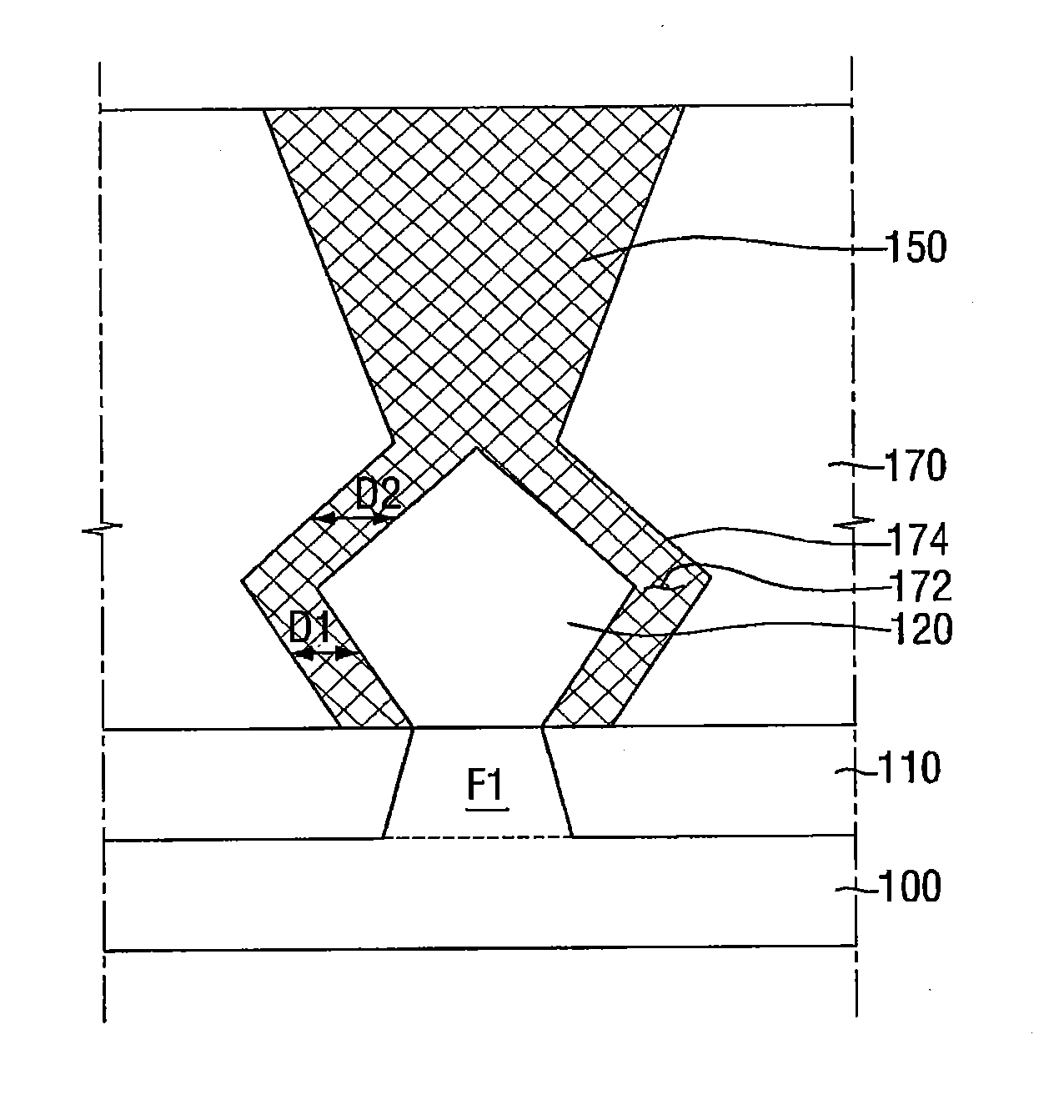

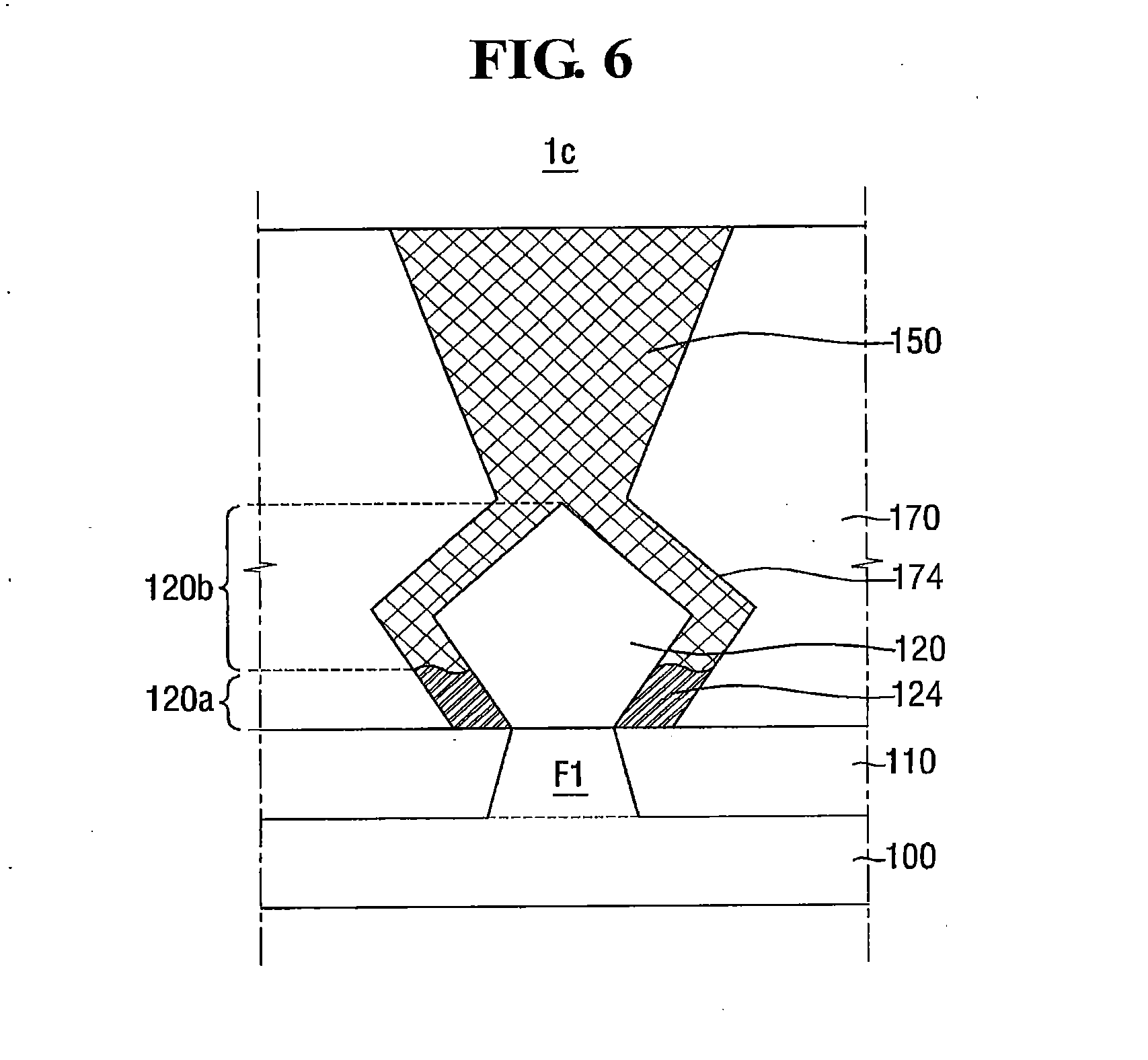

[0082] FIG. 6 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

[0083] FIG. 7 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

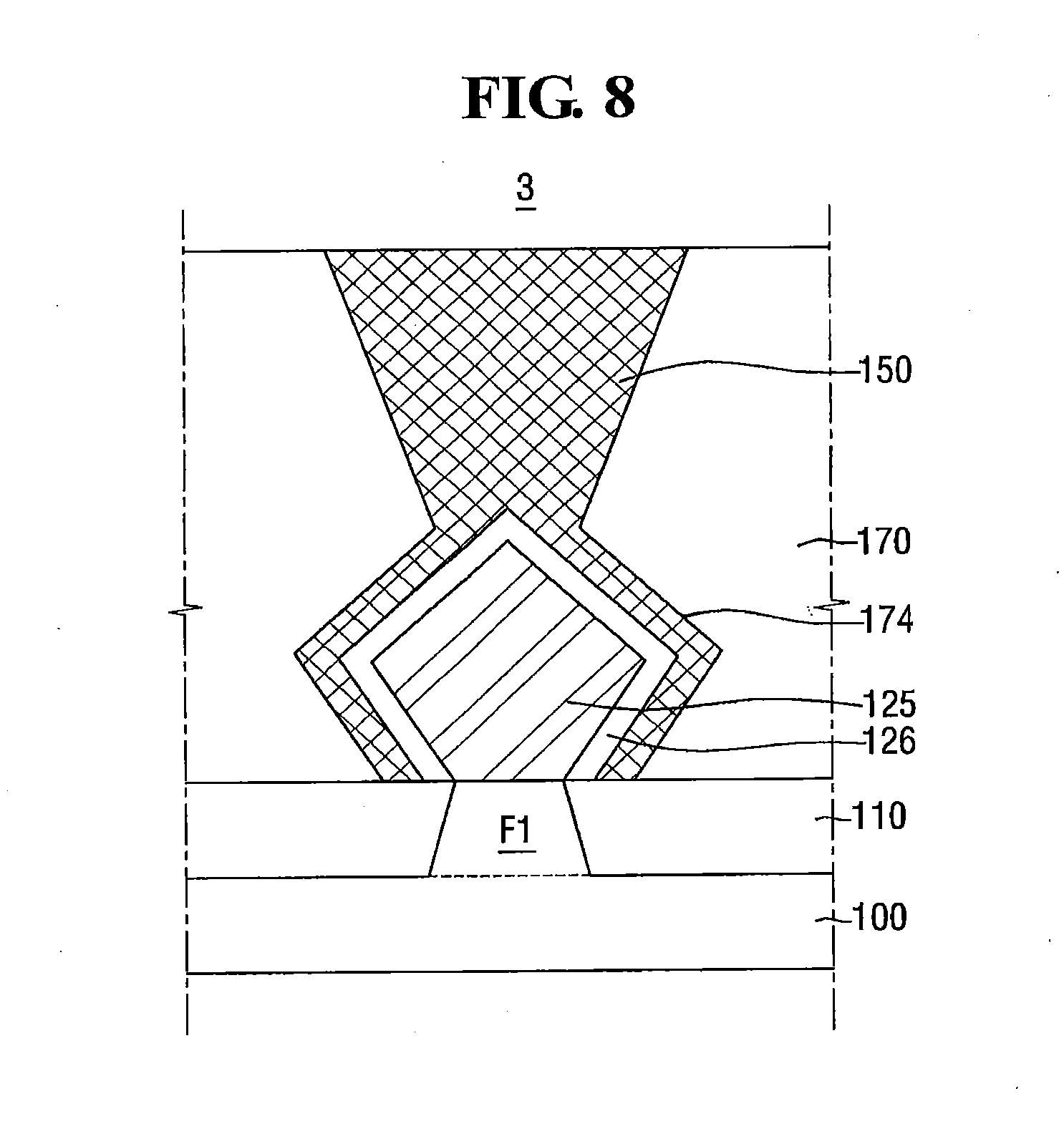

[0084] FIG. 8 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

[0085] FIG. 9 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

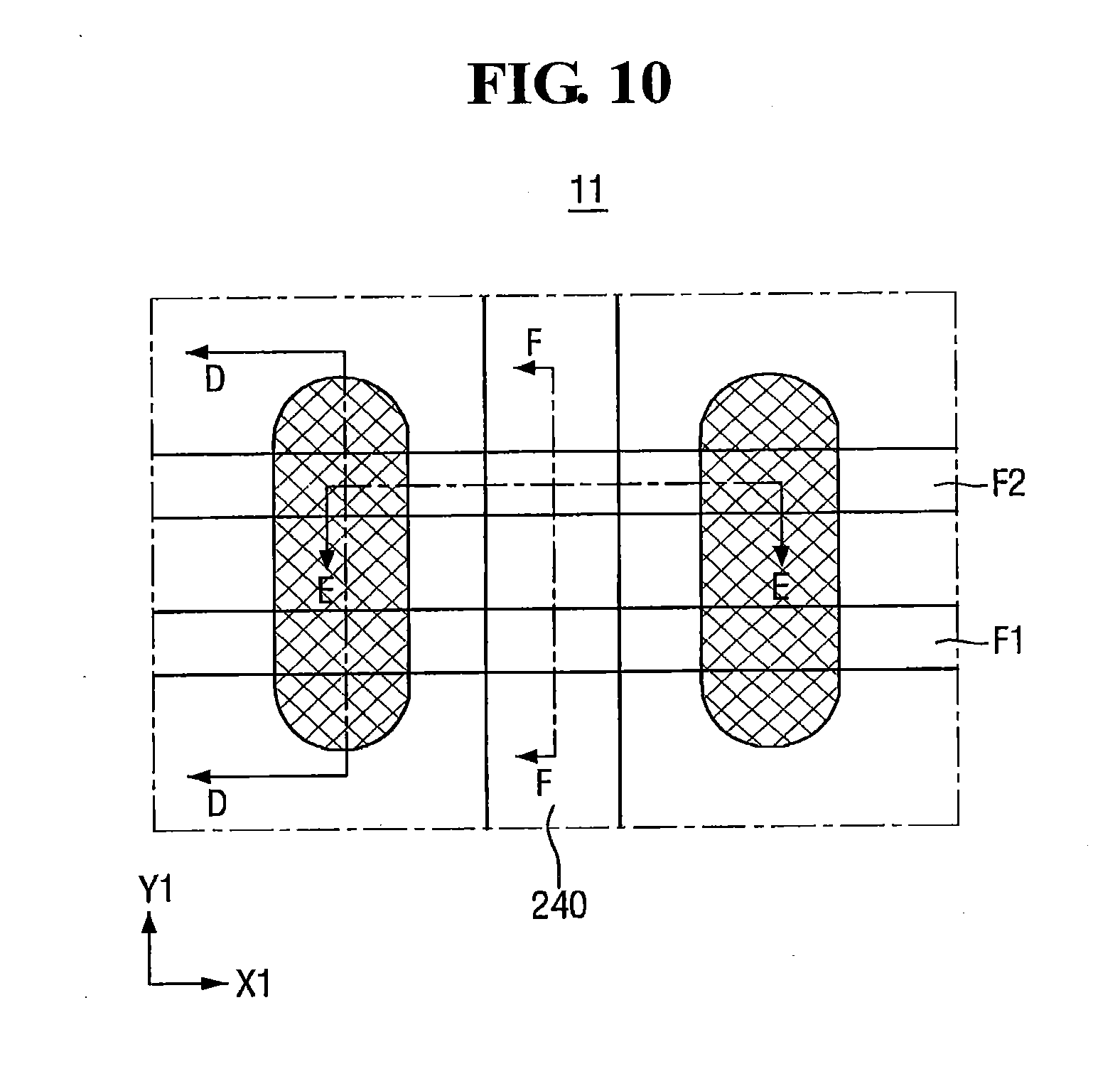

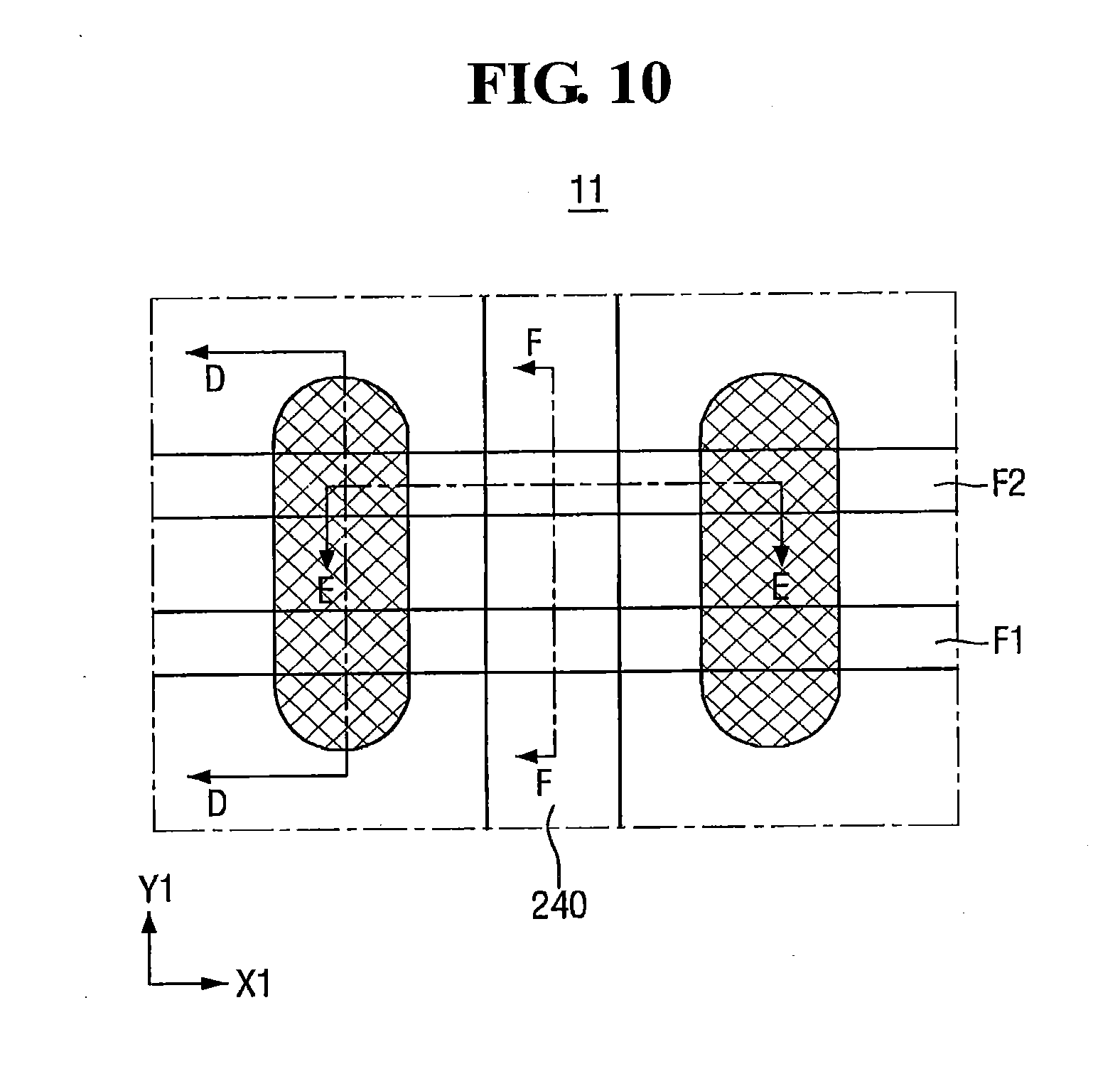

[0086] FIG. 10 is a layout diagram illustrating a semiconductor device according to still another embodiment of the inventive concepts;

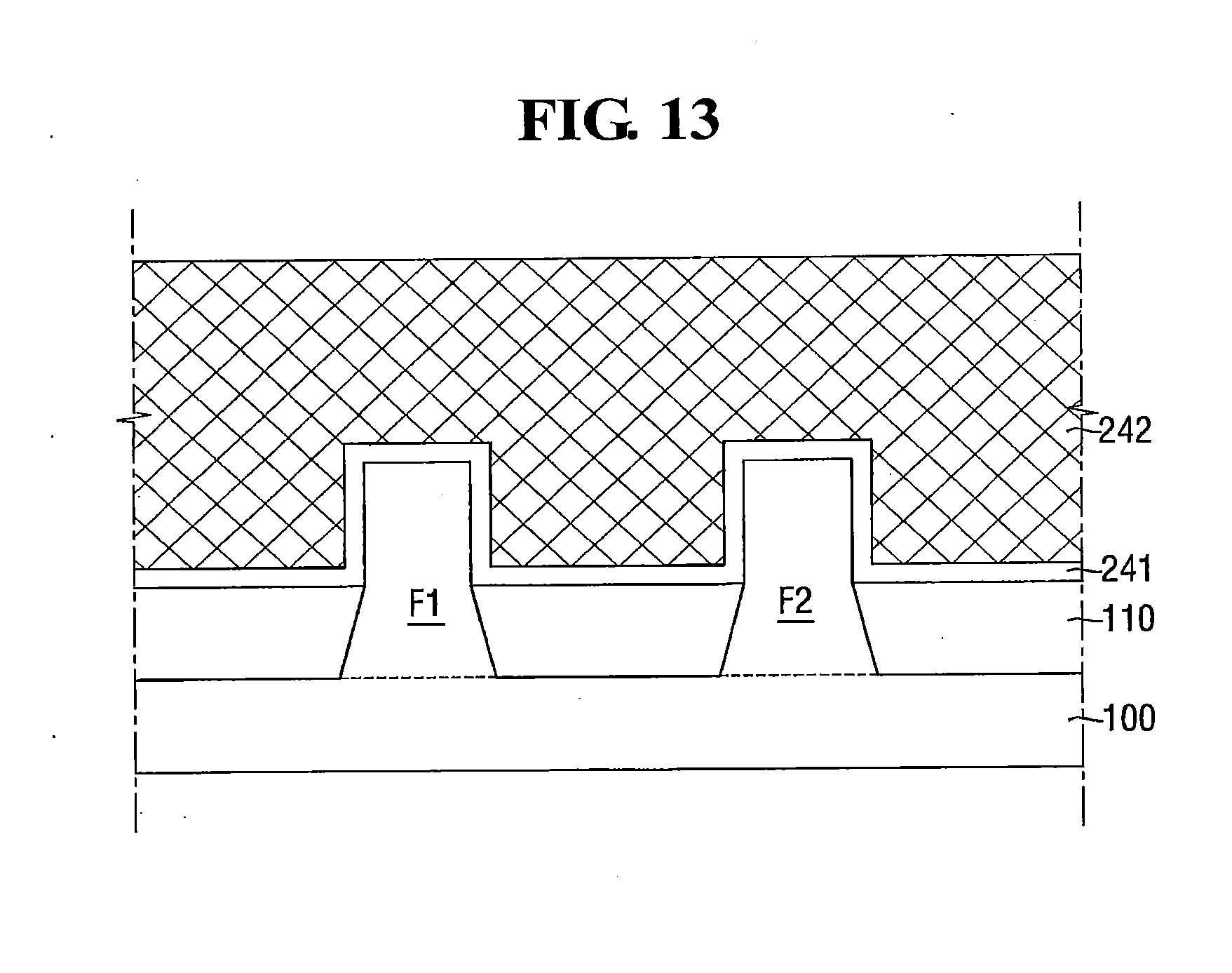

[0087] FIGS. 11, 12 and 13 are cross-sectionals view taken along lines D-D, E-E and F-F, respectively, of the semiconductor device of FIG. 10;

[0088] FIGS. 14A and 14B are cross-sectional views illustrating semiconductor devices according to further embodiments of the inventive concepts;

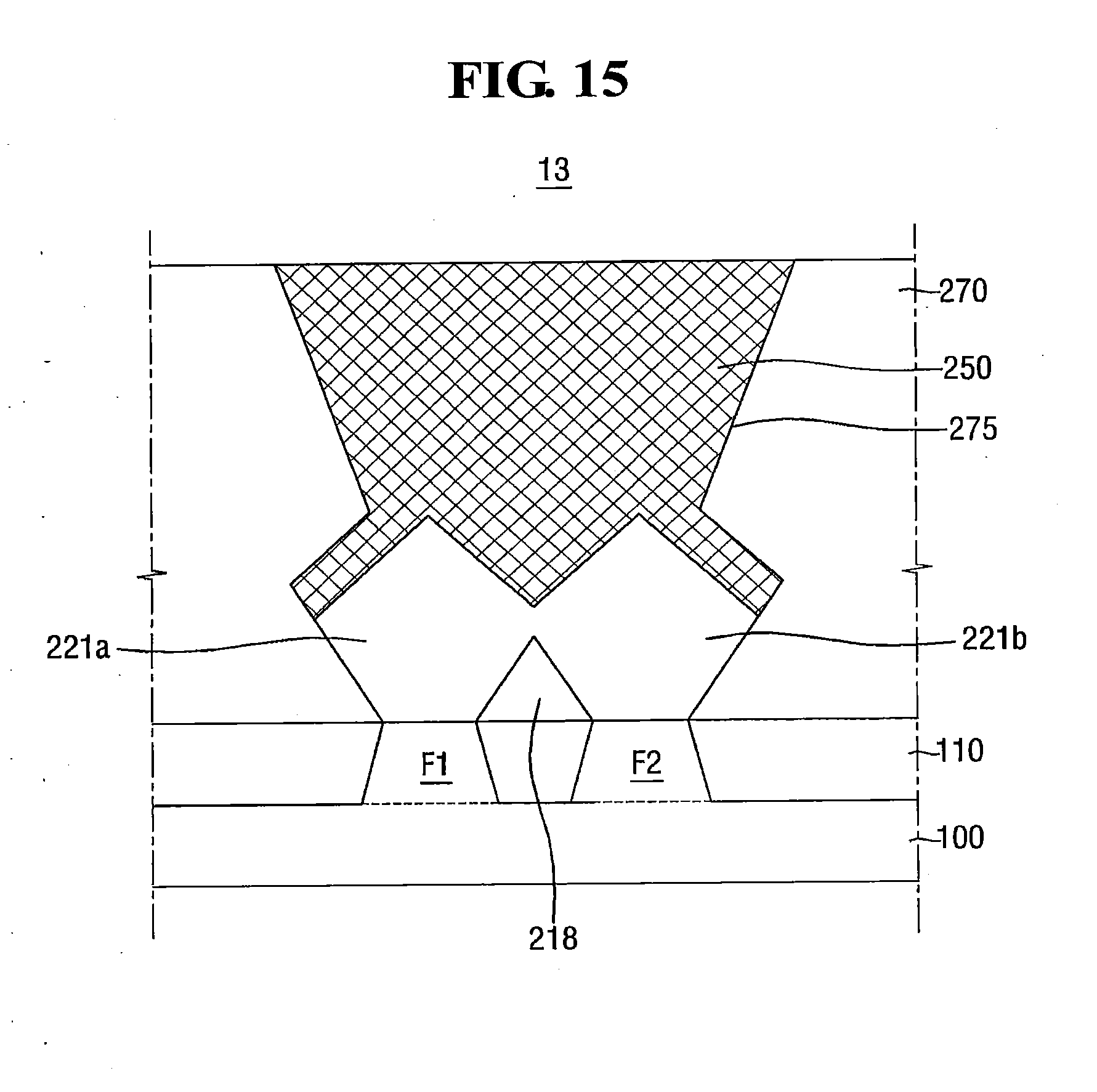

[0089] FIG. 15 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

[0090] FIG. 16 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts.

[0091] FIG. 17 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

[0092] FIG. 18 is a layout diagram illustrating a semiconductor device according to still another embodiment of the inventive concepts;

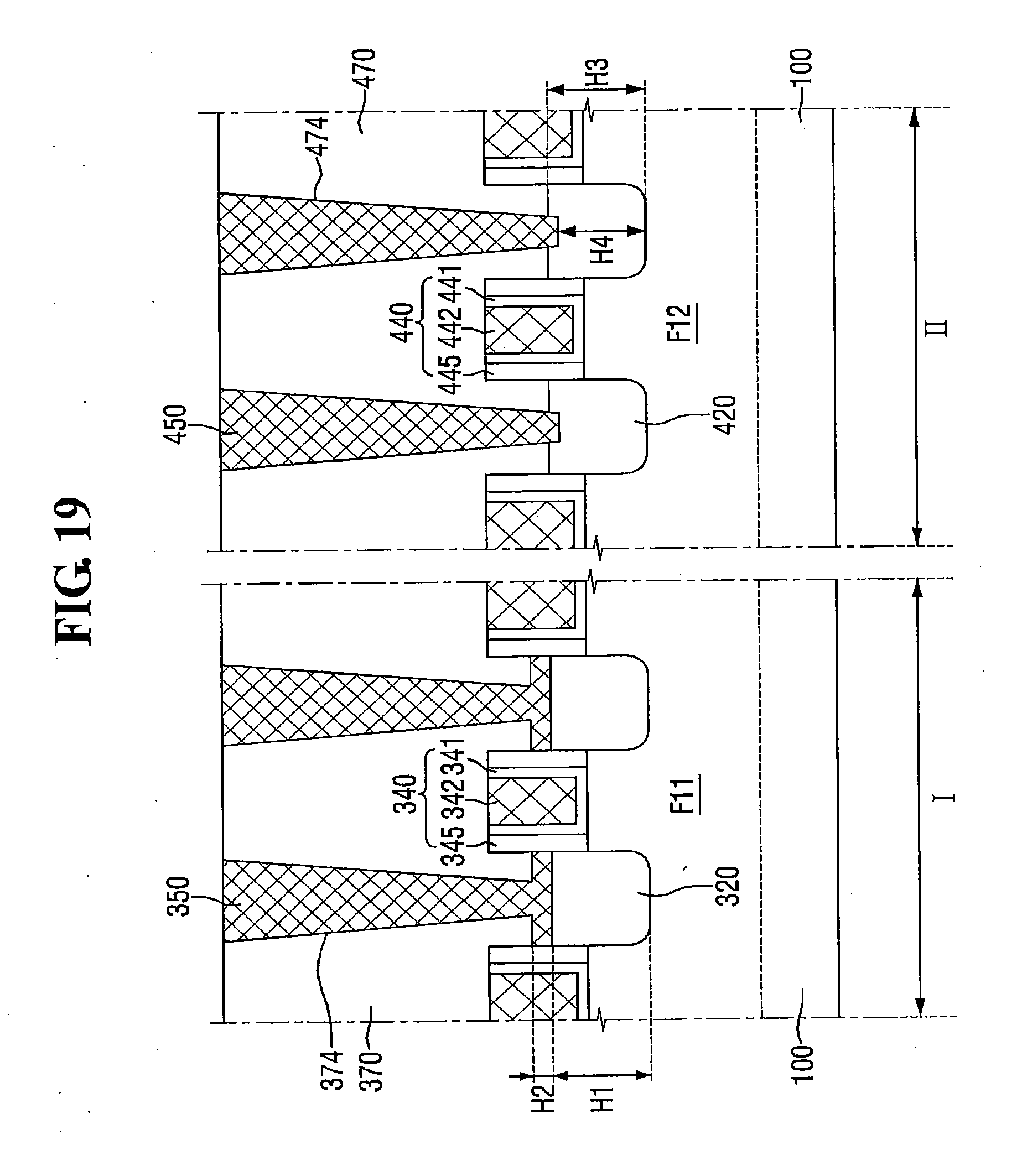

[0093] FIG. 19 is a cross-sectional view taken along lines G1-G1 and G2-G2 of the semiconductor device of FIG. 18;

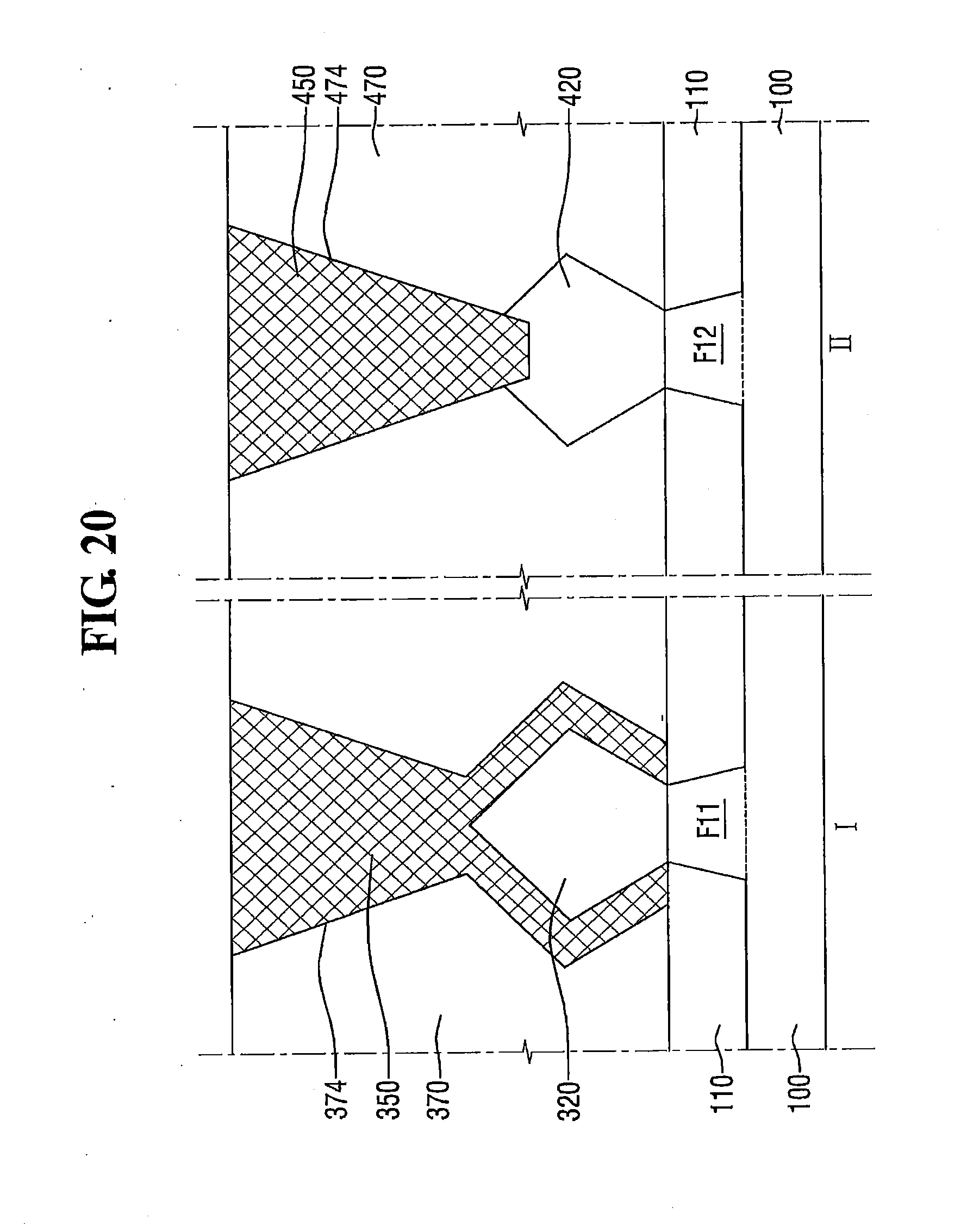

[0094] FIG. 20 is a cross-sectional view taken along lines I1-I1 and I2-I2 of the semiconductor device of FIG. 18;

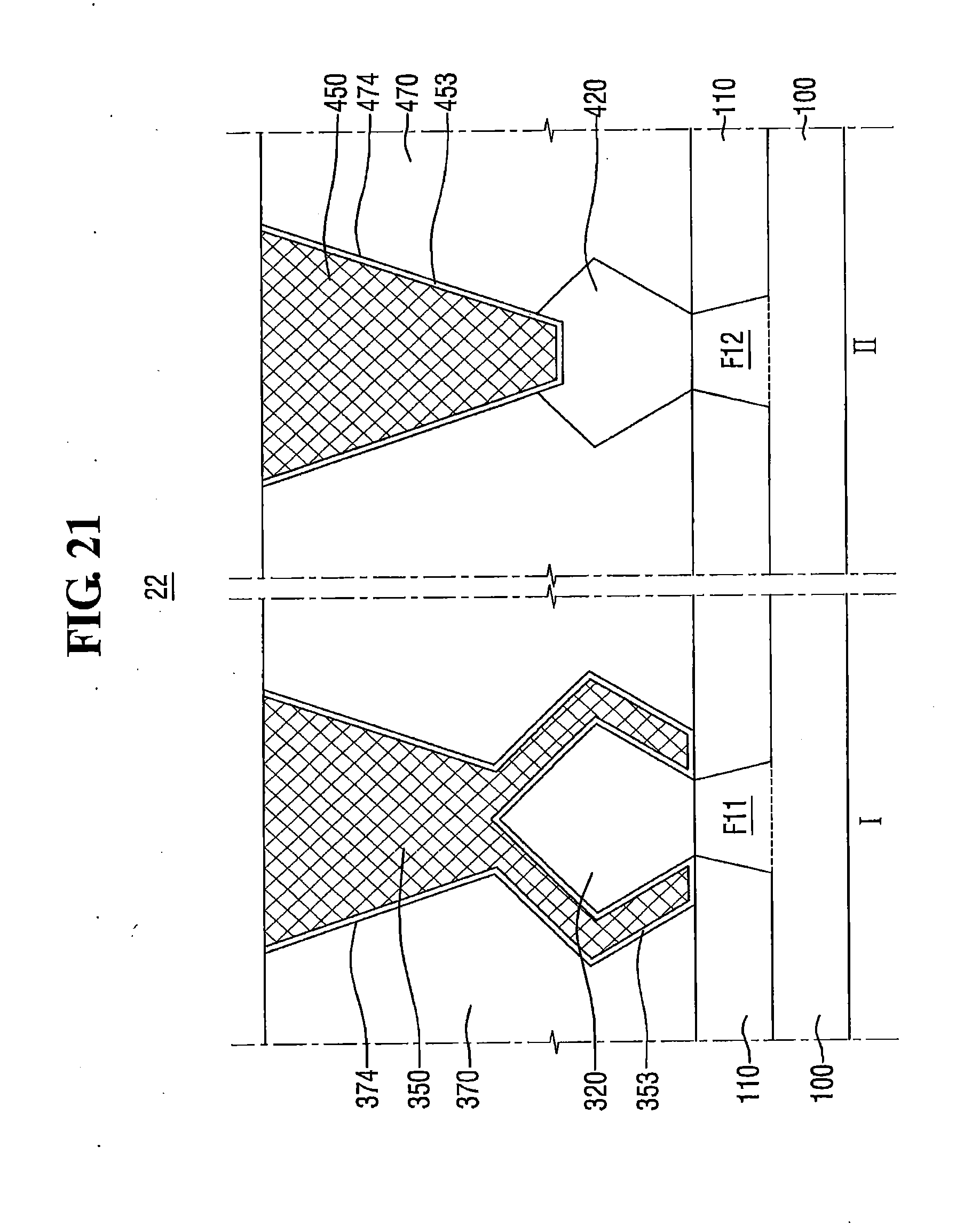

[0095] FIG. 21 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

[0096] FIG. 22 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts.

[0097] FIG. 23 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

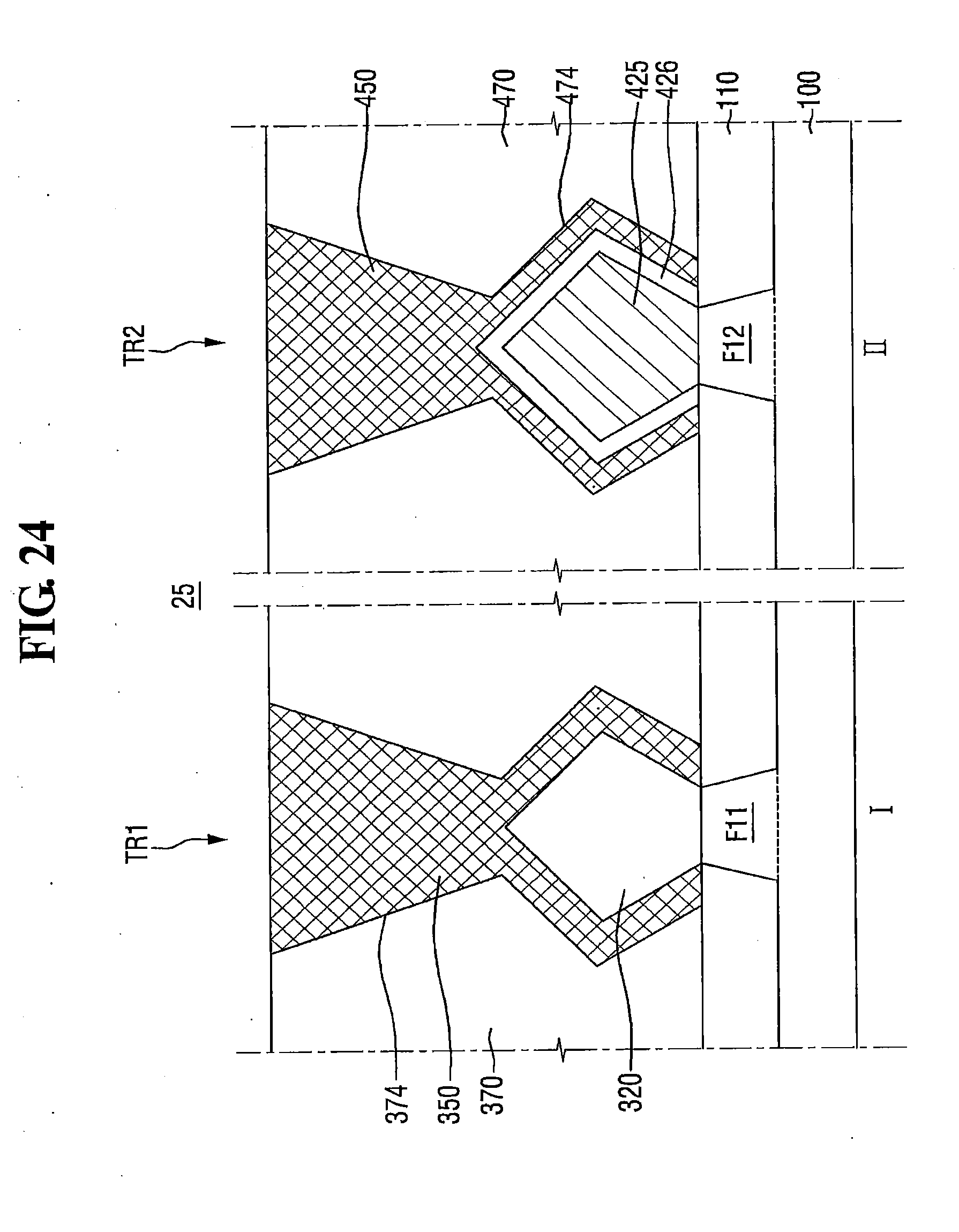

[0098] FIG. 24 is a cross-sectional view illustrating a semiconductor device according to still another embodiment of the inventive concepts;

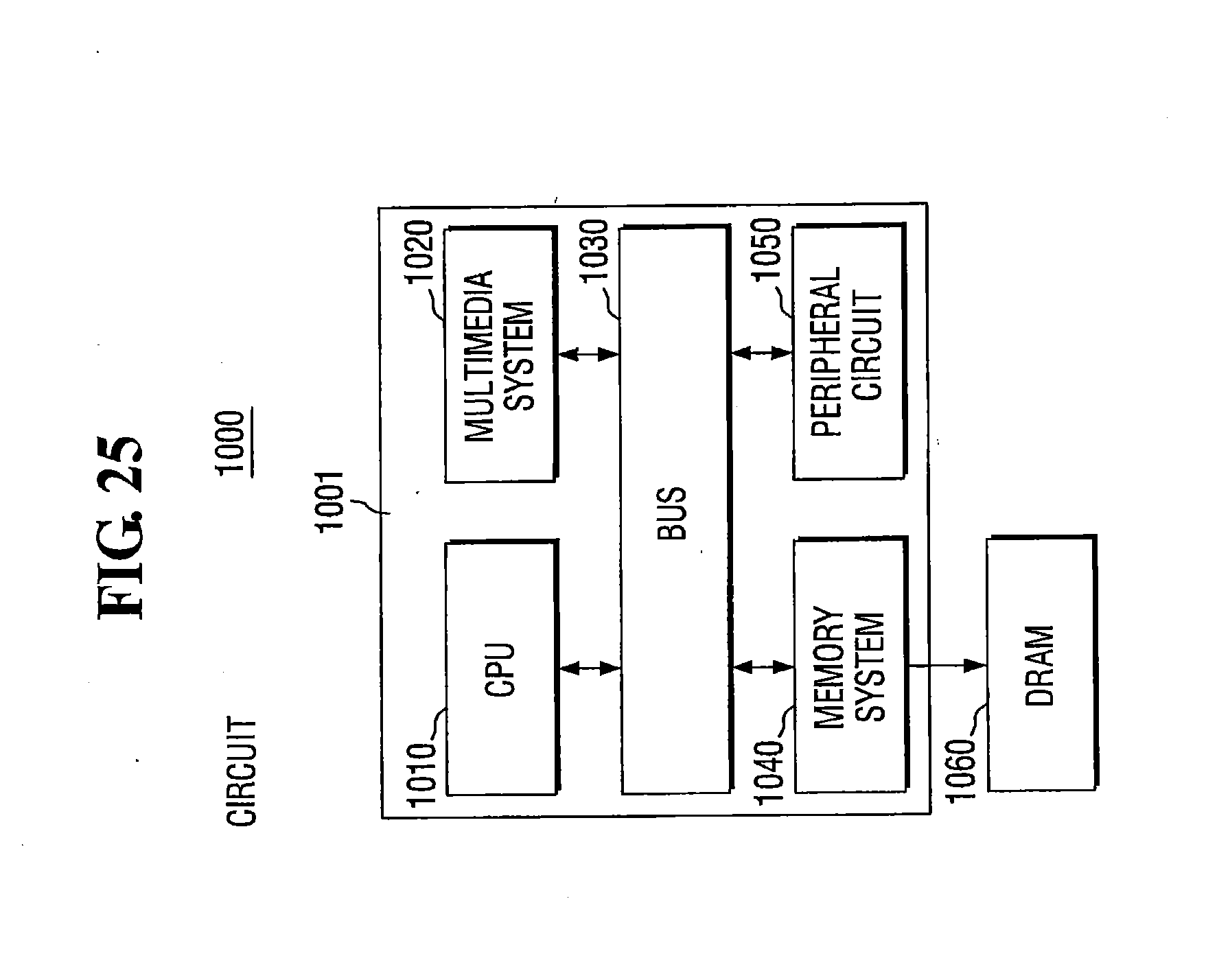

[0099] FIG. 25 is a block diagram of a SoC system including a semiconductor device according to embodiments of the inventive concepts;

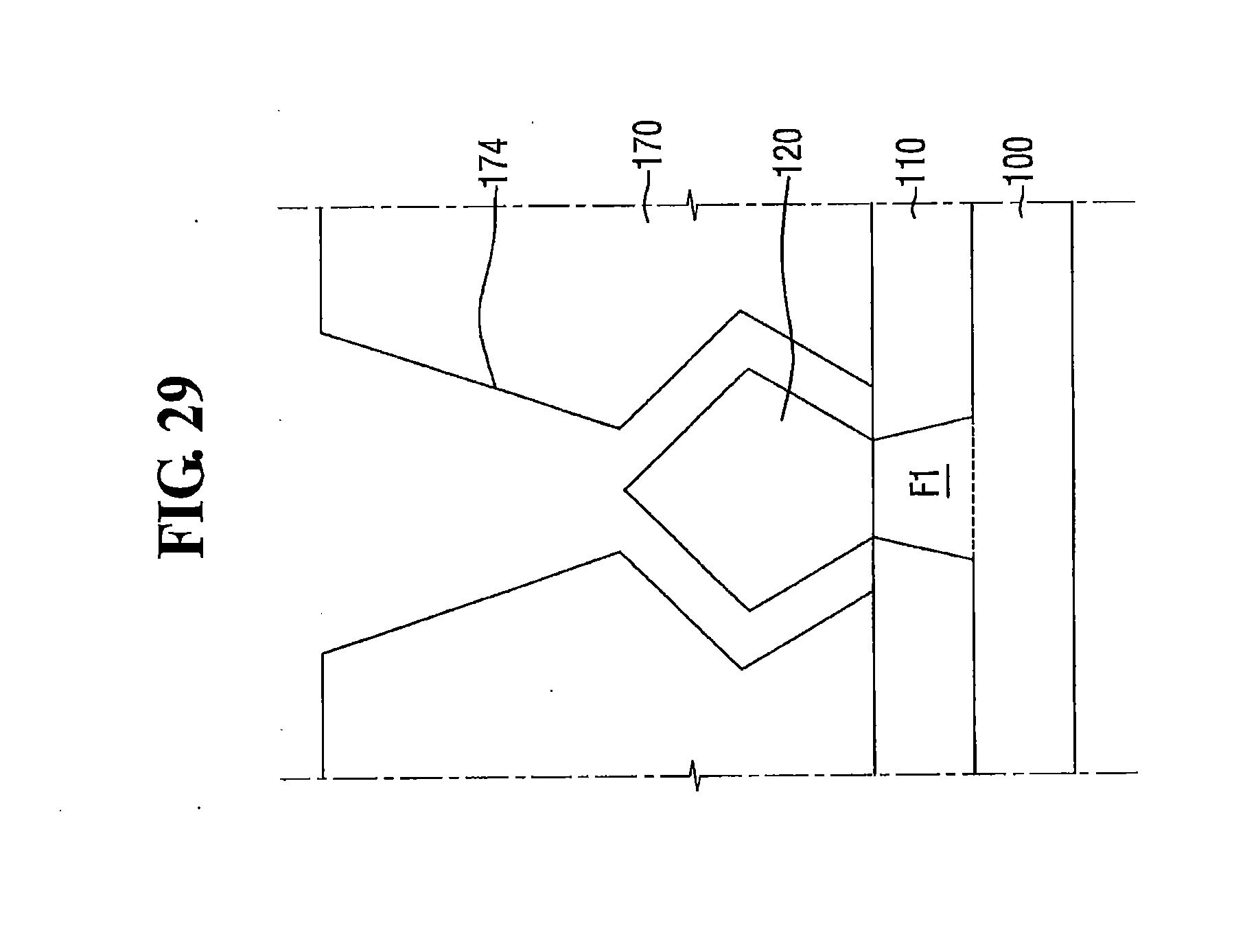

[0100] FIGS. 26 to 29 are intermediate step diagrams illustrating a method of manufacturing a semiconductor device according to some embodiments of the inventive concepts; and

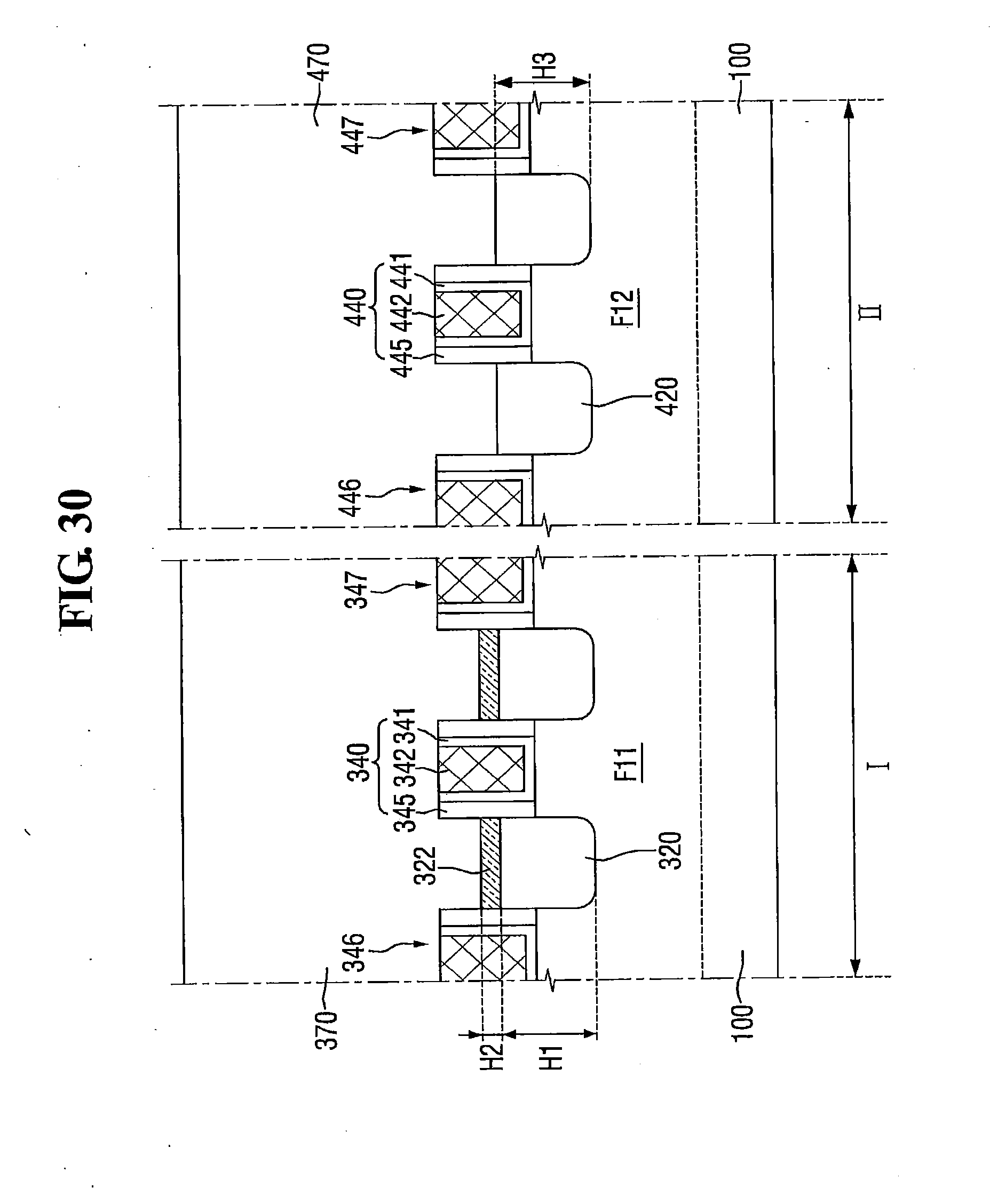

[0101] FIGS. 30 to 33 are intermediate step diagrams illustrating a method of manufacturing the semiconductor device according to some embodiments of the inventive concepts.

DETAILED DESCRIPTION OF THE EMBODIMENTS

[0102] Advantages and features of the inventive concepts and methods of accomplishing the same may be understood more readily by reference to the following detailed description and the accompanying drawings. The inventive concepts may, however, be embodied in many different forms and should not be construed as being limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete and will fully convey the inventive concepts to those skilled in the art. In the drawings, the thickness of layers and regions may be exaggerated for clarity.

[0103] It will be understood that when an element or layer is referred to as being "on," "contacting" or "connected to" another element or layer, it can be directly on, directly contacting or directly connected to the other element or layer, or alternatively, intervening elements or layers may be present. In contrast, when an element is referred to as being "directly on," "directly contacting" or "directly connected to" another element or layer, there are no intervening elements or layers present. Like numbers refer to like elements throughout. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

[0104] Spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. It will be understood that the spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. For example, if the device in the figures is turned over, elements described as "below" or "beneath" other elements or features would then be oriented "above" the other elements or features. Thus, the exemplary term "below" can encompass both an orientation of above and below. The device may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein interpreted accordingly.

[0105] The use of the terms "a" and "an" and "the" and similar referents in the context of describing the inventive concept (especially in the context of the following claims) are to be construed to cover both the singular and the plural, unless otherwise indicated herein or clearly contradicted by context. The terms "comprising," "having," "including," and "containing" are to be construed as open-ended terms (i.e., meaning "including, but not limited to,") unless otherwise noted.

[0106] It will be understood that, although the terms first, second, etc. may be used herein to describe various elements, these elements should not be limited by these terms. These terms are only used to distinguish one element from another element. Thus, for example, a first element, a first component or a first section discussed below could be termed a second element, a second component or a second section without departing from the teachings of the inventive concepts.

[0107] The inventive concepts will be described with reference to plan and cross-sectional views in which embodiments of the inventive concepts are shown. It will be appreciated, however, that the profile of an exemplary view may be modified according to manufacturing techniques and/or allowances. That is, the embodiments discussed herein are not intended to limit the scope of the inventive concepts but covers all changes and modifications that can be caused due to a change in manufacturing process. Thus, regions shown in the drawings are illustrated in schematic form and the shapes of the regions are presented simply by way of illustration and not as a limitation.

[0108] Unless defined otherwise, all technical and scientific terms used herein have the same meaning as commonly understood by one of ordinary skill in the art to which the inventive concepts belong. It is noted that the use of any and all examples, or exemplary terms provided herein is intended merely to better explain the inventive concepts and is not a limitation on the scope of the inventive concepts unless otherwise specified.

[0109] Those skilled in the art will appreciate that many variations and modifications can be made to the embodiments discussed below without substantially departing from the principles of the inventive concepts.

[0110] Hereinafter, semiconductor devices according to some embodiments of the inventive concepts will be described with reference to FIGS. 1 to 25.

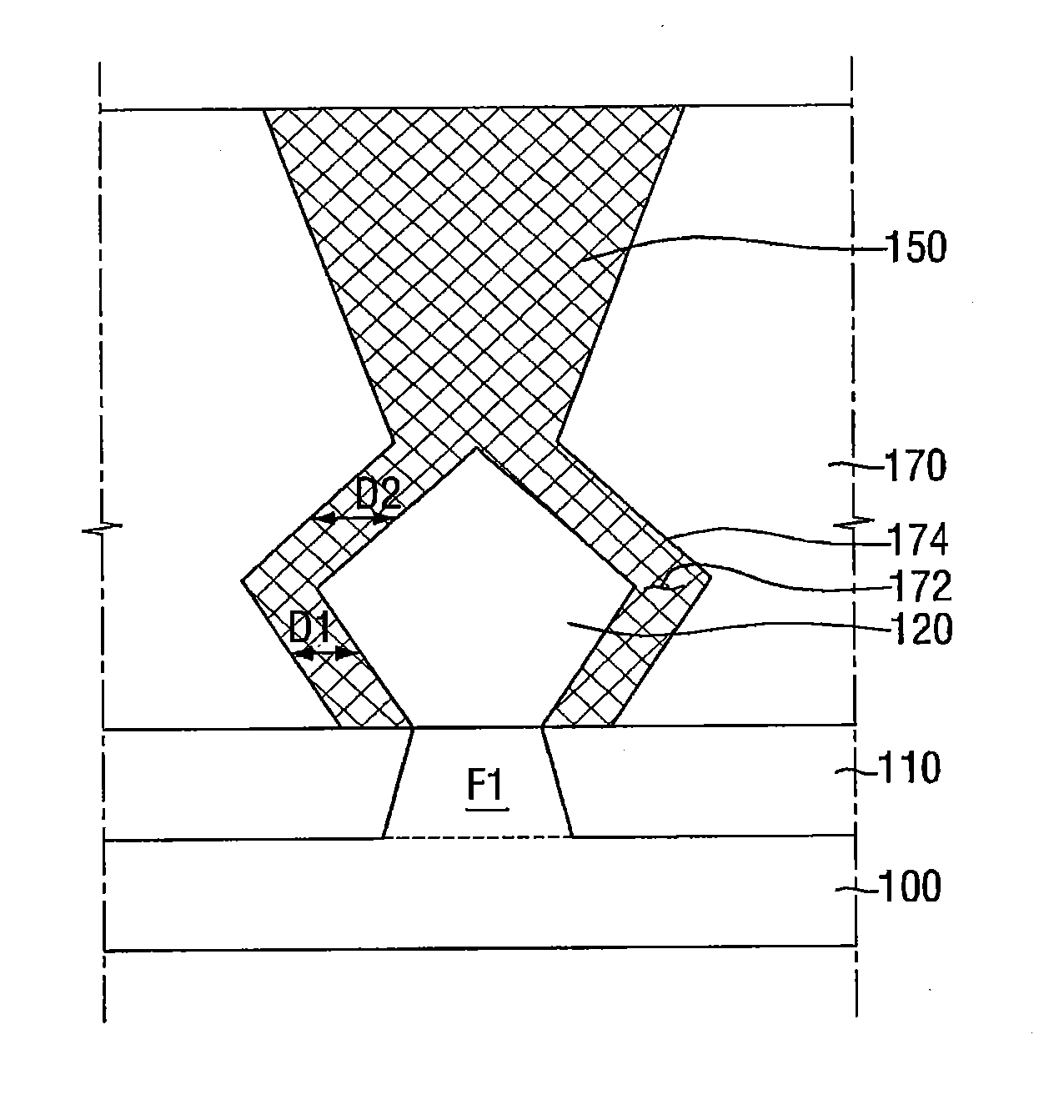

[0111] FIG. 1 is a layout diagram illustrating a semiconductor device according to an embodiment of the inventive concepts. FIGS. 2, 3 and 4 are cross-sectional views taken along lines A-A, B-B and C-C, respectively, of the semiconductor device of FIG. 1.

[0112] Referring to FIGS. 1 to 4, the semiconductor device 1a includes a substrate 100, a first fin-type pattern F1, a gate structure 140, a first epitaxial layer 120, a metal contact 150, an interlayer insulating film 170 and the like.

[0113] The substrate 100 may be, for example, a semiconductor substrate. The substrate 100 may include one of silicon, strained silicon (Si), silicon alloy, silicon carbide (SiC), silicon germanium (SiGe), silicon germanium carbide (SiGeC), germanium, germanium alloy, gallium arsenide (GaAs), indium arsenide (InAs) and a III-V semiconductor, a II-VI semiconductor, combinations thereof, and laminations thereof. Alternatively, the substrate may be an organic plastic substrate rather than the semiconductor substrate 100. Hereinafter, the substrate 100 will be described as being made of silicon.

[0114] The substrate 100 may be a P-type semiconductor substrate or an N-type semiconductor substrate. In other embodiments, an insulating substrate may be used as the substrate 100. Specifically, silicon on insulator (SOI) substrate may be used. When using an SOI substrate, there may be an advantage of being able to reduce a delay time in an operation process of the semiconductor device 1a.

[0115] The first fin-type pattern F1 may extend longer along a first direction X1 than along a third direction Y1. The first fin-type pattern F1 may be a part of the substrate 100 and may include an epitaxial layer that is grown from the substrate 100.

[0116] The field insulating film 110 is formed on the substrate 100 and is used for element isolation. The field insulating film 110 may be a shallow trench isolation (STI) structure which may be advantageous for high integration because it may exhibit excellent isolation characteristics within a small area. Other field insulating films may be used in other embodiments. The field insulating films 110 may include, for example, at least one of silicon oxide, silicon nitride, silicon oxynitride and combinations thereof. An upper portion of the first fin-type pattern F1 may protrude upwardly from an upper surface of the field insulating film 110.

[0117] The gate structure 140 may be formed on the first fin-type pattern F1 in a direction which intersects the first fin-type pattern F1. For example, the gate structure 140 may extend along the third direction Y1 which intersects the first direction X1.

[0118] The gate structure 140 may include a gate insulating film 141, a gate electrode 142, a spacer 145 and the like which are sequentially formed on the first fin-type pattern F1. By such a structure, channels may be formed on both side surfaces and the upper surface of the first fin-type pattern F1.

[0119] Although it is not clearly illustrated in the drawings, an interface film may be formed between the first fin-type pattern F1 and the gate insulating film 141. The interface film may serve to reduce or prevent a defective interface between the first fin-type pattern F1 and the gate insulating film 141. The interface film may include a low dielectric material layer having a dielectric constant (k) of 9 or less, for example, a silicon oxide film (k is approximately 4) or a silicon oxynitride film (k is approximately 4 to 8 depending on the respective oxygen and nitrogen contents). Further, the interface film may also be made of silicate, or may be made of a combination of the aforementioned films.

[0120] The gate insulating film 141 may be formed on the field insulating film 110 and the first fin-type pattern F1. The gate insulating film 141 may contain a material having a high dielectric constant (high-k). Specifically, the gate insulating film 141 may contain, for example, any one of the materials selected from a group which includes HfSiON, HfO.sub.2, ZrO.sub.2, Ta.sub.2O.sub.5, TiO.sub.2, SrTiO.sub.3, BaTiO.sub.3 and SrTiO.sub.3. The gate insulating film 141 may be formed to have a suitable thickness, depending on the types of element to be formed. According to some embodiments of the inventive concepts, as illustrated in FIG. 3, the gate insulating film 141 may extend upward along the side walls of a gate spacer 145 which will be described later.

[0121] The gate electrode 142 may contain a conductive material. In some embodiments of the inventive concepts, the gate electrode 142 may contain a metal having high conductivity, but the inventive concepts are not limited thereto. That is, in other embodiments of the inventive concepts, the gate electrode 142 may be made of a non-metal such as polysilicon. For example, the gate electrode 142 may be made of Si, SiGe or the like. The gate electrode 142 may be formed, for example, through the replacement process in some embodiments.

[0122] Although it is not clearly illustrated in the drawings, in some embodiments of the inventive concepts, the gate electrode 142 may include two or more laminated metal layers. The first metal layer may serve to adjust a work function, and the second metal layer may serve to fill a space formed by the first metal layer. For example, the first metal layer may contain at least one of TiN, TaN, TiC and TaC. Further, the second metal layer may contain W or Al. The gate structure 140 of the inventive concepts may be formed by a gate last manufacturing process.

[0123] The spacer 145 may be on at least one side of the gate electrode 142. As illustrated in FIG. 3, the spacer 145 may be on both sides of the gate electrode 142. The spacer 145 may include at least one of a nitride film and an oxynitride film. In FIG. 3, one side surface of the spacer 145 is illustrated as a straight line, but the inventive concepts are not limited thereto. For example, in other embodiments of the inventive concepts, the spacer 145 may have a curved shape, an L shape or the like.

[0124] The first epitaxial layer 120 may be formed on the first fin-type pattern F1 on at least one side of the gate structure 140. The first epitaxial layer 120 may be formed on both sides of the gate structure 140. The first epitaxial layer 120 may be in contact with the side surface of the spacer. The first epitaxial layer 120 may be a source/drain of the semiconductor device 1a.

[0125] The first epitaxial layer 120 may have various shapes. For example, the first epitaxial layer 120 may have a diamond shape or a rectangular shape in some embodiments. However, the inventive concepts are not limited thereto.

[0126] The first epitaxial layer 120 may be formed by an epitaxial growth method. In some embodiments, the first epitaxial layer 120 may contain silicon or germanium. In other embodiments, the first epitaxial layer 120 may include a compound semiconductor, and for example, may contain a group IV-IV compound semiconductor or a group III-V compound semiconductor. Specifically, taking the group IV-IV compound semiconductor as an example, the epitaxial layer 120 may be a binary compound or a ternary compound containing at least two or more of carbon (C), silicon (Si), germanium (Ge) and tin (Sn), or a compound in which these elements are doped with a Group IV element. Taking the group III-V compound semiconductor as an example, the epitaxial layer may be a binary compound, a ternary compound or a quaternary compound which is formed of at least one of aluminum (Al), gallium (Ga) and indium (In) as a group III element with at least one of phosphorus (P), arsenic (As) and antimony (Sb) as a group V element. Although it is not illustrated in the drawings, the first epitaxial layer 120 may have an LDD structure. However, the inventive concepts are not limited thereto.

[0127] When the semiconductor device 1a according to an embodiment of the inventive concept is a PMOS transistor, the first epitaxial layer 120 may contain a compressive stress material. For example, the compressive stress material may be a material having a lattice constant larger than Si, for example, SiGe. The compressive stress material may improve the mobility of the carriers of the channel area, by adding a compressive stress to the first fin-type pattern F1.

[0128] In contrast, when the semiconductor device a is an NMOS transistor, the first epitaxial layer 120 may be the same material as the substrate 100 or may be a tensile stress material. For example, when the substrate 100 is Si, the first epitaxial layer 120 may be Si or a material (e.g., SiC) having a lattice constant that is smaller than Si.

[0129] The interlayer insulating film 170 may be formed on the semiconductor substrate 100. The interlayer insulating film 170 may cover the gate structure 140 and the first epitaxial layer 120. However, the interlayer insulating film 170 may be formed so as not to be in direct contact with the first epitaxial layer 120.

[0130] The interlayer insulating film 170 may electrically insulate the semiconductor elements located below the interlayer insulating film 170 from the semiconductor element(s) located above the interlayer insulating film 170. The interlayer insulating film 170 may be formed of a silicon oxide, such as borosilicate glass (BSG), phosphosilicate glass (PSG), borophosphosilicate glass (BPSG), undoped silicate glass (USG), tetraethylorthosilicate glass (TEOS) or high density plasma-CVD (HDP-CVD).

[0131] The metal contact 150 may surround an outer circumferential surface of the first epitaxial layer 120. As used herein, the "outer circumferential surface" of an epitaxial layer that is formed above a fin-type pattern refers to the outer surface of the epitaxial layer with the exception of the bottom surface thereof that is above the fin-type pattern. For example, referring to FIG. 2, the metal contact 150 may completely surround the outer surface of the first epitaxial layer 120, except for the bottom of the first epitaxial layer 120 which contacts the first fin-type pattern F1. The metal contact 150 may be in contact with the upper surface of the field insulating film 110. The metal contact 150 may surround the first epitaxial layer 120 with a constant thickness. For example, a thickness D1 of the metal contact 150 which wraps around the bottom of the first epitaxial layer 120 may be substantially the same as a thickness D2 of the metal contact 150 which wraps around the top of the first epitaxial layer 120. However, the inventive concepts are not limited thereto.

[0132] As the metal contact 150 completely surrounds all but the bottom surface of the first epitaxial layer 120, the interlayer insulating film 170 may be spaced apart from the first epitaxial layer 120. The metal contact 150 may be formed within a first trench 174 which penetrates the interlayer insulating film 170.

[0133] The first trenches 174 may have a tapered shape. That is, the first trench 174 may be formed in a trapezoidal or reverse trapezoidal shape. However, the inventive concepts are not limited thereto, and the first trench 174 may have a rectangular shape. The first trench 174 may expose the outer circumferential surface of the first epitaxial layer 120 and a part of the field insulating film 110. However, the inventive concepts are not limited thereto.

[0134] The metal contact 150 may electrically connect a wiring that is on a top surface of the interlayer insulating film 170 with the first epitaxial layer 120 or the first fin-type pattern F1. For example, Al, Cu, W or the like may be used as the metal contact 150, but embodiments of the inventive concepts are not limited thereto. As illustrated in FIG. 2, the upper surface of the interlayer insulating film 170 may be on the same plane as the upper surface of the metal contact 150. The upper surfaces of the interlayer insulating film 170 and the metal contact 150 may be aligned through the planarization process (e.g., CMP process).

[0135] Referring to FIG. 3, the metal contact 150 may include a first portion 150a and a second portion 150b. The second portion 150b may be formed on the first portion 150a, and the second portion 150b and the first portion 150a may be integrally formed. The first portion 150a may be in contact with the upper surface of the first epitaxial layer 120, and may be in contact with the side walls of the gate structure 140. The second portion 150b may be on top of the first portion 150a and may be spaced apart from the side walls of the gate structure 140 (e.g., by a length L3). The interlayer insulating film 170 may be disposed between the second portion 150b and the gate structure 140. A part of the second portion 150b may be located below the upper surface of the gate structure 140.

[0136] At an interface between the first portion 150a and the second portion 150b, a width L1 of the first portion 150a may be greater than a width L2 of the second portion 150b. The first portion 150a and the second portion 150b may include the same material. However, the inventive concepts are not limited thereto.

[0137] As described with reference to FIGS. 1 to 4, the semiconductor device 1a includes the metal contact 150 which completely surrounds the outer surface of the first epitaxial layer 120 that extends above the field insulating film 110. This may reduce the contact resistance between the metal contact 150 and the first epitaxial layer 120.

[0138] The first epitaxial layer 120 may be surrounded by the metal contact 150, while remaining in an original form that is grown on the first fin-type pattern F1. To maintain the original form of the first epitaxial layer 120, a dummy epitaxial layer may be formed on the first epitaxial layer 120, and subsequently, the interlayer insulating film 170 which covers the dummy epitaxial layer is formed. Subsequently, after forming the first trench 174 which exposes the dummy epitaxial layer, the dummy epitaxial layer is removed, and thereafter, a process of gap-filling the metal contact 150 within an area in which the dummy epitaxial layer is formed may be used. The detailed description thereof will be provided below.

[0139] The semiconductor manufacturing process of the inventive concepts may not use a separate silicide forming process. Thus, by forming the metal contact 150 to surround first epitaxial layer 120 while remaining the original form, it is possible to reduce the contact resistance of the semiconductor device 1a and to further reduce the size of the contact. Thus, the semiconductor device 1a may exhibit improved performance.

[0140] FIG. 5 is a cross-sectional view illustrating a semiconductor device according to another embodiment of the inventive concepts. For convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiment will be omitted, and the differences will mainly be described.

[0141] Referring to FIG. 5, a semiconductor device 1b according to another embodiment of the inventive concepts may be operated substantially in the same manner as the semiconductor device 1a described above with reference to FIGS. 1 to 4.

[0142] However, the semiconductor device 1b may further include a barrier metal 153.

[0143] The barrier metal 153 may be formed on the inner surface of the first trench 174. The barrier metal 153 may include a first part 153a that is formed between the metal contact 150 and the first epitaxial layer 120, and a second part 153b that is formed between the metal contact 150 and the interlayer insulating film 170. That is, the first part 153a may be formed on the first epitaxial layer 120 so as to contact the first epitaxial layer 120, and the second part 153b may be formed so as contact the interlayer insulating film 170.

[0144] Thus, the barrier metal 153 may be formed along both side surfaces of the first trench 174 and the outer circumferential surface of the first epitaxial layer 120. The barrier metal 153 may be conformally formed along the inner surface of the first trench 174 with a constant thickness. The barrier metal 153 may contain titanium (Ti), titanium nitride (TiN) or tungsten nitride (WN). The barrier metal 153 may be formed using PVD, CVD or ILD methods.

[0145] The first part 153a and the second part 153b of the barrier metal 153 may be different from each other. For example, the first part 153a may contain a silicide material. The silicide material may be naturally generated at the interface between the first epitaxial layer 120 and the metal contact 150 during the manufacturing process in which the metal contact 150 is gap-filled in an area between the first epitaxial layer 120 and the interlayer insulating film 170. However, the inventive concepts are not limited thereto.

[0146] As the barrier metal 153 is included in the semiconductor device 1b, the contact resistance between the metal contact 150 and the first epitaxial layer 120 may be reduced, and the performance of the semiconductor device may be improved.

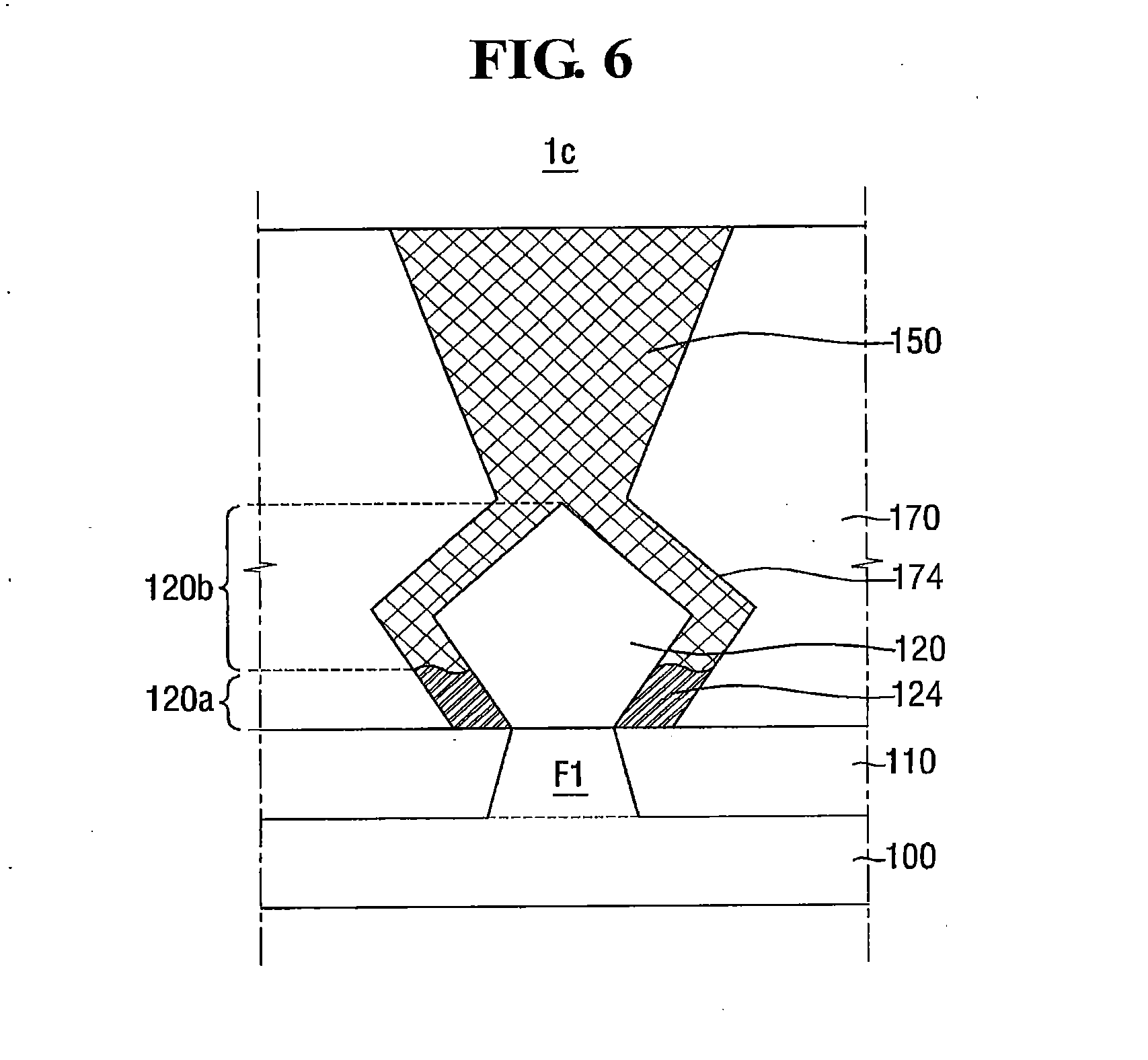

[0147] FIG. 6 is a cross-sectional view illustrating a semiconductor device 1c according to still another embodiment of the inventive concepts. For convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiment will be omitted, and the differences will mainly be described.

[0148] Referring to FIG. 6, the semiconductor device 1c may operate in substantially the same manner as the semiconductor device 1a that is described above with reference to FIGS. 1 to 4.

[0149] However, the semiconductor device 1c may further include a second epitaxial layer 124 which surrounds a first area 120a of the first epitaxial layer 120.

[0150] Specifically, the first epitaxial layer 120 may include a first area 120a and a second area 120b. The second area 120b is located over the first area 120a. The first area 120a may correspond to the bottom of the first epitaxial layer 120, and the second area 120b may correspond to the top of the first epitaxial layer 120.

[0151] The second epitaxial layer 124 surrounds the outer surface of the first area 120a and may be formed on the field insulating film 110. The second epitaxial layer 124 may be formed between the field insulating film 110 and the first area 120a. The second epitaxial layer 124 may be part of a dummy epitaxial layer that is formed during the manufacturing process. In particular, the second epitaxial layer 124 may be a part of the dummy epitaxial layer that remains after other portions of the dummy epitaxial layer are removed via an etching process. The second epitaxial layer 124 may be located below the first trench 174. However, the inventive concepts are not limited thereto.

[0152] The metal contact 150 may cover the upper surface of the second epitaxial layer 124 and may surround the outer surface of the second area 120b of first epitaxial layer 120. The metal contact 150 may be formed on the second epitaxial layer 124 within the first trench 174.

[0153] The second epitaxial layer 124 may contain a material different from the first epitaxial layer 120. For example, when the semiconductor device 1c is an NMOS device, the first epitaxial layer 120 may contain Si and SiC, and the second epitaxial layer 124 may contain SiGe. However, the inventive concepts are not limited thereto.

[0154] Although the metal contact 150 wraps around only a part of the first epitaxial layer 120, the semiconductor device 1c may operate in substantially the same manner as the semiconductor device 1a that is described above.

[0155] FIG. 7 is a cross-sectional view illustrating a semiconductor device 2 according to still another embodiment of the inventive concepts. For convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiments will be omitted, and the differences will mainly be described.

[0156] Referring to FIG. 7, the semiconductor device 2 may operate in substantially the same manner as the semiconductor device 1a described above with reference to FIGS. 1 to 4.

[0157] However, the metal contact 150 of the semiconductor device 2 may surround only an outer surface of an upper portion 120d of the first epitaxial layer 120, and the interlayer insulating film 170 may surround an outer surface of a lower portion 120c of the first epitaxial layer 120.

[0158] In the case of the semiconductor device 2, as the dummy epitaxial layer is etched after being formed only on the upper portion 120d of the first epitaxial layer 120, it may have a shape as shown in FIG. 7.

[0159] The first trench 175 exposes only the upper portion 120d of the first epitaxial layer 120, and as the metal contact 150 is formed within the first trench 175, the metal contact 150 may contact only the upper portion 120d of the first epitaxial layer 120. The interlayer insulating film 170 contacts the lower portion 120c of the first epitaxial layer 120.

[0160] The semiconductor device 2 may operate in substantially the same manner as the semiconductor device 1a that is described above.

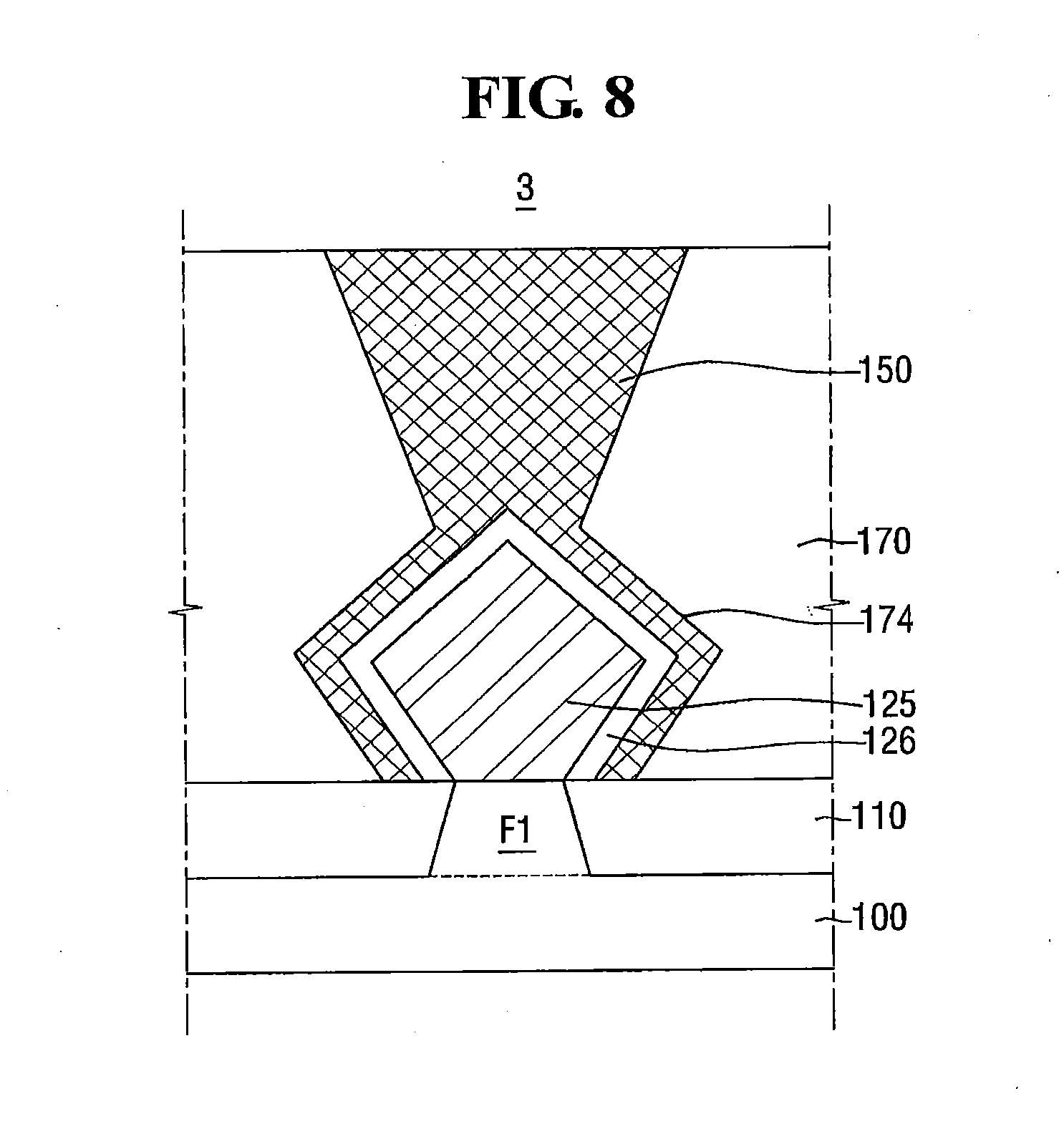

[0161] FIG. 8 is a cross-sectional view illustrating a semiconductor device 3 according to still another embodiment of the inventive concepts. For convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiment will be omitted, and the differences will mainly be described.

[0162] Referring to FIG. 8, the semiconductor device 3 may operate in substantially the same manner as the semiconductor device 1a that is described above with reference to FIGS. 1 to 4.

[0163] However, the semiconductor device 3 may further include a second epitaxial layer 126 which completely surrounds the outer circumferential surface of a first epitaxial layer 125. The second epitaxial layer 126 may be different from the first epitaxial layer 125.

[0164] The second epitaxial layer 126 may surround the outer circumferential surface of the first epitaxial layer 125. The second epitaxial layer 126 may completely surround an outer surface of the first epitaxial layer 125, except for a bottom portion of the first epitaxial layer 125 that contacts the first fin-type pattern F1. A part of the second epitaxial layer 126 may be in direct contact with the upper surface of the field insulating film 110. The second epitaxial layer 126 may surround the first epitaxial layer 125 with a constant thickness. For example, the thickness of the second epitaxial layer 126 which surrounds the lower portion of the first epitaxial layer 125 may be substantially the same as the thickness of the second epitaxial layer 126 which surrounds the upper portion of the first epitaxial layer 125. However, the inventive concepts are not limited thereto. Epitaxial layer 125 may be identical to epitaxial layer 120 that is discussed above with reference to FIGS. 1-4.

[0165] The metal contact 150 may be formed to surround the outer circumferential surface of the second epitaxial layer 126. The metal contact 150 may completely surround the outer surface of the second epitaxial layer 126 which faces the inner surface being in contact with the first epitaxial layer 125 with respect to the second epitaxial layer 126. A portion of the metal contact 150 may directly contact the upper surface of the field insulating film 110. The metal contact 150 may surround the second epitaxial layer 126 with a constant thickness. For example, the thickness of the metal contact 150 which wraps around the lower portion of the second epitaxial layer 126 may be substantially the same as the thickness of the metal contact 150 which wraps around the upper portion of the second epitaxial layer 126. However, the inventive concepts are not limited thereto.

[0166] The semiconductor device 3 may be operated as a PMOS transistor. The first epitaxial layer 125 may, for example, contain SiGe, and the second epitaxial layer 126 may, for example, contain Si or SiC. However, the inventive concepts are not limited thereto.

[0167] Similarly to the aforementioned semiconductor device 1a, the semiconductor device 3 may reduce the contact resistance and may further reduce the size of the contact. Thus, the performance of the semiconductor device may be improved.

[0168] FIG. 9 is a cross-sectional view illustrating a semiconductor device 4 according to still another embodiment of the inventive concepts. For convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiment will be omitted, and the differences will mainly be described.

[0169] Referring to FIG. 9, the semiconductor device 4 may operate in substantially the same manner as the semiconductor device 1a that is described above with reference to FIGS. 1 to 4.

[0170] However, in the case of the semiconductor device 4, the first epitaxial layer 128 may surround the side walls and the upper surface of the first fin-type pattern F1. The upper surface of the first fin-type pattern F1 which overlaps the first epitaxial layer 128 may be disposed on the same plane as the upper surface of the first fin-type pattern F1 which overlaps the gate structure 140. Thus, the first epitaxial layer 128 may be formed along the periphery of the first fin-type pattern F1.

[0171] As described above, the metal contact 150 may surround the outer circumferential surface of the first epitaxial layer 128. The metal contact 150 may surround the first epitaxial layer 128 with a constant thickness, and a part of the metal contact 150 may be in contact with the upper surface of the field insulating film 110.

[0172] FIG. 10 is a layout diagram illustrating a semiconductor device 11 according to still another embodiment of the inventive concepts. FIGS. 11, 12 and 13 are cross-sectional views taken along the lines D-D, E-E and F-F, respectively, of the semiconductor device of FIG. 10. FIG. 12 is substantially the same as FIG. 3, and FIG. 13 is substantially the same as FIG. 4. Thus, for convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiment will be omitted, and the differences will mainly be described.

[0173] Referring to FIGS. 10 to 13, the semiconductor device 11 includes a substrate 100, a first fin-type pattern F1, a second fin-type pattern F2, a gate structure 240, a first epitaxial layer 220a, a second epitaxial layer 220b, a metal contact 250 and an interlayer insulating film 270.

[0174] The first fin-type pattern F1 may extend on the substrate 100 along a first direction X1. Similarly, the second fin-type pattern F2 may extend on the same substrate 100 along the first direction X1. The first fin-type pattern F1 and the second fin-type pattern F2 may be spaced apart from each other. The first fin-type pattern F1 and the second fin-type pattern F2 may be a part of the substrate 100, and may include an epitaxial layer which is grown from the substrate 100.

[0175] The gate structure 240 may be formed on the first fin-type pattern F1 and on the second fin-type pattern F2 in a direction that intersects the first fin-type pattern F1 and the second fin-type pattern F2. For example, the gate structure 240 may extend along a third direction Y1 that intersects the first direction X1. The gate structure 240 may include a gate insulating film 241, a gate electrode 242, spacers 245 and the like which are sequentially formed on the first fin-type pattern F1 and the second fin-type pattern F2.

[0176] The first epitaxial layer 220a may be formed on the first fin-type pattern F1 on at least one side of the gate structure 240. The first epitaxial layer 220a may be formed on both sides of the gate structure 240. The first epitaxial layer 220a may contact the side surface of the spacer 245.

[0177] Similarly, the second epitaxial layer 220b may be formed on the second fin-type pattern F2 on at least one side of the gate structure 240. The second epitaxial layer 220b may be formed on both sides of the gate structure 240. The second epitaxial layer 220b may contact the side surface of the spacer 245. The first epitaxial layer 220a and the second epitaxial layer 220b may operate as the source/drains of the semiconductor device 11.

[0178] The first epitaxial layer 220a and the second epitaxial layer 220b may be spaced apart from each other, may contain the same material, and may have the same shape. However, the inventive concepts are not limited thereto.

[0179] The interlayer insulating film 270 may be formed on the semiconductor substrate 100. The interlayer insulating film 270 may cover the gate structure 240, the first epitaxial layer 220a and the second epitaxial layer 220b. However, the interlayer insulating film 270 may not be in direct contact with the first epitaxial layer 220a or the second epitaxial layer 220b.

[0180] The metal contact 250 may surround the outer circumferential surfaces of the first epitaxial layer 220a and the second epitaxial layer 220b. For example, referring to FIG. 11, the metal contact 250 may simultaneously and completely surround the outer surface of the first epitaxial layer 220a and the outer surface of the second epitaxial layer 220b except for the bottom surfaces that are on the respective first and second fin-type patterns F1 and F2. A part of the metal contact 250 may directly contact the upper surface of the field insulating film 110. Further, portions of the metal contact 250 that surround the first epitaxial layer 220a and the second epitaxial layer 220b may have the same thickness. However, the inventive concepts are not limited thereto.

[0181] As the metal contact 250 completely surrounds all but the respective bottom surfaces of the first epitaxial layer 220a and the second epitaxial layer 220b, the interlayer insulating film 270 may be spaced apart from the first epitaxial layer 220a and the second epitaxial layer 220b. The metal contact 250 may be formed within a first trench 274 which penetrates the interlayer insulating film 270.

[0182] Referring to FIG. 12, the metal contact 250 may include a first portion 250a and a second portion 250b. The second portion 250b may be formed on top of the first portion 250a, and the second portion 250b and the first portion 250a may be integrally formed. The first portion 250a may directly contact the upper surfaces of the first epitaxial layer 220a and the second epitaxial layer 220b, and may directly contact the side walls of the gate structure 240. The second portion 250b may be spaced apart from the side walls of the gate structure 240. The interlayer insulating film 270 may be between the second portion 250b and the gate structure 240.

[0183] At the interface between the first portion 250a and the second portion 250b, the width of the first portion 250a may be greater than the width of the second portion 250b. The first portion 250a and the second portion 250b may include the same material. However, the inventive concepts are not limited thereto.

[0184] In addition, referring to FIG. 11, a protruding area 215 may be formed between the metal contact 250 and the field insulating film 110.

[0185] Specifically, the protruding area 215 may be located between the first epitaxial layer 220a, the second epitaxial layer 220b and the field insulating film 110. The protruding area 215 may comprise the same material as the interlayer insulating film 270. However, the inventive concepts are not limited thereto.

[0186] The protruding area 215 may correspond to a depletion area that is formed below the dummy epitaxial layer in the process of manufacturing the semiconductor device 11. The protruding area 215 may completely overlap the field insulating film 110.

[0187] The semiconductor device 11 includes a metal contact 250 that may completely surround all but the bottom surfaces of the respective first and second epitaxial layers 220a, 220b. This configuration may reduce or minimize the contact resistance between the metal contact 250 and the respective first and second epitaxial layers 220a, 220b.

[0188] In addition, in the semiconductor device 11, the first epitaxial layer 220a and the second epitaxial layer 220b may be surrounded by the metal contact 250, while maintaining an epitaxially grown original form.

[0189] As the metal contact 250 surrounds the first epitaxial layer 220a and the second epitaxial layer 220b while maintaining the original form, the contact resistance of the semiconductor device 11 may be reduced, and the size of the contact may also be reduced. Thus, performance of the semiconductor device may be improved.

[0190] FIGS. 14A and 14B are cross-sectional views illustrating semiconductor devices 12a and 12b according to further embodiments of the inventive concepts. For convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiment will be omitted, and the differences will mainly be described.

[0191] Referring to be 14A and FIG. 14B, the semiconductor devices 12a, 12b may operate in substantially the same manner as the semiconductor device 11 that is described above with reference to FIGS. 10 to 13.

[0192] However, the first epitaxial layer 221a and the second epitaxial layer 221b of the semiconductor devices 12a, 12b may be formed so as to be in contact with each other. The first epitaxial layer 221a and the second epitaxial layer 221b may be integrally formed, and they may include the same material. The metal contact 250 may surround the outer circumferential surfaces of the first epitaxial layer 221a and the second epitaxial layer 221b.

[0193] Further, referring to FIG. 14A, in the semiconductor device 12a, a protruding area 216 may be formed between the first epitaxial layer 221a, the second epitaxial layer 221b and the field insulating film 110. This protruding area 216 may be filled with the same material that is used to form the metal contact 250.

[0194] However, the inventive concepts are not limited thereto. For example, referring to FIG. 14B, in the semiconductor device 12b, the protruding area 217 may include an air gap. That is, a depletion layer may be formed in the protruding area 217.

[0195] FIG. 15 is a cross-sectional view illustrating a semiconductor device 13 according to still another embodiment of the inventive concepts. For convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiment will be omitted, and the differences will mainly be described.

[0196] Referring to FIG. 15, the semiconductor device 13 may operate in substantially the same manner as the semiconductor device 11 that is described above with reference to FIGS. 10 to 13.

[0197] However, the metal contact 250 of the semiconductor device 13 may surround only the outer surfaces of the upper parts of the first epitaxial layer 221a and the second epitaxial layer 221b, and the interlayer insulating film 270 may surround the outer surfaces of the lower parts of the first epitaxial layer 221a and the second epitaxial layer 221b.

[0198] In the manufacturing process of the semiconductor device 13, a first trench 275 exposes only the upper parts of the first epitaxial layer 221a and the second epitaxial layer 221b. As the metal contact 250 is formed in the first trench 275, as illustrated in FIG. 15, the metal contact 250 only contacts the upper surfaces of the first epitaxial layer 221a and the second epitaxial layer 221b. The interlayer insulating film 270 contacts the side surfaces of the lower parts of the first epitaxial layer 221a and the second epitaxial layer 221b.

[0199] Although the metal contact 250 partially surrounds the first epitaxial layer 221a and the second epitaxial layer 221b, the semiconductor device 13 may operate in substantially the same manner as the semiconductor device 11 that is described above.

[0200] A protruding area 218 of the semiconductor device 13 may be filled with the interlayer insulating film 270, but the inventive concepts are not limited thereto.

[0201] FIG. 16 is a cross-sectional view illustrating a semiconductor device 14 according to still another embodiment of the inventive concepts. For convenience of description, hereinafter, repeated description of the same matters as in the aforementioned embodiment will be omitted, and the differences will mainly be described.

[0202] Referring to FIG. 16, the semiconductor device 14 may operate in substantially the same manner as the semiconductor device 11 that is described above with reference to FIGS. 10 to 13.

[0203] However, the semiconductor device 14 may further include a third epitaxial layer 226 that completely surrounds the outer circumferential surfaces of the first epitaxial layer 225a and the second epitaxial layer 225b. The third epitaxial layer 226 may comprise a material that is different from the material used to form the first epitaxial layer 225a and the second epitaxial layer 225b.