Systems And Methods For Refreshing A Memory Bank While Accessing Another Memory Bank Using A Shared Address Path

Lee; Joosang

U.S. patent application number 16/100443 was filed with the patent office on 2019-02-14 for systems and methods for refreshing a memory bank while accessing another memory bank using a shared address path. The applicant listed for this patent is MICRON TECHNOLOGY INC.. Invention is credited to Joosang Lee.

| Application Number | 20190051347 16/100443 |

| Document ID | / |

| Family ID | 63208123 |

| Filed Date | 2019-02-14 |

| United States Patent Application | 20190051347 |

| Kind Code | A1 |

| Lee; Joosang | February 14, 2019 |

SYSTEMS AND METHODS FOR REFRESHING A MEMORY BANK WHILE ACCESSING ANOTHER MEMORY BANK USING A SHARED ADDRESS PATH

Abstract

A system includes multiple memory banks that store data. The system also includes an address path coupled to the memory banks that provides a row address to the memory banks. The system further includes a command address input circuit coupled to the address path that refreshes a first set of memory banks via the address path and, when the command address input circuit refreshes the first set of memory banks, activates a row of a second set of memory banks to store the data or read the data from the row of the second set of memory banks via the address path.

| Inventors: | Lee; Joosang; (Frisco, TX) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 63208123 | ||||||||||

| Appl. No.: | 16/100443 | ||||||||||

| Filed: | August 10, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15676424 | Aug 14, 2017 | 10061541 | ||

| 16100443 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G06F 3/0673 20130101; G06F 3/0659 20130101; G11C 8/12 20130101; G11C 2211/4063 20130101; G11C 7/10 20130101; G11C 11/40618 20130101; G11C 2211/406 20130101; G11C 11/40611 20130101; G06F 3/0619 20130101 |

| International Class: | G11C 11/406 20060101 G11C011/406; G11C 8/12 20060101 G11C008/12 |

Claims

1. A system comprising: a plurality of memory banks configured to store data, wherein the plurality of memory banks comprises a first set of memory banks and a second set of memory banks; an address path coupled to the plurality of memory banks, wherein the address path is configured to provide a row address to the plurality of memory banks; and a command address input circuit coupled to the address path, wherein the command address input circuit is configured to refresh the first set of memory banks via the address path and, when the command address input circuit refreshes the first set of memory banks, activate a row of the second set of memory banks to store the data or read the data from the row of the second set of memory banks via the address path.

2. The system of claim 1, wherein the command address input circuit is configured to refresh the second set of memory banks via the address path and, when the command address input circuit refreshes the second set of memory banks, activate a second row of the first set of memory banks to store the data or read the data from the row of the first set of memory banks via the address path.

3. The system of claim 1, wherein the command address input circuit is configured to refresh the plurality of memory banks of the semiconductor device by outputting a first row address of the first set of memory banks to be refreshed or a second row address of the second set of memory banks to be refreshed to the address path.

4. The system of claim 1, wherein the command address input circuit is configured to refresh the first set of memory banks of the semiconductor device by outputting a row address of the first set of memory banks to be refreshed to the address path.

5. The system of claim 1, wherein the command address input circuit is configured to refresh the second set of memory banks of the semiconductor device by outputting a row address of the second set of memory banks to be refreshed to the address path.

6. A row address output circuit configured to: receive a first row address of a first set of memory banks of a plurality of memory banks, a second row address of a second set of memory banks of the plurality of memory banks, and a selection signal; output the first row address when the selection signal is associated with refreshing the plurality of memory banks or refreshing the first set of memory banks; and output the second row address when the selection signal is associated with refreshing the plurality of memory banks or refreshing the second set of memory banks, wherein the first set of memory banks is configured to be refreshed during activation of the second row of the second set of memory banks, wherein the second set of memory banks is configured to be refreshed during activation of the first row of the first set of memory banks.

7. The row address output circuit of claim 6, wherein the row address output circuit is configured to: receive a third row address associated with a first row of the first set of memory banks or a second row of the second set of memory banks; and output the third row address when the selection signal is associated with activating the first row of the first set of memory banks or the second row of the second set of memory banks.

8. The row address output circuit of claim 6, wherein the row address output circuit is configured to increment the first row address and increment the second row address when the selection signal is associated with refreshing the plurality of memory banks and the first row address is the same as the second row address.

9. The row address output circuit of claim 6, wherein the row address output circuit is configured to increment the second row address when the selection signal is associated with refreshing the plurality of memory banks and the first row address is greater than the second row address.

10. The row address output circuit of claim 6, wherein the row address output circuit is configured to increment the first row address when the selection signal is associated with refreshing the plurality of memory banks and the first row address is less than the second row address.

11. The row address output circuit of claim 6, wherein the row address output circuit is configured to increment the first row address when the selection signal is associated with refreshing the first set of memory banks and the first row address is less than or equal to the second row address.

12. The row address output circuit of claim 6, wherein the row address output circuit is configured to increment the second row address when the selection signal is associated with refreshing the second set of memory banks and the second row address is less than or equal to the second row address.

13. A method comprising: receiving a command at a semiconductor device to refresh at least some memory banks of a plurality of memory banks of the semiconductor device; when the command is configured to refresh the plurality of memory banks of the semiconductor device, outputting a first row address of a first set of memory banks of the plurality of memory banks or a second row address of a second set of memory banks of the plurality of memory banks to be refreshed; when the command is configured to refresh the first set of memory banks and not the second set of memory banks, outputting the first row address of the first set of memory banks; and when the command is configured to refresh the second set of memory banks and not the first set of memory banks, outputting the second row address of the first set of memory banks.

14. The method of claim 13, wherein, when the command is configured to refresh the first set of memory banks and not the second set of memory banks, the command is configured to refresh a plurality of rows of the first set of memory banks.

15. The method of claim 13, wherein, when the command is configured to refresh the plurality of memory banks of the semiconductor device and the first row address is the same as the second row address, incrementing the first row address and incrementing the second row address.

16. The method of claim 13, wherein, when the command is configured to refresh the plurality of memory banks of the semiconductor device and the first row address is greater than the second row address, incrementing the second row address and not incrementing the first row address.

17. The method of claim 13, wherein, when the command is configured to refresh the plurality of memory banks of the semiconductor device and the first row address is less than the second row address, incrementing the first row address and not incrementing the second row address.

18. The method of claim 13, wherein, when the command is configured to refresh the first set of memory banks and not the second set of memory banks and the first row address is less than or equal to the second row address, incrementing the first row address.

19. The method of claim 13, wherein, when the command is configured to refresh the second set of memory banks and not the first set of memory banks and the second row address is less than or equal to the first row address, incrementing the second row address.

20. The method of claim 13, comprising: receiving a second command to activate a row of the first set of memory banks; receiving and outputting a third row address associated with the row of the first set of memory banks, wherein the second set of memory banks is configured to be refreshed during activation of the row of the first set of memory banks.

21. The method of claim 13, comprising: receiving a second command to activate a row of the second set of memory banks; receiving and outputting a third row address associated with the row of the second set of memory banks, wherein the first set of memory banks is configured to be refreshed during activation of the row of the second set of memory banks.

Description

CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a Continuation of U.S. Patent Application No. 15/676,424, filed on Aug. 14, 2017, entitled "Systems and Methods for Refreshing a Memory Bank While Accessing Another Memory Bank Using a Shared Address Path," which is herein incorporated by reference.

BACKGROUND

Field of the Present Disclosure

[0002] Embodiments of the present disclosure relate generally to the field of semiconductor devices. More specifically, embodiments of the present disclosure relate to refreshing a first memory bank of the semiconductor device while accessing a second memory bank of the semiconductor device using a shared address path.

Description of Related Art

[0003] A semiconductor memory device, such as a dynamic random-access memory (DRAM), may refresh a memory cell by periodically reading information from the memory cell and rewriting the read information to the memory cell to preserve the information. For example, each bit of memory data in the memory may be stored as a presence or absence of an electric charge on a capacitor on the memory. As time passes, the electric charge may leak and eventually be lost, unless the data is refreshed. As such, external circuitry may periodically read each memory cell and rewrite the data to the memory cell, restoring the charge on the capacitor to its original level. A memory refresh cycle may refresh a group or area (such as a bank) of memory cells at one time, and each successive cycle may refresh a next group or area of memory cells, thus refreshing all memory cells in the memory. This refresh process may be conducted by a controller of the memory device and/or by a user periodically to keep data in the memory cells.

[0004] A memory may include multiple memory banks of memory cells. If a memory bank is being refreshed, then that memory bank may not be accessed (e.g., for read and/or write operations). Some DRAMs, such as a DDR5 SDRAM (double data rate type five synchronous dynamic random access memory), may be capable of refreshing only some memory banks, while enabling access to other memory banks.

[0005] Refreshing or accessing a memory bank may be performed by providing a row address on a single address path to the memory circuitry to be refreshed or accessed. The row address to be refreshed may be stored and maintained in a counter (e.g., in the memory) that may be incremented after each time the row address is transmitted to the register. The row address to be accessed may be provided via an external device (e.g., an external controller), along with, for example, an activate command. In either case, the row address may be transmitted and stored in a register of the memory, and the command address input circuit or command decoder may transmit a command to refresh or access the memory bank. Bank control blocks coupled to the memory banks may then perform a refresh or access operation based on the row address stored in the register.

[0006] However, the command address input circuit or command decoder may transmit a command that performs multiple refresh operations on one or more rows of a first memory bank (including the row address stored in the register). In some embodiments, a single command (e.g., issued externally from the first memory bank) may perform multiple refresh operations on multiple rows of the first memory bank consecutively. Each refresh operation may be performed within a given refresh time (t.sub.RFC). One of these multiple refresh operations may be performed at or near approximately the same time as when an activate operation (e.g., to read from or write to a row) is performed on a second memory bank by storing an activate row address in the register (thus possibly overwriting the row address stored in the register for the refresh operation). As such, either the refresh operation may be performed on the wrong row address (i.e., the row address of the second memory bank to be activated) or the activate operation may be performed on the wrong row address (i.e., the row address of the first memory bank to be refreshed).

[0007] Embodiments of the present disclosure may be directed to one or more of the problems set forth above.

BRIEF DESCRIPTION OF DRAWINGS

[0008] FIG. 1 is a simplified block diagram illustrating certain features of a memory device, according to an embodiment of the present disclosure;

[0009] FIG. 2 is a schematic diagram of a row address output circuit of a command address input circuit of the memory device of FIG. 1, according to an embodiment of the present disclosure;

[0010] FIG. 3 is an example timing diagram illustrating bank control blocks performing a command that performs one refresh operation on one or more rows of all memory banks of the memory device of FIG. 1 using a shared address path, according to an embodiment of the present disclosure;

[0011] FIG. 4 is an example timing diagram illustrating bank control blocks performing a command that performs multiple refresh operations on one or more rows of all memory banks of the memory device of FIG. 1 using a shared address path, according to an embodiment of the present disclosure;

[0012] FIG. 5 is an example timing diagram illustrating bank control blocks performing a command that performs one refresh operation on one or more rows of a set (e.g., even or odd) of memory banks of the memory device of FIG. 1 using a shared address path, according to an embodiment of the present disclosure;

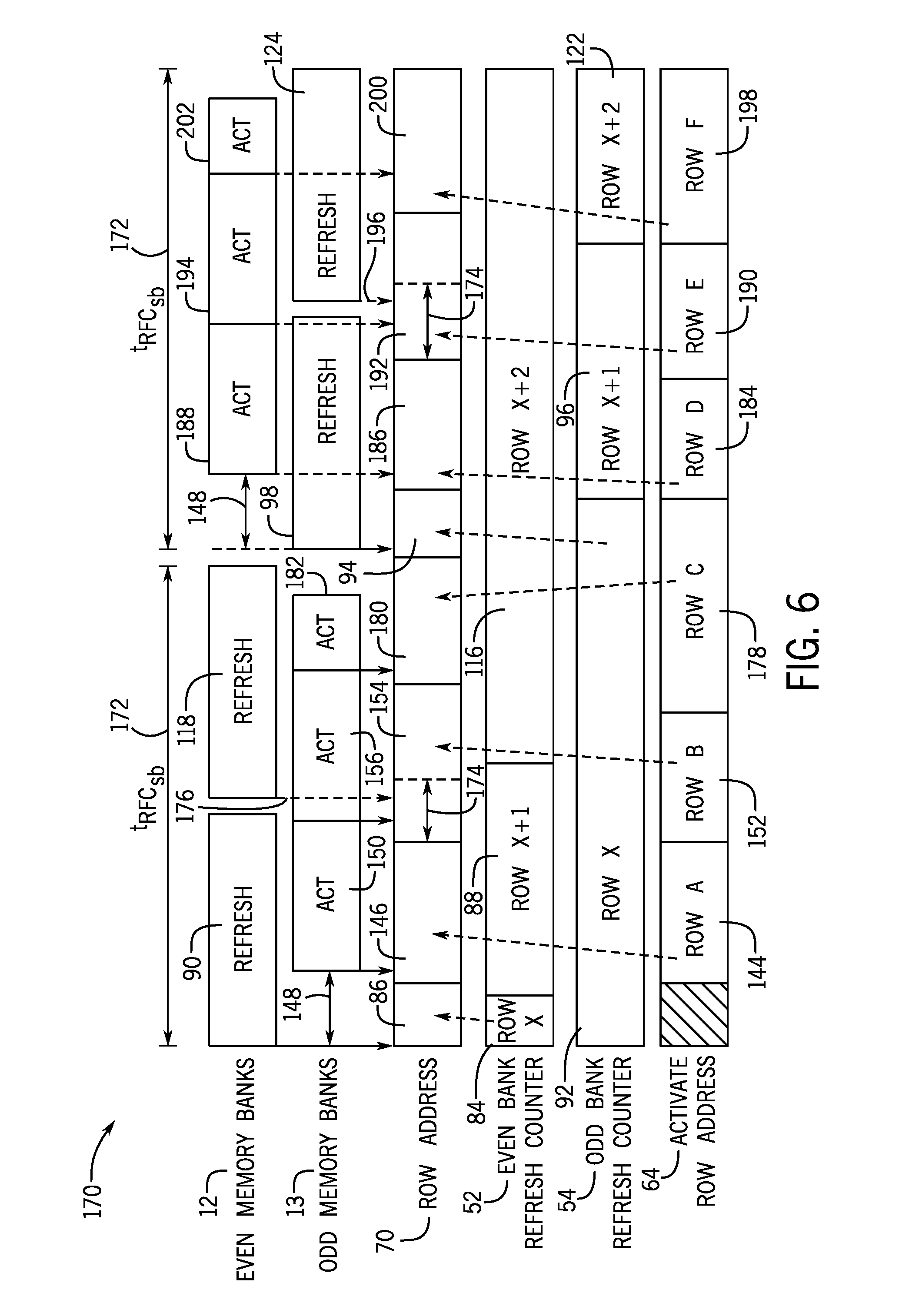

[0013] FIG. 6 is an example timing diagram illustrating bank control blocks performing a command that performs multiple refresh operations on one or more rows of a set (e.g., even or odd) of memory banks of the memory device of FIG. 1 using a shared address path, according to an embodiment of the present disclosure;

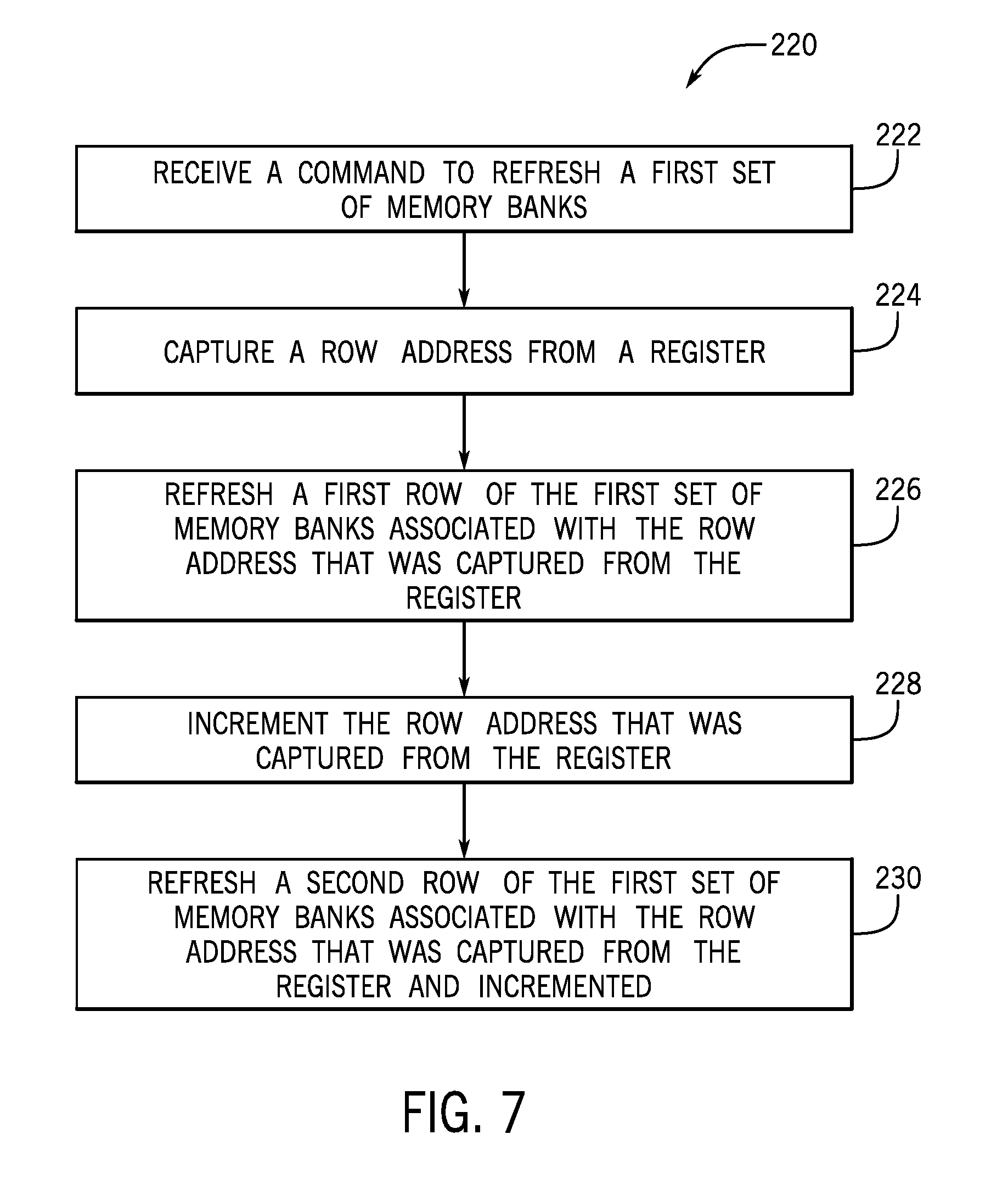

[0014] FIG. 7 is a flow diagram of a method for refreshing a first set of memory banks of the memory device of FIG. 1 while activating a row of a second set of the memory banks using a shared address path, according to an embodiment of the present disclosure; and

[0015] FIG. 8 is a flow diagram of a method for maintaining synchronization of rows in bank refresh counters of the memory device 10 of FIG. 1 using a shared address path, according to an embodiment of the present disclosure.

DETAILED DESCRIPTION

[0016] One or more specific embodiments will be described below. In an effort to provide a concise description of these embodiments, not all features of an actual implementation are described in the specification. It should be appreciated that in the development of any such actual implementation, as in any engineering or design project, numerous implementation-specific decisions must be made to achieve the developers' specific goals, such as compliance with system-related and business-related constraints, which may vary from one implementation to another. Moreover, it should be appreciated that such a development effort might be complex and time consuming, but would nevertheless be a routine undertaking of design, fabrication, and manufacture for those of ordinary skill having the benefit of this disclosure.

[0017] As described in detail below, when a command performs multiple refresh operations on one or more rows of a first set of memory banks, a first set of bank control blocks may capture a row address stored in a register, refresh a first set of rows of the first set of memory banks corresponding to the row address that was captured from the register, increment the captured row address (as opposed to capturing a subsequent row address stored in the register), and refresh a second set of rows of the first set of memory banks corresponding to the row address that captured from the register and incremented. During refresh of the first and second set of rows of the first set of memory banks, a second set of bank control blocks may activate the second set of memory banks. In this manner, the memory device may refresh a first set of memory banks while activating a row of a second set of memory banks to access (e.g., read data from or write data to) the row of the second set of memory banks, while preventing a wrong row of the first set of memory banks from being refreshed or a wrong row of the second memory banks from being activated (and vice versa).

[0018] Moreover, a row address output circuit in a memory device may receive a command. When the command refreshes all memory banks of the memory device (e.g., a REF.sub.ab command), the row address output circuit outputs a first row address (e.g., stored in a first counter) of a first set of memory banks to be refreshed or a second row address (e.g., stored in a second counter) of a second set of memory banks to be refreshed. Both counters may then be incremented (e.g., to a next row address of the memory banks to be refreshed) if the first row address is the same as the second row address. Otherwise, the second counter is incremented when the first row address is greater than the second row address, and the first counter is incremented when the second row address is greater than the first row address.

[0019] When the command refreshes the first set of memory banks (e.g., a REF.sub.sb command), the row address output circuit outputs the first row address stored in the first counter. The first counter may then be incremented (e.g., to a next row address of the first set of memory banks to be refreshed) if the first row address is less than or equal to the second row address. When the command refreshes the second set of memory banks, the row address output circuit outputs the second row address stored in the second counter. The second counter may then be incremented (e.g., to a next row address of the second set of memory banks to be refreshed) if the second row address is less than or equal to the first row address. When the command activates a first row of the first set of memory banks, the row address output circuit receives and outputs a third row address associated with the first row (e.g., to be read or written to), while the second set of memory banks may be refreshed. Again, the second counter may then be incremented if the second row address is less than or equal to the first row address. Similarly, when the command is configured to activate a second row of the second set of memory banks, the row address output circuit receives and outputs a fourth row address associated with the second row (e.g., to be read or written to), while the first set of memory banks may be refreshed. The first counter may then be incremented if the first row address is less than or equal to the second row address. In this manner, synchronization or pairing of the rows in the memory banks being refreshed may be enforced or maintained.

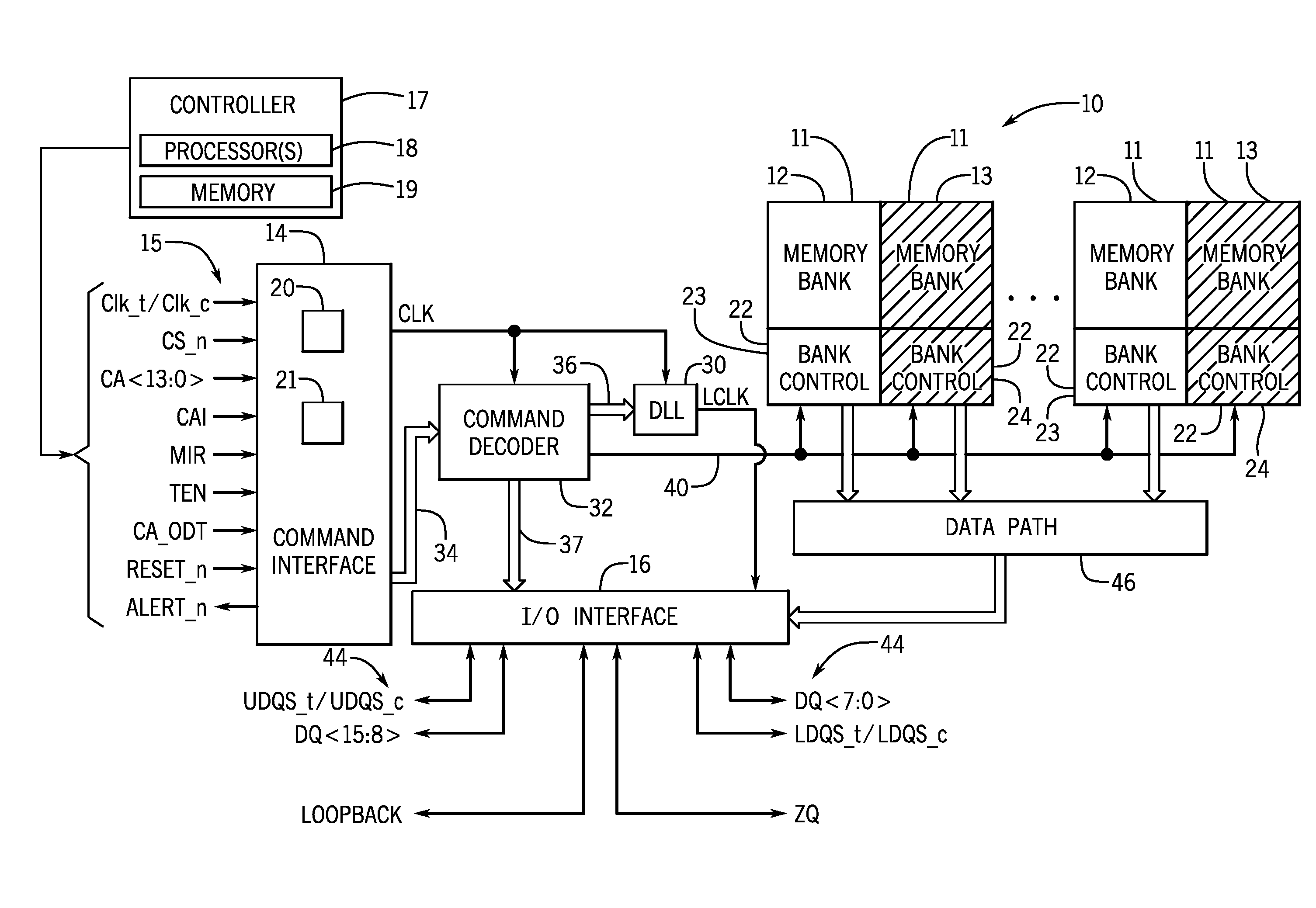

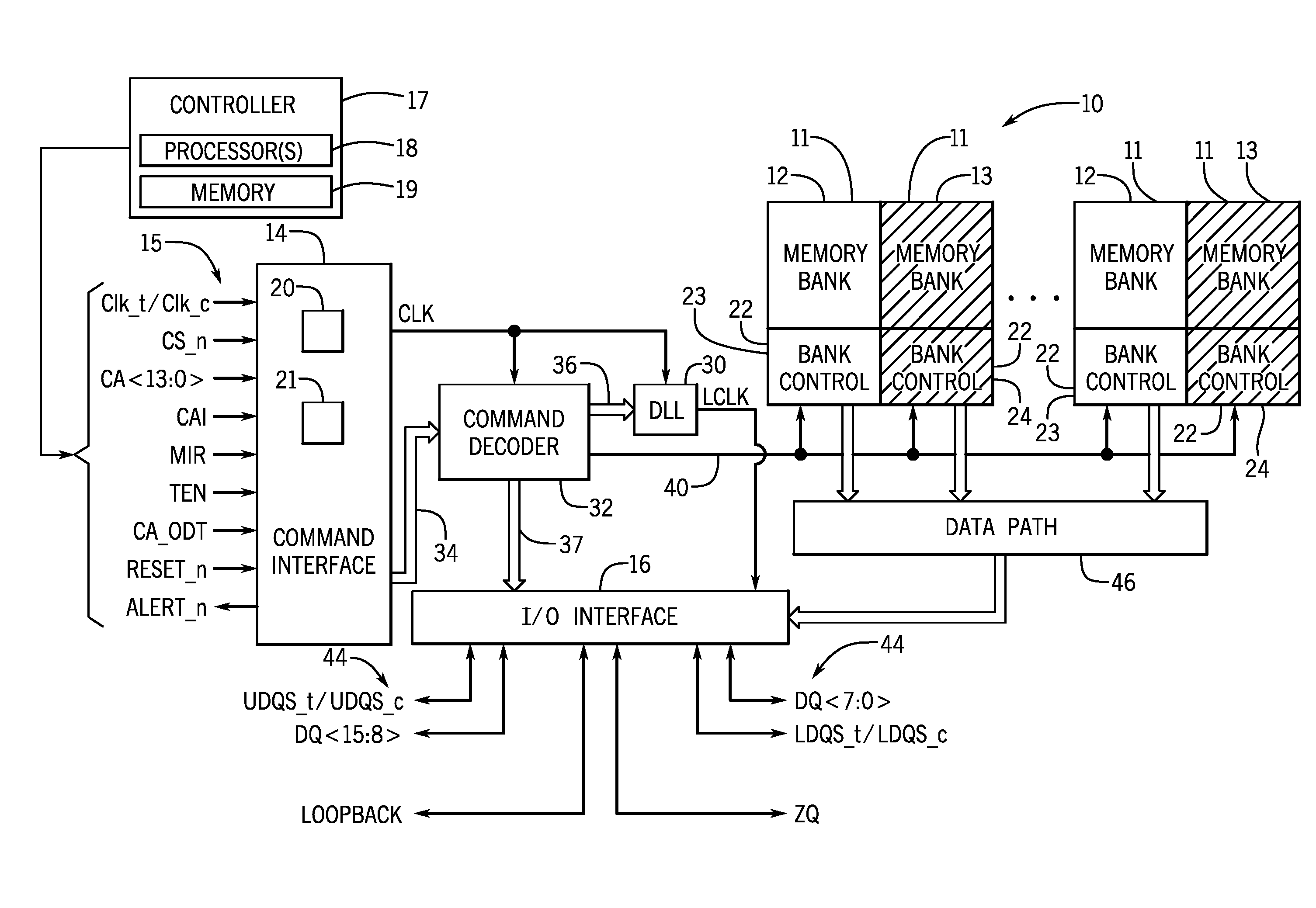

[0020] Turning now to the figures, FIG. 1 is a simplified block diagram illustrating certain features of a semiconductor device (e.g., a memory device 10), according to an embodiment of the present disclosure. Specifically, the block diagram of FIG. 1 is a functional block diagram illustrating certain functionality of the memory device 10. In accordance with one embodiment, the memory device 10 may be a double data rate type five synchronous dynamic random access memory (DDR5 SDRAM) device. Various features of DDR5 SDRAM allow for reduced power consumption, more bandwidth and more storage capacity compared to prior generations of DDR SDRAM. While the present disclosure uses the memory device 10 as an example, it should be understood that embodiments of the present disclosure are envisioned to apply to any suitable semiconductor device, such as integrated circuits, transistors, processors, microprocessors, and the like.

[0021] The memory device 10, may include a number of memory banks 11. The memory banks 11 may be DDR5 SDRAM memory banks, for instance. The memory banks 11 may be provided on one or more chips (e.g., SDRAM chips) that are arranged on dual inline memory modules (DIMMS). Each DIMM may include a number of SDRAM memory chips (e.g., x8 or x16 memory chips), as will be appreciated. Each SDRAM memory chip may include one or more memory banks 11. The memory device 10 represents a portion of a single memory chip (e.g., SDRAM chip) having a number of memory banks 11. For DDR5, the memory banks 11 may be further arranged to form bank groups. For instance, for an 8 gigabit (Gb) DDR5 SDRAM, the memory chip may include 16 memory banks 11, arranged into 8 bank groups, each bank group including 2 memory banks. For a 16 Gb DDR5 SDRAM, the memory chip may include 32 memory banks 11, arranged into 8 bank groups, each bank group including 4 memory banks, for instance. Various other configurations, organization and sizes of the memory banks 11 on the memory device 10 may be utilized depending on the application and design of the overall system. For example, the memory banks 11 may be divided into sets of memory banks 11, such as even memory banks 12 and odd memory banks 13. It should be understood that references in the present disclosure to the even memory banks 12 should apply equally to the odd memory banks 13, and vice versa.

[0022] The memory device 10 may include a command interface 14 and an input/output (I/O) interface 16. The command interface 14 may include processing and/or interface circuitry configured to provide a number of signals (e.g., signals 15) from an external device, such as a controller 17. The controller 17 may include processing circuitry, such as one or more processors 18 (e.g., one or more microprocessors), that may execute software programs to, for example, provide various signals 15 to the memory device 10 to facilitate the transmission and receipt of data to be written to or read from the memory device 10. Moreover, the processor(s) 18 may include multiple microprocessors, one or more "general-purpose" microprocessors, one or more special-purpose microprocessors, and/or one or more application specific integrated circuits (ASICS), or some combination thereof. For example, the processor(s) 18 may include one or more reduced instruction set (RISC) processors. The controller 17 may couple to one or more memories 19 that may store information such as control logic and/or software, look up tables, configuration data, etc. In some embodiments, the processor(s) 18 and/or the memory 19 may be external to the controller 17. The memory 19 may include a tangible, non-transitory, machine-readable-medium, such as a volatile memory (e.g., a random access memory (RAM)) and/or a nonvolatile memory (e.g., a read-only memory (ROM), flash memory, a hard drive, or any other suitable optical, magnetic, or solid-state storage medium, or a combination thereof). The memory 19 may store a variety of information and may be used for various purposes. For example, the memory 19 may store machine-readable and/or processor-executable instructions (e.g., firmware or software) for the processor(s) 18 to execute, such as instructions for providing various signals 15 to the memory device 10 to facilitate the transmission and receipt of data to be written to or read from the memory device 10. As such, the controller 17 may provide various signals 15 to the memory device 10 to facilitate the transmission and receipt of data to be written to or read from the memory device 10.

[0023] As will be appreciated, the command interface 14 may include a number of circuits, such as a clock input circuit 20 and a command address input circuit 21, for instance, to ensure proper handling of the signals 15. The command interface 14 may receive one or more clock signals from an external device. Generally, double data rate (DDR) memory utilizes a differential pair of system clock signals, referred to herein as the true clock signal (Clk_t/) and the complementary clock signal (Clk_c). The positive clock edge for DDR refers to the point where the rising true clock signal Clk_t/crosses the falling complementary clock signal Clk_c, while the negative clock edge indicates that transition of the falling true clock signal Clk_t and the rising of the complementary clock signal Clk_c. Commands (e.g., read command, write command, etc.) are typically entered on the positive edges of the clock signal and data is transmitted or received on both the positive and negative clock edges.

[0024] The I/O interface 16 may include processing and/or interface circuitry configured to manage and/or perform input/output operations between the memory device 10 and any suitable external device coupled to the I/O interface 16.

[0025] The clock input circuit 20 receives the true clock signal (Clk_t/) and the complementary clock signal (Clk_c) and generates an internal clock signal CLK. The internal clock signal CLK is supplied to an internal clock generator, such as a delay locked loop (DLL) circuit 30. The internal clock generator 30 generates a phase controlled internal clock signal LCLK based on the received internal clock signal CLK. The phase controlled internal clock signal LCLK is supplied to the I/O interface 16, for instance, and is used as a timing signal for determining an output timing of read data.

[0026] The internal clock signal CLK may also be provided to various other components within the memory device 10 and may be used to generate various additional internal clock signals. For instance, the internal clock signal CLK may be provided to a command decoder 32. The command decoder 32 may receive command signals from the command bus 34 and may decode the command signals to provide various internal commands. For instance, the command decoder 32 may provide command signals to the internal clock generator 30 over the bus 36 to coordinate generation of the phase controlled internal clock signal LCLK. The command decoder 32 may also provide command signals to the I/O interface 16 over bus 37 to facilitate receiving and transmitting I/O signals. The phase controlled internal clock signal LCLK may be used to clock data through the 10 interface 16, for instance.

[0027] Further, the command decoder 32 may decode commands, such as read commands, write commands, mode-register set commands, activate commands, etc., and provide access to a particular memory bank 11 corresponding to the command, via a bus path 40. As will be appreciated, the memory device 10 may include various other decoders, such as row decoders and column decoders, to facilitate access to the memory banks 11. In one embodiment, each memory bank 11 includes a bank control block 22 which provides the necessary decoding (e.g., row decoder and column decoder), as well as other features, such as timing control and data control, to facilitate the execution of commands to and from the memory banks 11. In particular, the bus path 40 may include a row address path that may provide a row address (e.g., sent from the command decoder 32 or one or more counters coupled to the row address path) to the bank control blocks 22 so that the bank control blocks 22 may perform operations on a row corresponding to the row address. The path 40 may be shared by both the command decoder 32 sending a row address on the path 40 to be activated, as well as the counters sending a row address on the path 40 to be refreshed. Similar to the memory banks 11, the bank control blocks 22 may also be divided into sets of bank control blocks 22, such as even bank control blocks 23 associated with the even memory banks 12 and odd bank control blocks 24 associated with the odd memory banks 13. It should be understood that references in the present disclosure to the even bank control blocks 23 should apply equally to the odd bank control blocks 24, and vice versa.

[0028] The memory device 10 executes operations, such as read commands and write commands, based on the command/address signals received from an external device, such as a processor. In one embodiment, the command/address bus may be a 14-bit bus to accommodate the command/address signals (CA<13:0>). The command/address signals are clocked to the command interface 14 using the clock signals (Clk_t/ and Clk_c). The command interface may include a command address input circuit 21 which is configured to receive and transmit the commands to provide access to the memory banks 11, through the command decoder 32, for instance. In addition, the command interface 14 may receive a chip select signal (CS_n). The CS_n signal enables the memory device 10 to process commands on the incoming CA<13:0> bus. Access to specific banks 11 within the memory device 10 is encoded on the CA<13:0> bus with the commands.

[0029] In addition, the command interface 14 may be configured to receive a number of other command signals. For instance, a command/address on die termination (CA_ODT) signal may be provided to facilitate proper impedance matching within the memory device 10. A reset command (RESET_n) may be used to reset the command interface 14, status registers, state machines and the like, during power-up for instance. The command interface 14 may also receive a command/address invert (CAI) signal which may be provided to invert the state of command/address signals CA<13:0> on the command/address bus, for instance, depending on the command/address routing for the particular memory device 10. A mirror (MIR) signal may also be provided to facilitate a mirror function. The MIR signal may be used to multiplex signals so that they can be swapped for enabling certain routing of signals to the memory device 10, based on the configuration of multiple memory devices in a particular application. Various signals to facilitate testing of the memory device 10, such as the test enable (TEN) signal, may be provided, as well. For instance, the TEN signal may be used to place the memory device 10 into a test mode for connectivity testing.

[0030] The command interface 14 may also be used to provide an alert signal (ALERT_n) to the system processor or controller for certain errors that may be detected. For instance, an alert signal (ALERT_n) may be transmitted from the memory device 10 if a cyclic redundancy check (CRC) error is detected. Other alert signals may also be generated. Further, the bus and pin for transmitting the alert signal (ALERT_n) from the memory device 10 may be used as an input pin during certain operations, such as the connectivity test mode executed using the TEN signal, as described above.

[0031] Data may be sent to and from the memory device 10, utilizing the command and clocking signals discussed above, by transmitting and receiving data signals 44 through the IO interface 16. More specifically, the data may be sent to or retrieved from the memory banks 11 over the data path 46, which may include multiple data paths or bi-directional data buses. Data IO signals, generally referred to as DQ signals, are generally transmitted and received in one or more bi-directional data busses. For certain memory devices, such as a DDR5 SDRAM memory device, the IO signals may be divided into upper and lower bytes. For instance, for a x16 memory device, the IO signals may be divided into upper and lower TO signals (e.g., DQ<15:8> and DQ<7:0>) corresponding to upper and lower bytes of the data signals, for instance.

[0032] To allow for higher data rates within the memory device 10, certain memory devices, such as DDR memory devices may utilize data strobe signals, generally referred to as DQS signals. The DQS signals are driven by the external processor or controller sending the data (e.g., for a write command) or by the memory device 10 (e.g., for a read command). For read commands, the DQS signals are effectively additional data output (DQ) signals with a predetermined pattern. For write commands, the DQS signals are used as clock signals to capture the corresponding input data. As with the clock signals (Clk_t/ and Clk_c), the data strobe (DQS) signals may be provided as a differential pair of data strobe signals (DQS_t/ and DQS_c) to provide differential pair signaling during reads and writes. For certain memory devices, such as a DDR5 SDRAM memory device, the differential pairs of DQS signals may be divided into upper and lower data strobe signals (e.g., UDQS_t/ and UDQS_c; LDQS_t/ and LDQS_c) corresponding to upper and lower bytes of data sent to and from the memory device 10, for instance.

[0033] An impedance (ZQ) calibration signal may also be provided to the memory device 10 through the TO interface 16. The ZQ calibration signal may be provided to a reference pin and used to tune output drivers and ODT values by adjusting pull-up and pull-down resistors of the memory device 10 across changes in process, voltage and temperature (PVT) values. Because PVT characteristics may impact the ZQ resistor values, the ZQ calibration signal may be provided to the ZQ reference pin to be used to adjust the resistance to calibrate the input impedance to known values. As will be appreciated, a precision resistor is generally coupled between the ZQ pin on the memory device 10 and GND/VSS external to the memory device 10. This resistor acts as a reference for adjusting internal ODT and drive strength of the IO pins.

[0034] In addition, a loopback signal (LOOPBACK) may be provided to the memory device 10 through the IO interface 16. The loopback signal may be used during a test or debugging phase to set the memory device 10 into a mode wherein signals are looped back through the memory device 10 through the same pin. For instance, the loopback signal may be used to set the memory device 10 to test the data output (DQ) of the memory device 10. Loopback may include both a data and a strobe or possibly just a data pin. This is generally intended to be used to monitor the data captured by the memory device 10 at the IO interface 16.

[0035] As will be appreciated, various other components such as power supply circuits (for receiving external VDD and VSS signals), mode registers (to define various modes of programmable operations and configurations), read/write amplifiers (to amplify signals during read/write operations), temperature sensors (for sensing temperatures of the memory device 10), etc., may also be incorporated into the memory system 10. Accordingly, it should be understood that the block diagram of FIG. 1 is only provided to highlight certain functional features of the memory device 10 to aid in the subsequent detailed description.

[0036] With the foregoing in mind, FIG. 2 is a schematic diagram of a row address output circuit 50 of the command address input circuit 21 of the memory device 10 of FIG. 1, according to an embodiment of the present disclosure. As illustrated, the row address output circuit 50 includes an even bank refresh counter 52 and an odd bank refresh counter 54. It should be understood that references to the even bank refresh counter 52 in the present disclosure may apply equally to the odd bank refresh counter 54, and vice versa.

[0037] The even bank refresh counter 52 may store a row address associated with a first set of memory banks (e.g., the even memory banks 12) of the memory device 10 to be refreshed. The even bank refresh counter 52 may increment the stored row address when the row address output circuit 50 receives a REF.sub.ab (refresh all memory banks) command 56 or a REF.sub.sb(Even) (refresh some memory banks--even) command 58. The REF.sub.ab command 56 may be transmitted (e.g., by the command interface 14, the external controller 17, or the like) to refresh all memory banks 11, while the REF.sub.sb(Even) command 58 may be transmitted to each even bank control block 23 of the memory device 10 to refresh the even memory banks 12 (e.g., separately from the odd memory banks 13). In either case, in response to receiving the REF.sub.ab command 56 or the REF.sub.sb(Even) command 58, each even bank control block 23 may refresh the row address identified by the even bank refresh counter 52 of a respective even memory bank 12 (e.g., corresponding to the even bank control block 23).

[0038] Similarly, the odd bank refresh counter 54 may store a row address associated with a second set of memory banks (e.g., the odd memory banks 13) of the memory device 10 to be refreshed. The odd bank refresh counter 54 may increment the stored row address when the row address output circuit 50 receives a REF.sub.ab (refresh all memory banks) command 56 or a REF.sub.sb(Odd) (refresh some memory banks--odd) command 60. The REF.sub.sb(Odd) command 60 may be transmitted to each odd bank control block 24 of the memory device 10 to refresh the odd memory banks 13 (e.g., separately from the even memory banks 12). In either case, in response to receiving the REF.sub.ab command 56 or the REF_sb(Odd) command 60, each odd bank control block 24 may refresh the row address identified by the odd bank refresh counter 54 of a respective odd memory bank 13 (e.g., corresponding to the odd bank control block 24).

[0039] While the even bank refresh counter 52 may store a row address associated with the even memory banks 12 and the odd bank refresh counter 54 may store a row address associated with the odd memory banks 13, it should be understood that the even bank refresh counter 52 may not be dedicated to the even memory banks 12 and the odd bank refresh counter 54 may not be dedicated to the odd memory banks 13. That is, the even bank refresh counter 52 and the odd bank refresh counter 54 may be interchanged, e.g., independent of the contents of the even memory banks 12 and the odd memory banks 13.

[0040] A multiplexer 62 of the row address output circuit 50 may accept as inputs the row address stored in the even bank refresh counter 52, the row address stored in the odd bank refresh counter 54, and an activate row address 64 (e.g., associated with a read or write operation). The multiplexer 62 may output one of these inputs based on a selection signal 66. The selection signal 66 may indicate whether the command sent to the row address output circuit 50 is, for example, the REF.sub.ab command 56, the REF.sub.sb(Even) command 58, the REF.sub.sb(Odd) command 60, an activate command, or the like. The multiplexer 62 may then output the row address stored in the even bank refresh counter 52, the row address stored in the odd bank refresh counter 54, or the activate row address 64 to a register 68 that stores the output as row address 70. The row address 70 may then be captured (e.g., by bank control blocks 22) to perform refresh and/or access (e.g., read/write) operations in the even memory banks 12, the odd memory banks 13, or both.

[0041] The bank control blocks 22 may perform any suitable number of refresh operations on any suitable number of rows of respective memory banks 11 (e.g., corresponding to the bank control blocks 22) per refresh command. For example, if the memory device 10 is operating in an FGR (Fine Granularity Refresh) 2x mode, a single refresh command may refresh one or more rows of a memory bank 11. If the memory device is operating in an FGR lx mode, a single refresh command may perform two refresh operations on two sets of rows of a memory bank 11. As explained below, when a single refresh command performs more than one (e.g., two) refresh operations, one of the refresh operations may be performed at approximately the same time as an activate command, resulting in the refresh operation being performed on the wrong row address or the activate command being performed on the wrong row address.

[0042] FIG. 3 is an example timing diagram 80 illustrating the bank control blocks 22 performing the REF.sub.ab command 56 that performs one refresh operation on one or more rows of all memory banks 11 of the memory device 10 of FIG. 1 using a shared address path 40, according to an embodiment of the present disclosure. In particular, the memory device 10 may be operating in the FGR 2x mode. Each refresh operation performed by the REF.sub.ab command 56 may take t.sub.RFCab ns (nanoseconds) 82. For example, in the case of the memory device 10 operating in the FGR 2x mode, t.sub.RFCab 82 may be approximately on the order of 100 ns. In response to receiving the REF.sub.ab command 56 (e.g., at the command decoder 32), the even control blocks 23 may refresh the even memory banks 12 while (e.g., simultaneously) the odd control blocks 24 refresh the odd memory banks 13. Because the even memory banks 12 and the odd memory banks 13 are being refreshed during the REF.sub.ab command 56, no memory banks 11 of the memory device 10 may be activated (e.g., for read/write operations).

[0043] For example, in response to receiving the REF.sub.ab command 56, the row address output circuit 50 may output the row address (i.e., Row X 84) in the even bank refresh counter 52 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 86) to perform a refresh operation. Both the even bank refresh counter 52 and the odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X 84, 92 to Row X+1 88, 96) to account for Row X 84 of the even memory banks 12 and the odd memory banks 13 being refreshed. The even control blocks 23 and the odd control blocks 24 may capture the row address 70 (i.e., Row X 84) and refresh 90, 98 the row address 70 in the even memory banks 12 and the odd memory banks 13.

[0044] In additional or alternative embodiments, in response to receiving the REFab command 56, the row address output circuit 50 may output the row address (i.e., Row X 92) in the odd bank refresh counter 54 instead of the even bank refresh counter 52 on the shared address path 40 to store in the register 68 as the row address 70. Again, both the even bank refresh counter 52 and the odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X 84, 92 to Row X+1 88, 96) to account for Row X 92 of the even memory banks 12 and the odd memory banks 13 being refreshed.

[0045] While the example described in the timing diagram 80 of FIG. 3 illustrates one row (e.g., Row X 84) of the even memory banks 12 and the odd memory banks 13 being refreshed, it should be understood that multiple rows of the even memory banks 12 and the odd memory banks 13 may instead or also be refreshed. In this manner, the bank control blocks 22 may refresh one or more rows of all memory banks 11 of the memory device 10 of FIG. 1 in response to each REFab command 56 performing one refresh operation.

[0046] FIG. 4 is an example timing diagram 110 illustrating the bank control blocks 22 performing the REFab command 56 by performing multiple refresh operations on one or more rows of all memory banks 11 of the memory device 10 of FIG. 1 using the shared address path 40, according to an embodiment of the present disclosure. In particular, the memory device 10 may be operating in the FGR lx mode. As such, the bank control blocks 22 may perform two refresh operations on all memory banks 11 of the memory device 10 in response to each REF.sub.ab command 56. However, it should be understood that the bank control blocks 22 may perform any suitable number of refresh operations of all memory banks 11 of the memory device 10. As illustrated, the two refresh operations refresh two rows of the memory banks 11. However, it should be understood that the bank control blocks 22 may refresh any suitable number of rows of all memory banks 11 of the memory device 10. Each refresh operation performed by the REF.sub.ab command 56 may take t.sub.RFcab ns (nanoseconds) 112. For example, in the case of the memory device 10 operating in the FGR 1x mode, t.sub.RFcab 112 may be approximately on the order of 195 ns. In response to receiving the REFab command 56 (e.g., at the command decoder 32), the even control blocks 23 may first refresh the even memory banks 12 while (e.g., simultaneously) the odd control blocks 24 refresh the odd memory banks 13. As mentioned above, because the even memory banks 12 and the odd memory banks 13 are being refreshed during the REF.sub.ab command 56, no memory banks 11 of the memory device 10 may be activated (e.g., for read/write operations).

[0047] For example, in response to receiving the REF.sub.ab command 56, the row address output circuit 50 may output the row address (i.e., Row X 84) in the even bank refresh counter 52 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 86) to be captured to perform refresh and/or access (e.g., read/write) operations. The even bank refresh counter 52 and the odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X 84, 92 to Row X+1 88, 96). The even control blocks 23 and the odd control blocks 24 may capture the row address 70 (i.e., Row X 84) and refresh 90 the row address 70 in the even memory banks 12 and the odd memory banks 13.

[0048] When the register 68 is available to store a new row address 70, the row address output circuit 50 may then output the incremented row address (i.e., Row X+1 88) in the even bank refresh counter 52 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 114) to be captured to perform a refresh operation. The even bank refresh counter 52 and the odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X+1 88, 96 to Row X+2 116, 122). The even control blocks 23 and the odd control blocks 24 may capture the row address 70 (i.e., Row X+1 88) and refresh 118, 124 the row address 70 in the even memory banks 12 and the odd memory banks 13.

[0049] In additional or alternative embodiments, in response to receiving the REFab command 56, the row address output circuit 50 may output the row address (i.e., Row X 92) in the odd bank refresh counter 54 instead of the even bank refresh counter 52 on the shared address path 40 to store in the register 68 as the row address 70. Again, both the even bank refresh counter 52 and the odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X 84, 92 to Row X+1 88, 96) to account for Row X 92 of the even memory banks 12 and the odd memory banks 13 being refreshed.

[0050] In such embodiments, when the register 68 is available to store a new row address 70, the row address output circuit 50 may then output the incremented row address (i.e., Row X+1 96) in the odd bank refresh counter 54 on the shared address path 40 to store in the register 68 as the row address 70 to be captured to perform refresh and/or access (e.g., read/write) operations. The even bank refresh counter 52 and the odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X+1 88, 96 to Row X+2 116, 122). The even control blocks 23 and the odd control blocks 24 may capture the row address 70 (i.e., Row X+1 96) and refresh 118, 124 the row address 70 in the even memory banks 12 and the odd memory banks 13.

[0051] In this manner, the bank control blocks 22 may refresh multiple rows of all memory banks 11 of the memory device 10 of FIG. 1 in response to each REFab command 56 performing multiple refresh operations.

[0052] FIG. 5 is an example timing diagram 140 illustrating the bank control blocks 22 performing the REF.sub.sb command 58, 60 by performing one refresh operation on one or more rows of a set (e.g., even or odd) of memory banks 11 of the memory device 10 of FIG. 1 using the shared address path 40, according to an embodiment of the present disclosure. In particular, the memory device 10 may be operating in the FGR 2x mode. Each refresh operation performed by the REF.sub.sb command 58, 60 may take t.sub.RFCsb ns (nanoseconds) 142. For example, in the case of the memory device 10 operating in the FGR 2x mode, t.sub.RFCsb 142 may be approximately on the order of 100 ns. In response to receiving the REF.sub.sb(Even) command 58 (e.g., at the command decoder 32), the even control blocks 23 may refresh the even memory banks 12. Similarly, in response to receiving the REF.sub.sb(Odd) command 60 (e.g., at the command decoder 32), the odd control blocks 24 may refresh the odd memory banks 13. During a REF.sub.sb command 58, 60, while one set of memory banks 11 (e.g., the even memory banks 12) are being refreshed, another set of memory banks 11 (e.g., the odd memory banks 13) may be activated (e.g., for read/write operations).

[0053] For example, in response to receiving the REF.sub.sb(Even) command 58, the row address output circuit 50 may output the row address (i.e., Row X 84) in the even bank refresh counter 52 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 86) to be captured to perform a refresh operation. The even bank refresh counter 52 may then increment the stored row address (i.e., from Row X 84 to Row X+1 88). The even control blocks 23 may capture the row address 70 (i.e., Row X 84) and refresh 90 the row address 70 in the even memory banks 12.

[0054] While the refresh operation 90 is performed on the even memory banks 12 via the REF.sub.sb(Even) command 58, the odd memory banks 13 may be activated (e.g., for read/write operations). For example, in response to receiving an activate (ACT) command (e.g., at the command decoder 32), and when the register 68 is available to store a new row address 70, the row address output circuit 50 may output an activate row address 64 (i.e., Row A 144) of the odd memory banks 13 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 146) to be captured to perform an access (e.g., read/write) operation. After a delay time 148 (e.g., t.sub.RRD) associated with a delay between (consecutive) activations, one or more odd control blocks 24 may activate 150 the row address 70 (i.e., Row A 144) of one or more odd memory banks 13 to, for example, read from or write to the row address 70. In some embodiments, multiple activate commands may be received and multiple activations 150 may be performed while the refresh operation 90 is performed on the even memory banks 12 via the REF.sub.sb(Even) command 58 (e.g., depending on the delay 148, the time it takes to perform the activation 150, and the time it takes to perform the refresh operation 90).

[0055] In response to receiving the REF.sub.sb(Odd) command 60, and when the register 68 is available to store a new row address 70, the row address output circuit 50 may also output the row address (i.e., Row X 92) in the odd bank refresh counter 54 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 94) to be captured to perform a refresh operation. The odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X 92 to Row X+1 96). The odd control blocks 24 may capture the row address 70 (i.e., Row X 92) and refresh 98 the row address 70 in the odd memory banks 13.

[0056] While the refresh operation 98 is performed on the odd memory banks 13 via the REF.sub.sb(Odd) command 60, the even memory banks 12 may be activated (e.g., for read/write operations). For example, in response to receiving the activate command (e.g., at the command decoder 32), and when the register 68 is available to store a new row address 70, the row address output circuit 50 may output an activate row address 64 (i.e., Row B 152) of the even memory banks 12 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 154) to be captured to perform an access (e.g., read/write) operation. After a delay 148 (e.g., t.sub.RRD), one or more even control blocks 23 may activate 156 the row address 70 (i.e., Row B 152) of one or more even memory banks 12 to, for example, read from or write to the row address 70. In some embodiments, multiple activate commands may be received and multiple activations 156 may be performed while the refresh operation 98 is performed on the odd memory banks 13 via the REF.sub.sb(Odd) command 60 (e.g., depending on the delay 148, the time it takes to perform the activation 156, and the time it takes to perform the refresh operation 98).

[0057] While the example described in the timing diagram 140 of FIG. 5 illustrates one row (e.g., Row X 84) of the even memory banks 12 and the odd memory banks 13 being refreshed, it should be understood that multiple rows of the even memory banks 12 and the odd memory banks 13 may instead or also be refreshed. In this manner, the bank control blocks 22 may refresh one row of a set (e.g., even or odd) memory banks 11 of the memory device 10 of FIG. 1 in response to each REF.sub.sb command 58, 60 performing one refresh operation.

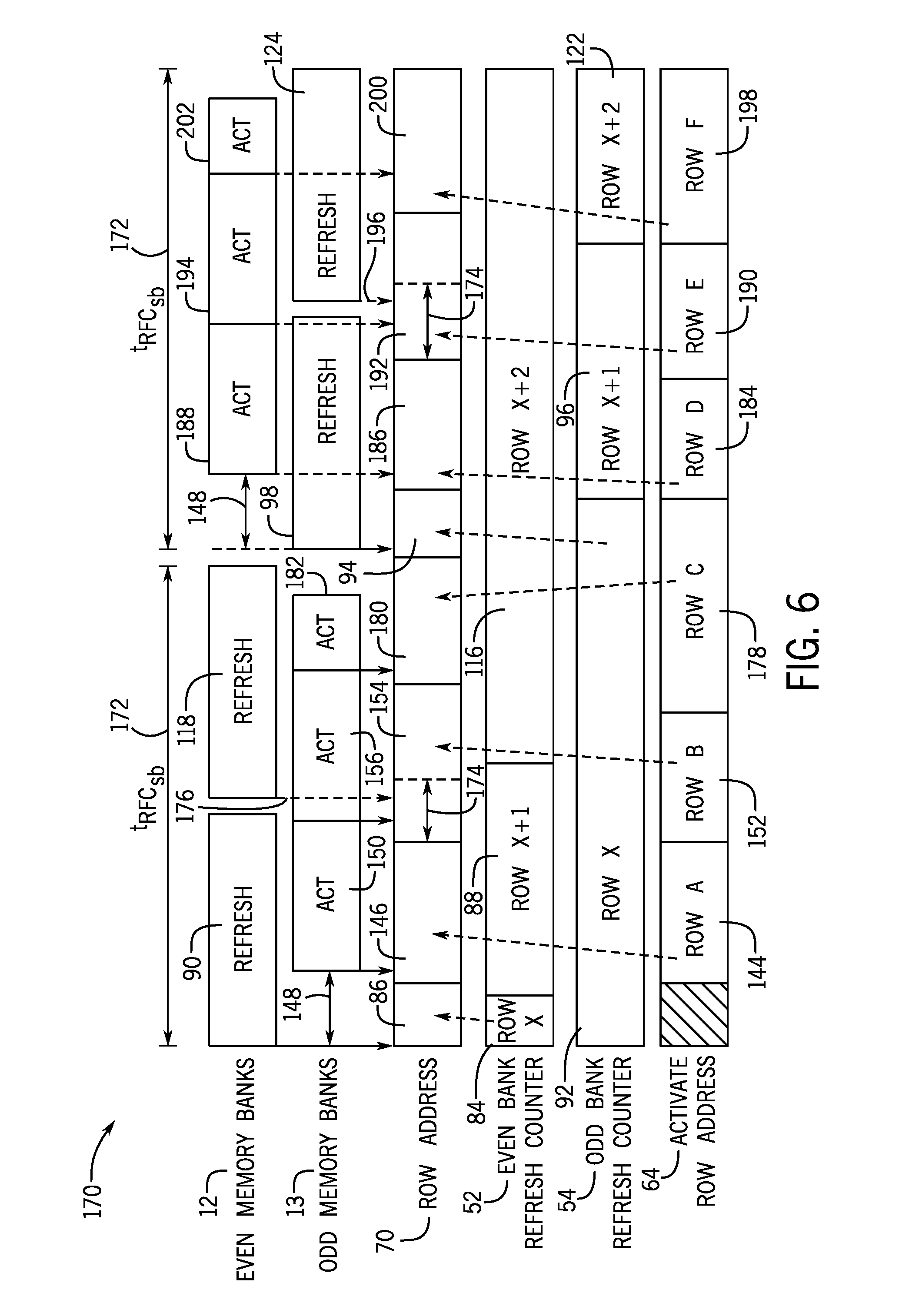

[0058] FIG. 6 is an example timing diagram 170 illustrating the bank control blocks 22 performing the REF.sub.sb command 58, 60 by performing multiple refresh operations on one or more rows of a set (e.g., even or odd) of memory banks 11 of the memory device 10 of FIG. 1 using the shared address path 40, according to an embodiment of the present disclosure. In particular, the memory device 10 may be operating in the FGR lx mode. As such, the bank control blocks 22 may perform two refresh operations on the even memory banks 12 or the odd memory banks 13 of the memory device 10 in response to each REF.sub.sb command 58, 60. However, it should be understood that the bank control blocks 22 may perform any suitable number of refresh operations of the even memory banks 12 or the odd memory banks 13 of the memory device 10. As illustrated, the two refresh operations refresh two rows of the even memory banks 12 or the odd memory banks 13. However, it should be understood that the bank control blocks 22 may refresh any suitable number of rows of the even memory banks 12 or the odd memory banks 13 of the memory device 10. Each refresh operation performed by the REF.sub.sb command 58, 60 may take t.sub.RFCsb ns (nanoseconds) 172 to complete. For example, in the case of the memory device 10 operating in the FGR 1x mode, t.sub.RFCsb 172 may be approximately on the order of 130 ns. In response to receiving the REF.sub.sb(Even) command 58 (e.g., at the command decoder 32), the even control blocks 23 may refresh the even memory banks 12. Similarly, in response to receiving the REF.sub.sb(Odd) command 60 (e.g., at the command decoder 32), the odd control blocks 24 may refresh the odd memory banks 13. During a REF.sub.sb command 58, 60, while one set of memory banks 11 (e.g., the even memory banks 12) are being refreshed, another set of memory banks 11 (e.g., the odd memory banks 13) may be activated (e.g., for read/write operations).

[0059] For example, in response to receiving the REF.sub.sb(Even) command 58, the row address output circuit 50 may output the row address (i.e., Row X 84) in the even bank refresh counter 52 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 86) to be captured to perform an access (e.g., read/write) operation. The even bank refresh counter 52 may then increment the stored row address (i.e., from Row X 84 to Row X+1 88). The even control blocks 23 may capture the row address 70 (i.e., Row X 84) and refresh 90 the row address 70 in the even memory banks 12.

[0060] While the first refresh operation 90 is performed on the even memory banks 12 via the REF.sub.sb(Even) command 58, the odd memory banks 13 may be activated (e.g., for read/write operations). For example, in response to receiving a first activate command (e.g., at the command decoder 32) corresponding to the odd memory banks 13 when the register 68 is available to store a new row address 70, the row address output circuit 50 may output a first activate row address 64 (i.e., Row A 144) of the odd memory banks 13 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 146) to be captured to perform an access (e.g., read/write) operation. After a delay time 148 (e.g., t.sub.RRD), one or more odd control blocks 24 may activate 150 the row address 70 (i.e., Row A 144) of one or more odd memory banks 13 to, for example, read from or write to the row address 70.

[0061] In some embodiments, multiple activate commands may be received and multiple activations 150 may be performed while the first refresh operation 90 is performed on the even memory banks 12 via the REF.sub.sb(Even) command 58. In some embodiments, the number of activate command and/or activations 150 may be based at least in part on the delay 148, the time it takes to perform the activation 150, and/or the time it takes to perform the first refresh operation 90. However, in the case of refreshing multiple rows of a set of memory banks 11, such as refreshing two rows of the even memory banks 12 or the odd memory banks 13 in response to a REF.sub.sb command 58, 60, a refresh operation of subsequent rows (e.g., a second row) may be performed at or near approximately the same time as an activate command. As a result, and because the shared address path 40 is used (e.g., instead of multiple address paths, where one address path might be used for a refresh operation and another for an activation operation), the wrong address may be captured, and either the refresh operation may be performed on the wrong row address (i.e., the row address of the memory bank to be activated) or the activation operation may be performed on the wrong row address (i.e., the row address of the memory banks to be refreshed). As such, instead of capturing the row address 70 to refresh (e.g., 118) subsequent rows (e.g., a second row) of a set of memory banks 11 (e.g., the even memory banks 12), the bank control blocks 22 (e.g., the even control blocks 23) associated with the set of memory banks 11 may internally increment the row address 70 captured during a first refresh operation (e.g., 90).

[0062] For example, while the first refresh operation 90 is performed on the even memory banks 12 via the REF.sub.sb(Even) command 58, the odd memory banks 13 may be activated a second time. In response to receiving a second activate command (e.g., at the command decoder 32) corresponding to the odd memory banks 13, and when the register 68 is available to store a new row address 70, the row address output circuit 50 may output a second activate row address 64 (i.e., Row B 152) of the odd memory banks 13 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 154) to be captured to perform an access (e.g., read/write) operation. After a delay 148 (e.g., t.sub.RRD), one or more odd control blocks 24 may activate 156 the row address 70 (i.e., Row B 152) of one or more odd memory banks 13 to, for example, read from or write to the row address 70.

[0063] In response to receiving the REF.sub.sb(Even) command 58, the row address output circuit 50 may output the row address (i.e., Row X+1 88) stored in the even bank refresh counter 52 on the shared address path 40 in an attempt to store Row X+1 88 in the register 68 as the row address 70 (i.e., at the portion 154) to be captured to perform refresh and/or access (e.g., read/write) operations. However, in some instances, the register 68 (e.g., for a duration of time 174) may not be available to store a new row address 70, and instead retains the stored row address (i.e., Row B 152). As such, if the even control blocks 23 capture the row address 70 to refresh 118 the row address 70 in the even memory banks 12, the even control blocks 23 may capture 176 the row address 70 (i.e., Row B 152) meant for activation in the odd memory banks 13 (instead of Row X+1 88). The even control blocks 23 may thus refresh a wrong row in the even memory banks 12.

[0064] Instead, rather than capturing 176 the row address 70 and refreshing that row address 70 of the even memory banks 12, the even bank control blocks 23 may internally increment the row address 70 (i.e., from Row X 84 to Row X+1) captured during the first refresh operation 90, and refresh 118 the internally incremented row address (i.e., Row X+1). In this manner, the memory device 10 may refresh the even memory banks 12 while activating a row of the odd memory banks 13, and prevent a wrong row of the even memory banks 12 from being refreshed and/or a wrong row of the odd memory banks 13 from being activated. The even bank refresh counter 52 may then increment the stored row address (i.e., from Row X+1 88 to Row X+2 116) to account for the internally incremented row address 70 associated with the even memory banks 12. To reduce complexity in the circuitry of the memory device 10, in some embodiments, the command interface 14, the command address input circuit 21, the command decoder 32, and/or the bank control blocks 22 may guarantee that the first refresh operation 90 is performed on an even row address 70 (i.e., Row X 84), such that the least significant bit of the even row address 70 is 0. This way, internally incrementing the row address 70 is simply a matter of flipping the least significant bit (to 1).

[0065] While the first refresh operation 90 is performed on the even memory banks 12 via the REF.sub.sb(Even) command 58, the odd memory banks 13 may be activated a third time. In response to receiving a third activate command (e.g., at the command decoder 32) corresponding to the odd memory banks 13, and when the register 68 is available to store a new row address 70, the row address output circuit 50 may output a third activate row address 64 (i.e., Row C 178) of the odd memory banks 13 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 180) to be captured to perform an access (e.g., read/write) operation. After a delay time 148 (e.g., t.sub.RRD) associated with a delay between (consecutive) activations, one or more odd control blocks 24 may activate 182 the row address 70 (i.e., Row C 178) of one or more odd memory banks 13 to, for example, read from or write to the row address 70.

[0066] In response to receiving the REF.sub.sb(Odd) command 60, the row address output circuit 50 may output the row address (i.e., Row X 92) in the odd bank refresh counter 54 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 94) to be captured to perform a refresh operation. As illustrated, if only a single counter (e.g., the even refresh counter 52) were used instead of two counters (e.g., the even refresh counter 52 and the odd refresh counter 54), the row address output circuit 50 might not be able to output the correct row (i.e., Row X). That is, because the even refresh counter 52 was incremented (e.g., to Row X+1 88) to prepare for the second refresh operation 118 for the even memory banks 12, it no longer stores the correct row (e.g., Row X) for the odd memory banks 13 to refresh. The odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X 92 to Row X+1 96). The odd control blocks 24 may capture the row address 70 (i.e., Row X 92) and refresh 98 the row address 70 in the odd memory banks 13.

[0067] While the first refresh operation 98 is performed on the odd memory banks 13 via the REF.sub.sb(Odd) command 60, the even memory banks 12 may be activated (e.g., for read/write operations). For example, in response to receiving a first activate command (e.g., at the command decoder 32) corresponding to the even memory banks 12, and when the register 68 is available to store a new row address 70, the row address output circuit 50 may output a first activate row address 64 (i.e., Row D 184) of the even memory banks 12 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 186) to be captured to perform an access (e.g., read/write) operation. After a delay 148 (e.g., t.sub.RRD), one or more even control blocks 23 may activate 188 the row address 70 (i.e., Row D 184) of one or more even memory banks 12 to, for example, read from or write to the row address 70.

[0068] While the first refresh operation 90 is performed on the odd memory banks 13 via the REF.sub.sb(Odd) command 60, the even memory banks 12 may be activated a second time. In response to receiving a second activate command (e.g., at the command decoder 32) corresponding to the even memory banks 12, and when the register 68 is available to store a new row address 70, the row address output circuit 50 may output a second activate row address 64 (i.e., Row E 190) of the even memory banks 12 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 192) to be captured to perform an access (e.g., read/write) operation. After a delay 148 (e.g., t.sub.RRD), one or more even control blocks 23 may activate 194 the row address 70 (i.e., Row D 184) of one or more even memory banks 12 to, for example, read from or write to the row address 70.

[0069] In response to receiving the REF.sub.sb(Odd) command 60, the row address output circuit 50 may output the row address (i.e., Row X+1 96) stored in the odd bank refresh counter 54 on the shared address path 40 in an attempt to store Row X+1 96 in the register 68 as the row address 70 (i.e., at the portion 186) to be captured to perform refresh and/or access (e.g., read/write) operations. However, in some instances, the register 68 (e.g., for a duration of time 174) may not be available to store a new row address 70, and instead retains the stored row address (i.e., Row D 184). As such, if the odd control blocks 24 capture the row address 70 to refresh 124 the row address 70 in the odd memory banks 13, the odd control blocks 24 may capture 196 the row address 70 (i.e., Row D 184) meant for activation in the even memory banks 12 (instead of Row X+1 96). The odd control blocks 24 may thus refresh a wrong row in the odd memory banks 13.

[0070] Instead, rather than capturing 196 the row address 70 and refreshing that row address 70 of the odd memory banks 13, the odd bank control blocks 24 may internally increment the row address 70 (i.e., from Row X 92 to Row X+1) captured during the first refresh operation 98, and refresh 124 the internally incremented row address (i.e., Row X+1). In this manner, the memory device 10 may refresh the odd memory banks 13 while activating a row of the even memory banks 12, and prevent a wrong row of the odd memory banks 13 from being refreshed or a wrong row of the even memory banks 12 from being activated. The odd bank refresh counter 54 may then increment the stored row address (i.e., from Row X+1 96 to Row X+2 122) to account for the internally incremented row address 70 associated with the odd memory banks 13. To reduce complexity in the circuitry of the memory device 10, in some embodiments, the command interface 14, the command address input circuit 21, the command decoder 32, and/or the bank control blocks 22 may guarantee that the first refresh operation 98 is performed on an even row address 70 (i.e., Row X 92), such that the least significant bit of the even row address 70 is 0. This way, internally incrementing the row address 70 is simply a matter of flipping the least significant bit (to 1).

[0071] While the first refresh operation 98 is performed on the odd memory banks 13 via the REF.sub.sb(Odd) command 60, the even memory banks 12 may be activated a third time. In response to receiving a third activate command (e.g., at the command decoder 32) corresponding to the even memory banks 12, and when the register 68 is available to store a new row address 70, the row address output circuit 50 may output a third activate row address 64 (i.e., Row F 198) of the even memory banks 12 on the shared address path 40 to store in the register 68 as the row address 70 (i.e., as shown in portion 200) to be captured to perform refresh and/or access (e.g., read/write) operations. After a delay 148 (e.g., t.sub.RRD), one or more even control blocks 23 may activate 202 the row address 70 (i.e., Row F 198) of one or more even memory banks 12 to, for example, read from or write to the row address 70.

[0072] In this manner, the memory device 10 may refresh a first set of memory banks 11 while activating a row of a second set of memory banks 11 to access (e.g., read data from or write data to) the row of the second set of memory banks 11, while preventing a wrong row of the first set of memory banks 11 from being refreshed or a wrong row of the second memory banks 11 from being activated (and vice versa). In some embodiments, when performing the REFab command 56 by performing multiple refresh operations of all memory banks 11 of the memory device 10 as shown in FIG. 4, rather than capturing the row address 70 and refreshing that row address 70 of the memory banks 11, the bank control blocks 22 may internally increment the row address 70 (e.g., Row X 84) captured during a first refresh operation (e.g., 90), and refresh (e.g., 118) the internally incremented row address (e.g., Row X+1).

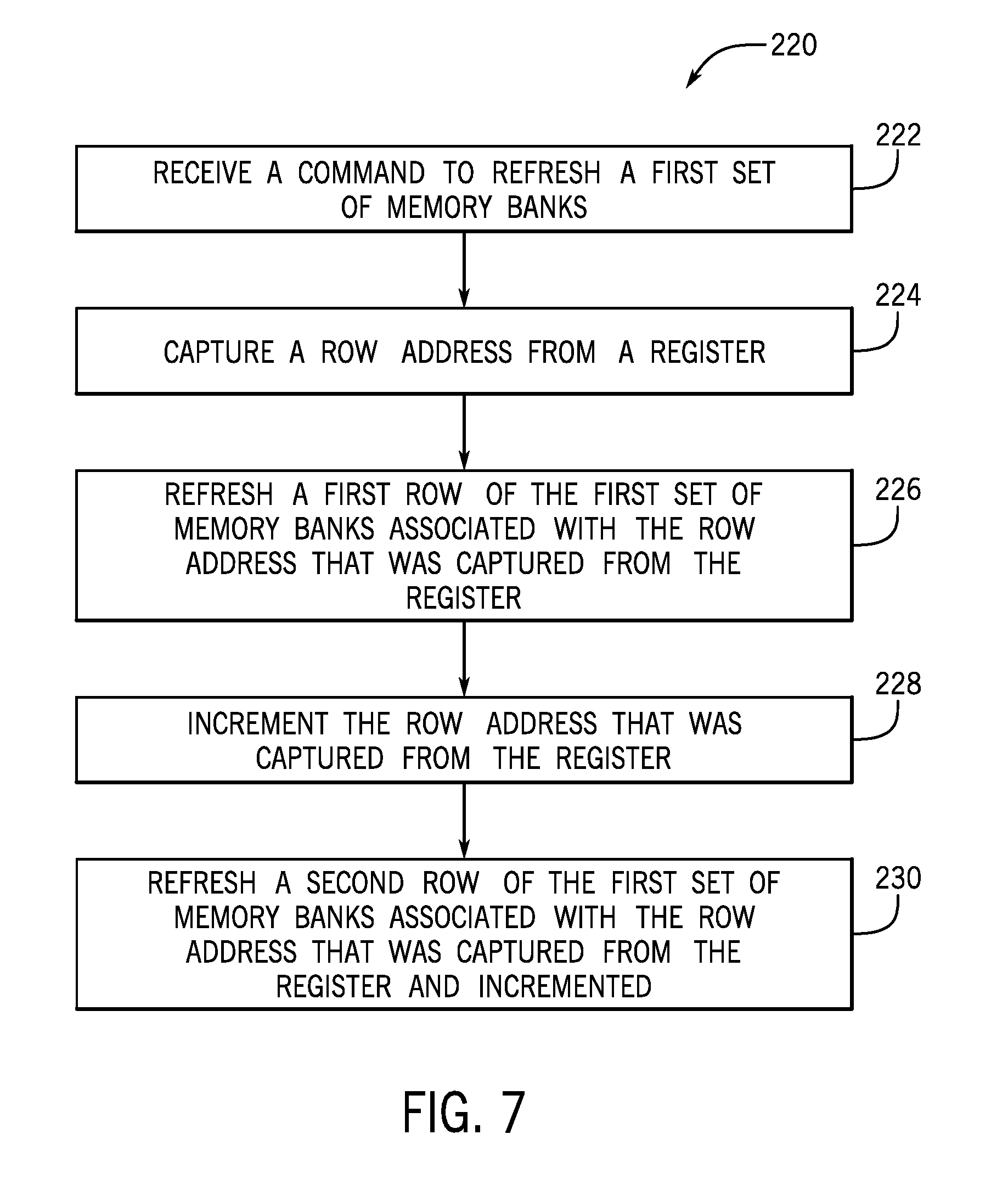

[0073] FIG. 7 is a flow diagram of a method 220 for refreshing a first set of memory banks 11 of the memory device 10 of FIG. 1 while activating a row of a second set of the memory banks 22 using a shared address path 40, according to an embodiment of the present disclosure. In particular, performing the method 220 may result in the example timing diagram 170 of FIG. 6. The method 220 may be performed by any suitable device or combination of devices that may capture a row address from a register (e.g., 68), increment the row address captured from the register, and refresh rows of the memory banks 11. While the method 220 is described using steps in a specific sequence, it should be understood that the present disclosure contemplates that the described steps may be performed in different sequences than the sequence illustrated, and certain described steps may be skipped or not performed altogether. In some embodiments, at least some of the steps of the method 220 may be performed by bank control blocks 22 of the memory device 10, as described below.

[0074] As illustrated, the bank control blocks 22 receive (process block 222) a command to refresh a first set (e.g., the even memory banks 12 or the odd memory banks 13) of memory banks 11. For example, the command may be the REF.sub.sb(Even) command 58 or the REF.sub.sb(Odd) command 60.

[0075] The bank control blocks (e.g., 23, 24) associated with the first set of memory banks 11 capture (process block 224) a row address 70 from a register 68 of the memory device 10. The register 68 may store an output of the multiplexer 62 of the row address output circuit 50 via the shared address path 40. As such, the register 68 may store the row address stored in the even bank refresh counter 52, the row address stored in the odd bank refresh counter 54, or the activate row address 64.

[0076] The bank control blocks associated with the first set of memory banks 11 refresh (process block 226) a first row of the first set of memory blocks associated with the row address 70 that was captured from the register 68. In particular, the first row of the first set of memory blocks may have an address that is the same as the row address 70 that was captured from the register 68.

[0077] The bank control blocks associated with the first set of memory banks 11 increment (process block 228) the row address 70 that was captured from the register 68. The row address 70 may be incremented internally, such that the row address 70 is stored and incremented in a memory device (e.g., a register) local to the bank control blocks 22. In particular, the row addresses stored in the even bank refresh counter 52 and the odd bank refresh counter 54 may not change when the row address 70 is incremented. However, the even bank refresh counter 52 or the odd bank refresh counter 54 may then increment their respective stored row addresses to account for the internally incremented row address 70.

[0078] The bank control blocks associated with the first set of memory banks 11 refresh (process block 230) a second row of the first set of memory blocks associated with the row address 70 that was captured from the register 68 and incremented. In particular, the second row of the first set of memory blocks may have an address that is the same as the row address 70 that was captured from the register 68 and incremented. In this manner, the bank control blocks 22 may refresh a first set of memory banks while activating a row of a second set of memory banks, and prevent a wrong row of the first set of memory banks from being refreshed and/or a wrong row of the second set of memory banks from being activated.

[0079] In some embodiments, synchronization or pairing of rows in the memory banks 11 being refreshed may be enforced or maintained. For example, the even bank refresh counter 52 and the odd bank refresh counter 54 may be synchronized or paired when they store the same row address. The even control blocks 23 may refresh the even memory banks 12 in response to receiving the REF.sub.sb(Even) command 58, and then the even bank refresh counter 52 may be incremented. If the memory device 10 is operating in the FGR lx mode, the even control blocks 23 may refresh two rows of the even memory banks 12, and the even bank refresh counter 52 may be incremented twice. If the memory device 10 is operating in the FGR 2x mode, the even control blocks 23 may refresh one row of the even memory banks 12, and the even bank refresh counter 52 may be incremented once. To enforce synchronization or pairing, the odd control blocks 24 may refresh the odd memory banks 13 in response to receiving the REF.sub.sb(Odd) command 60, and then the odd bank refresh counter 54 may be incremented. The even bank refresh counter 52 and the odd bank refresh counter 54 may then store the same row address.

[0080] However, in some instances, instead of the odd control blocks 24 receiving the REF.sub.sb(Odd) command 60, the even control blocks 23 may receive the REF.sub.sb(Even) command 58 again. To enforce synchronization or pairing, the even bank refresh counter 52 may not be incremented. Otherwise, the rows to be refreshed in the even memory banks 12 and the odd memory banks 13 may not align. Instead, when the next REF.sub.sb(Odd) command 60 is received, the odd bank refresh counter 54 may be incremented, and the even bank refresh counter 52 and the odd bank refresh counter 54 may store the same row address, and thus be aligned. Despite not incrementing the even bank refresh counter 52, the even control blocks 23 may still refresh the row address of the even memory banks 12 that was previously refreshed in response to receiving the REF.sub.sb(Even) command 58.

[0081] Additionally, in some instances, instead of the odd control blocks 24 receiving the REF.sub.sb(Odd) command 60, the control blocks 22 may receive the REF.sub.ab command 56. To enforce synchronization or pairing, the even bank refresh counter 52 may not be incremented, while the odd bank refresh counter 54 may be incremented. That way, the even bank refresh counter 52 and the odd bank refresh counter 54 may store the same row address, and thus be aligned. In some embodiments, before the odd bank refresh counter 54 is incremented, the row address register 68 may capture the row address in the odd bank refresh counter 54. Despite not incrementing the even bank refresh counter 52, both the even control blocks 23 and the odd control blocks 24 may refresh the even memory banks 12 and the odd memory banks 13, respectively, in response to receiving the REFab command 56. In this manner, synchronization or pairing of the rows in the memory banks 11 being refreshed may be enforced or maintained. In some embodiments, a threshold value may be used to limit desynchronization of the row addresses in the even bank refresh counter 52 and the odd bank refresh counter 54. In other words, this threshold value may indicate a maximum difference between the even bank refresh counter 52 and the odd bank refresh counter 54. For example, a threshold value of 1 may indicate that the even bank refresh counter 52 and the odd bank refresh counter 54 may not be incremented while storing a value greater than the other respective counter.