Semiconductor Device And Method Of Manufacturing The Same

HAYASHI; Kiyoshi

U.S. patent application number 15/698219 was filed with the patent office on 2017-12-28 for semiconductor device and method of manufacturing the same. The applicant listed for this patent is RENESAS ELECTRONICS CORPORATION. Invention is credited to Kiyoshi HAYASHI.

| Application Number | 20170373146 15/698219 |

| Document ID | / |

| Family ID | 55302749 |

| Filed Date | 2017-12-28 |

View All Diagrams

| United States Patent Application | 20170373146 |

| Kind Code | A1 |

| HAYASHI; Kiyoshi | December 28, 2017 |

SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

Abstract

A semiconductor device including a well resistance element of high accuracy and high withstand voltage and a method of manufacturing the semiconductor device are provided. The semiconductor device includes a semiconductor substrate, a well region, an input terminal, an output terminal, a separation insulating film, and an active region. The input terminal and the output terminal are electrically coupled to the well region. The separation insulating film is arranged to be in contact with the upper surface of the well region in an intermediate region between the input terminal and the output terminal. The active region is arranged to be in contact with the upper surface of the well region. The separation insulating film and the active region in the intermediate region have an elongated shape in plan view. In the intermediate region, a plurality of separation insulating films and a plurality of active regions are alternately and repeatedly arranged.

| Inventors: | HAYASHI; Kiyoshi; (Tokyo, JP) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 55302749 | ||||||||||

| Appl. No.: | 15/698219 | ||||||||||

| Filed: | September 7, 2017 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 14807757 | Jul 23, 2015 | 9786738 | ||

| 15698219 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 29/78 20130101; H01L 29/0692 20130101; H01L 27/0629 20130101; H01L 29/41758 20130101; H01L 21/76224 20130101; H01L 29/0653 20130101; H01L 29/1095 20130101; H01L 28/20 20130101 |

| International Class: | H01L 29/06 20060101 H01L029/06; H01L 27/06 20060101 H01L027/06; H01L 21/762 20060101 H01L021/762; H01L 49/02 20060101 H01L049/02; H01L 29/417 20060101 H01L029/417; H01L 29/10 20060101 H01L029/10 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Aug 13, 2014 | JP | 2014-164811 |

Claims

1. A method of manufacturing a semiconductor device, comprising the steps of: forming a plurality of grooves each having an elongated shape in plan view with a gap between them in a main surface of a semiconductor substrate by using a plurality of mask patterns; forming a separation insulating film by burying an insulating film into the groove; forming a well region in contact with a lower surface of the separation insulating film in the semiconductor substrate and an active region in contact with an upper surface of the well region; and forming an input terminal and an output terminal over the semiconductor substrate so as to be electrically coupled to the well region, wherein in an intermediate region between the input terminal and the output terminal, the separation insulating film and the active region have an elongated shape in plan view, and in the intermediate region, a plurality of the separation insulating films and a plurality of the active regions are formed so that the separation insulating film and the active region are alternately and repeatedly arranged.

2. The method of manufacturing a semiconductor device according to claim 1, wherein the step of forming the separation insulating film includes the steps of forming the insulating film to cover the mask patterns and fill the groove and removing the insulating film until the mask patterns are exposed, removing the insulating film located between a plurality of the mask patterns, and removing the mask patterns.

3. The method of manufacturing a semiconductor device according to claim 1, wherein the separation insulating film and the active region are formed so that uppermost surfaces of the separation insulating film and the active region are the same surface as the main surface of the semiconductor substrate.

4. The method of manufacturing a semiconductor device according to claim 1, wherein the separation insulating film in the intermediate region is formed to extend in a direction crossing a direction connecting the input terminal and the output terminal in plan view.

5. The method of manufacturing a semiconductor device according to claim 1, wherein the separation insulating film in the intermediate region is formed to extend in a direction along a direction connecting the input terminal and the output terminal in plan view.

6. The method of manufacturing a semiconductor device according to claim 5, wherein a plurality of the input terminals and a plurality of the output terminals are formed with a gap between them in plan view, and the separation insulating film in the intermediate region is formed to extend so as to reach a region sandwiched by a pair of the input terminals adjacent to each other in plan view among the plurality of input terminals and a region sandwiched by a pair of the output terminals adjacent to each other in plan view among the plurality of output terminals.

7. The method of manufacturing a semiconductor device according to claim 1, further comprising the step of: forming a contact region between the input terminal and the well region and between the output terminal and the well region.

8. The method of manufacturing a semiconductor device according to claim 1, further comprising the step of: laminating a gate insulating film and a gate electrode in this order so as to cover the main surface of the semiconductor substrate in the intermediate region.

9. The method of manufacturing a semiconductor device according to claim 1, further comprising the steps of: removing a part of the active region from an uppermost surface of the active region in a depth direction; and forming an other separation insulating film by filling an opening formed by removing the active region, wherein the other separation insulating film is formed to include the same surface as the main surface of the semiconductor substrate.

Description

CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a divisional Ser. No. 14/807,757, filed on Jul. 23, 2015, which claims the benefit of Japanese Patent Application No. 2014-164811 filed on Aug. 13, 2014 the entire contents of each are incorporated herein by reference.

BACKGROUND

[0002] The present invention relates to a semiconductor device and a method of manufacturing the same, and more particularly to a semiconductor device including a resistance element formed by a well region and a separation insulating film and a method of manufacturing the same.

RELATED ART

[0003] A resistance element, in particular, a well resistance element including a well region is used in many semiconductor integrated circuits as a high resistance element. For example, Japanese Patent Laid-Open No. 2008-21962 (Patent Literature 1) discloses a well resistance element having a structure in which a separation insulating film having a so-called STI (Shallow Trench Isolation) structure is formed on a main surface of a semiconductor substrate and a well region is formed immediately below the separation insulating film.

[0004] Further, for example, Japanese Patent Laid-Open No. 2006-13233 (Patent Literature 2) discloses a well resistance element having a structure in which a separation insulating film having the STI structure which is partially removed in a lattice shape in plan view is formed on a main surface of a semiconductor substrate and a well region is formed immediately below the separation insulating film.

SUMMARY

[0005] For example, if an area of the separation insulating film of the well resistance element having a configuration of Patent Literature 1 increases, when the upper surface of the separation insulating film is polished by CMP (Chemical Mechanical Polishing) to form the separation insulating film, flatness of the surface of the separation insulating film after polishing degrades due to a difference of polishing rate between an insulating film that forms the separation insulating film and an insulating film that forms a mask pattern to form the separation insulating film. If the surface of the separation insulating film after polishing has a curved shape by dishing, the depth of the well region immediately below the separation insulating film varies and the variation of resistance value of the well resistance element increases. Therefore, it is difficult to improve accuracy of the well resistance element.

[0006] Further, for example, in Patent Literature 2, the separation insulating film is partially removed in a lattice shape, so that the continuous length of the separation insulating film in a direction along the main surface of the semiconductor substrate is short. Therefore, it is considered that in Patent Literature 2, the occurrence of dishing after the polishing as in Patent Literature 1 is suppressed.

[0007] However, in Patent Literature 2, an electric current flowing from one terminal of a pair of terminals from which a voltage is applied to the well resistance element to the other terminal through the inside of the well resistance element enters into the high resistance separation insulating film, so that the electric current may alternately flow through the separation insulating film and a low resistance active region. Thereby, the current density in the well resistance element becomes partially uneven, so that there is a possibility that the electric current partially meanders or a partial concentration of electric field occurs and the withstand voltage of the well resistance element decreases. This may reduce the reliability of the well resistance element that is expected to function as a high resistance element for high voltage.

[0008] The other purposes and new features will become clear from the description of the present specification and the accompanying drawings.

[0009] A semiconductor device according to an embodiment includes a semiconductor substrate, a well region, an input terminal and an output terminal, a separation insulating film, and an active region. The input terminal and the output terminal are arranged over the semiconductor substrate so as to be electrically coupled to the well region formed in the semiconductor substrate. The separation insulating film is arranged to be in contact with the upper surface of the well region in an intermediate region between the input terminal and the output terminal in a direction along the main surface. The active region is arranged to be in contact with the upper surface of the well region in the semiconductor substrate. The separation insulating film and the active region in the intermediate region have an elongated shape in plan view. In the intermediate region, a plurality of separation insulating films and a plurality of active regions are arranged so that the separation insulating film and the active region are alternately and repeatedly arranged.

[0010] In a method of manufacturing a semiconductor device according to an embodiment, first, a plurality of grooves having an elongated shape in plan view is formed with a gap between them in a main surface of the semiconductor device by using a plurality of mask patterns. A separation insulating film is formed by burying an insulating film into the groove. A well region in contact with the lower surface of the separation insulating film in the semiconductor substrate and an active region in contact with the upper surface of the well region are formed. The input terminal and the output terminal are formed over the semiconductor substrate so as to be electrically coupled to the well region. In the intermediate region between the input terminal and the output terminal, the separation insulating film and the active region have elongated shapes in plan view. In the intermediate region, a plurality of separation insulating films and a plurality of active regions are formed so that the separation insulating film and the active region are alternately and repeatedly arranged.

[0011] According to an embodiment, it is possible to achieve high accuracy of a well resistance element by suppressing the dishing and stabilizing the resistance value of the well resistance element and to achieve suppression of decrease in withstand voltage due to electric field concentration of the well resistance element, so that it is possible to provide a semiconductor device including a well resistance element of high accuracy and high withstand voltage and a method of manufacturing the semiconductor device.

BRIEF DESCRIPTION OF THE DRAWINGS

[0012] FIG. 1 is a schematic plan view showing a state of a wafer, which is a semiconductor device according to an embodiment;

[0013] FIG. 2 is a schematic enlarged view of a region IMC surrounded by a dashed line in FIG. 1;

[0014] FIG. 3 is a schematic plan view showing a configuration of a resistance element region of a first embodiment;

[0015] FIG. 4 is a schematic cross-sectional view taken along line IV-IV in FIG. 3;

[0016] FIG. 5 is a schematic cross-sectional view taken along line V-V in FIG. 3;

[0017] FIG. 6 is a schematic cross-sectional view taken along line VI-VI in FIG. 3;

[0018] FIG. 7 is a schematic plan view showing a configuration of a transistor region of the first embodiment;

[0019] FIG. 8 is a schematic cross-sectional view taken along line VIII-VIII in FIG. 7;

[0020] FIG. 9A is a schematic cross-sectional view showing a first process of a manufacturing method of the first embodiment in a region shown in the cross-sectional view in FIG. 4 in a region where a well resistance element should be formed, and FIG. 9B is a schematic cross-sectional view showing the first process of the manufacturing method of the first embodiment in a region shown in the cross-sectional view in FIG. 8 in a region where a transistor should be formed;

[0021] FIG. 10A is a schematic cross-sectional view showing a second process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 4 in the region where the well resistance element should be formed, and FIG. 10B is a schematic cross-sectional view showing the second process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

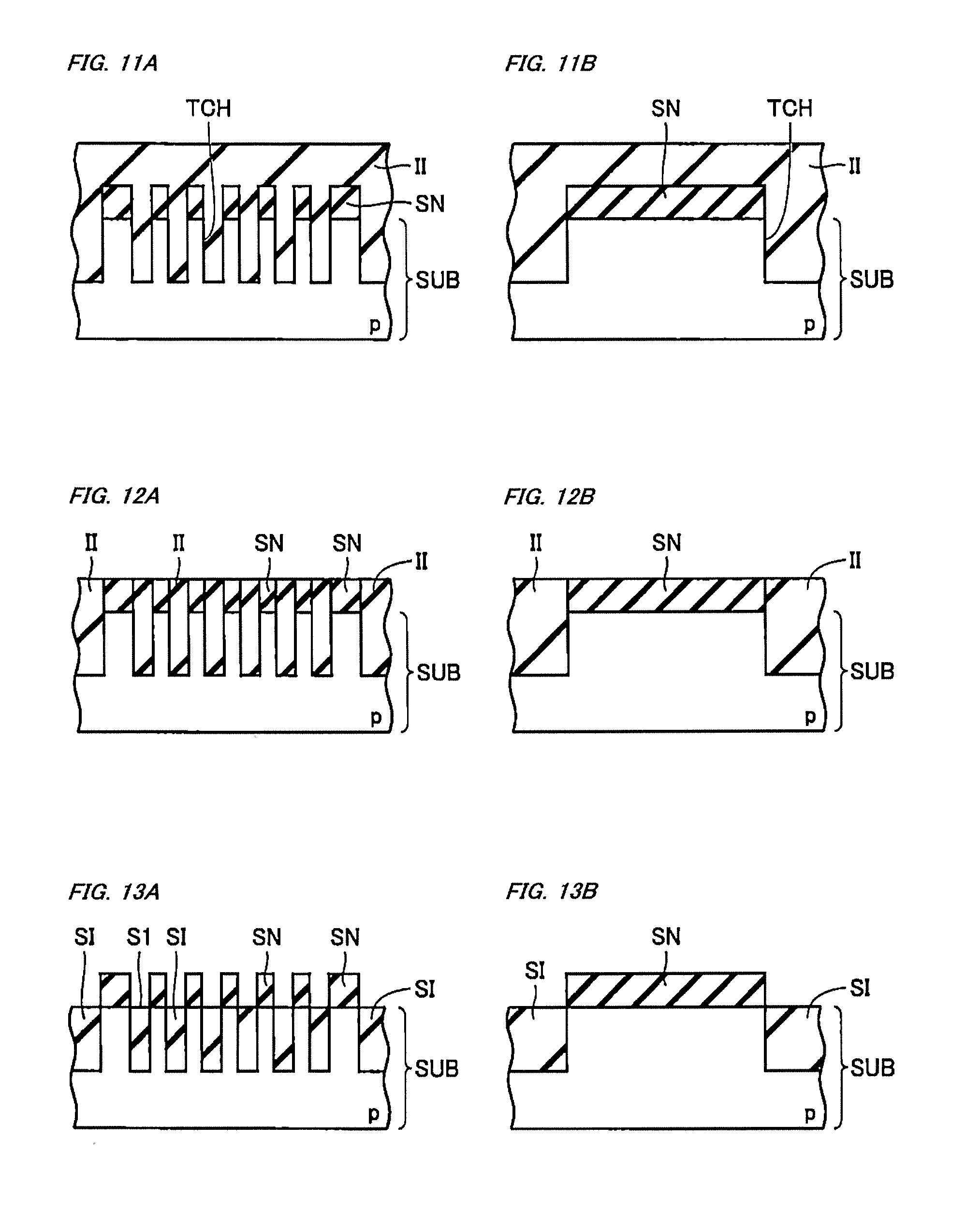

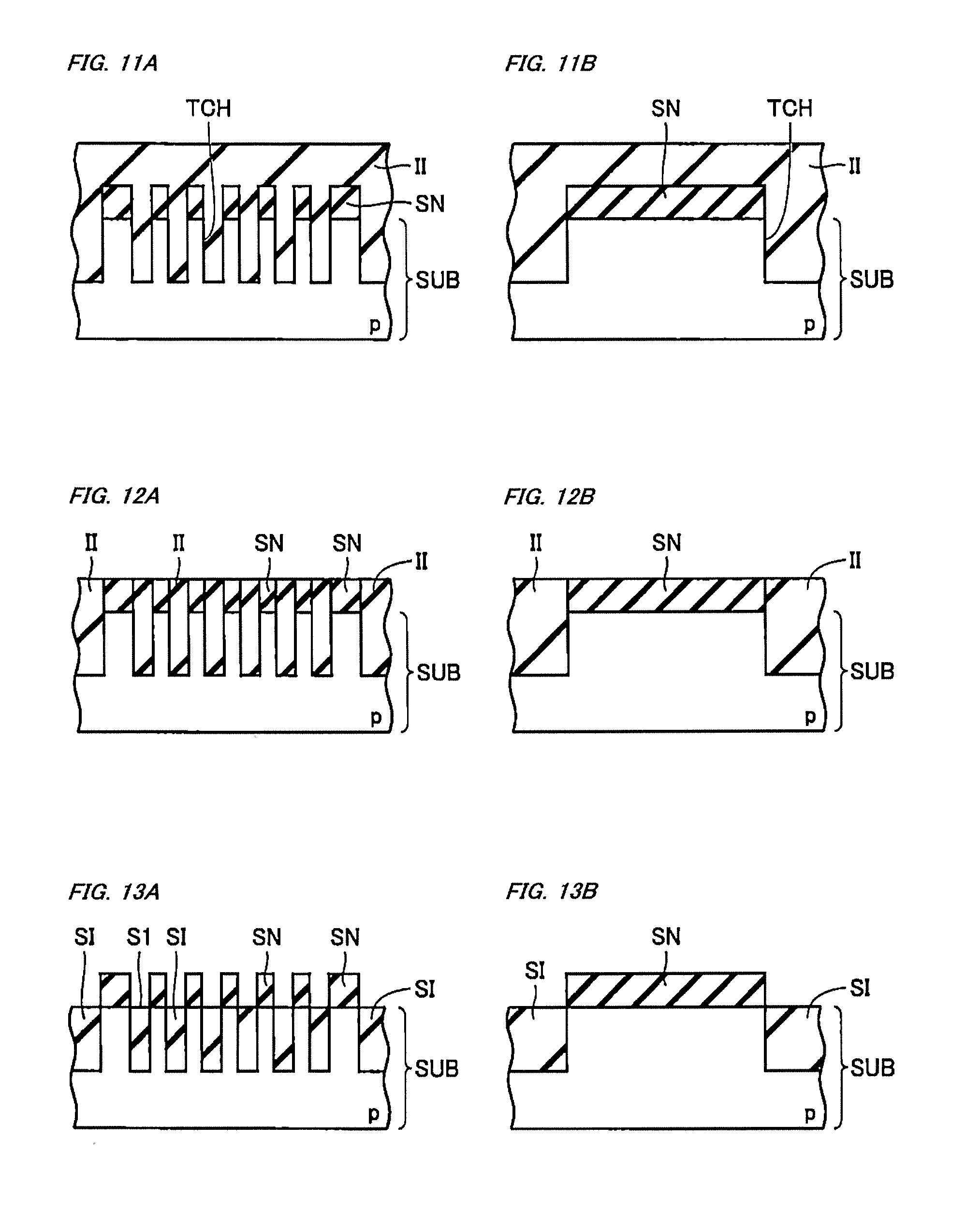

[0022] FIG. 11A is a schematic cross-sectional view showing a third process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 4 in the region where the well resistance element should be formed, and FIG. 11B is a schematic cross-sectional view showing the third process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

[0023] FIG. 12A is a schematic cross-sectional view showing a fourth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 4 in the region where the well resistance element should be formed, and FIG. 12B is a schematic cross-sectional view showing the fourth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

[0024] FIG. 13A is a schematic cross-sectional view showing a fifth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 4 in the region where the well resistance element should be formed, and FIG. 13B is a schematic cross-sectional view showing the fifth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

[0025] FIG. 14A is a schematic cross-sectional view showing a sixth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 4 in the region where the well resistance element should be formed, and FIG. 14B is a schematic cross-sectional view showing the sixth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

[0026] FIG. 15A is a schematic cross-sectional view showing a seventh process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 4 in the region where the well resistance element should be formed, and FIG. 15B is a schematic cross-sectional view showing the seventh process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

[0027] FIG. 16A is a schematic cross-sectional view showing an eighth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 4 in the region where the well resistance element should be formed, and FIG. 16B is a schematic cross-sectional view showing the eighth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

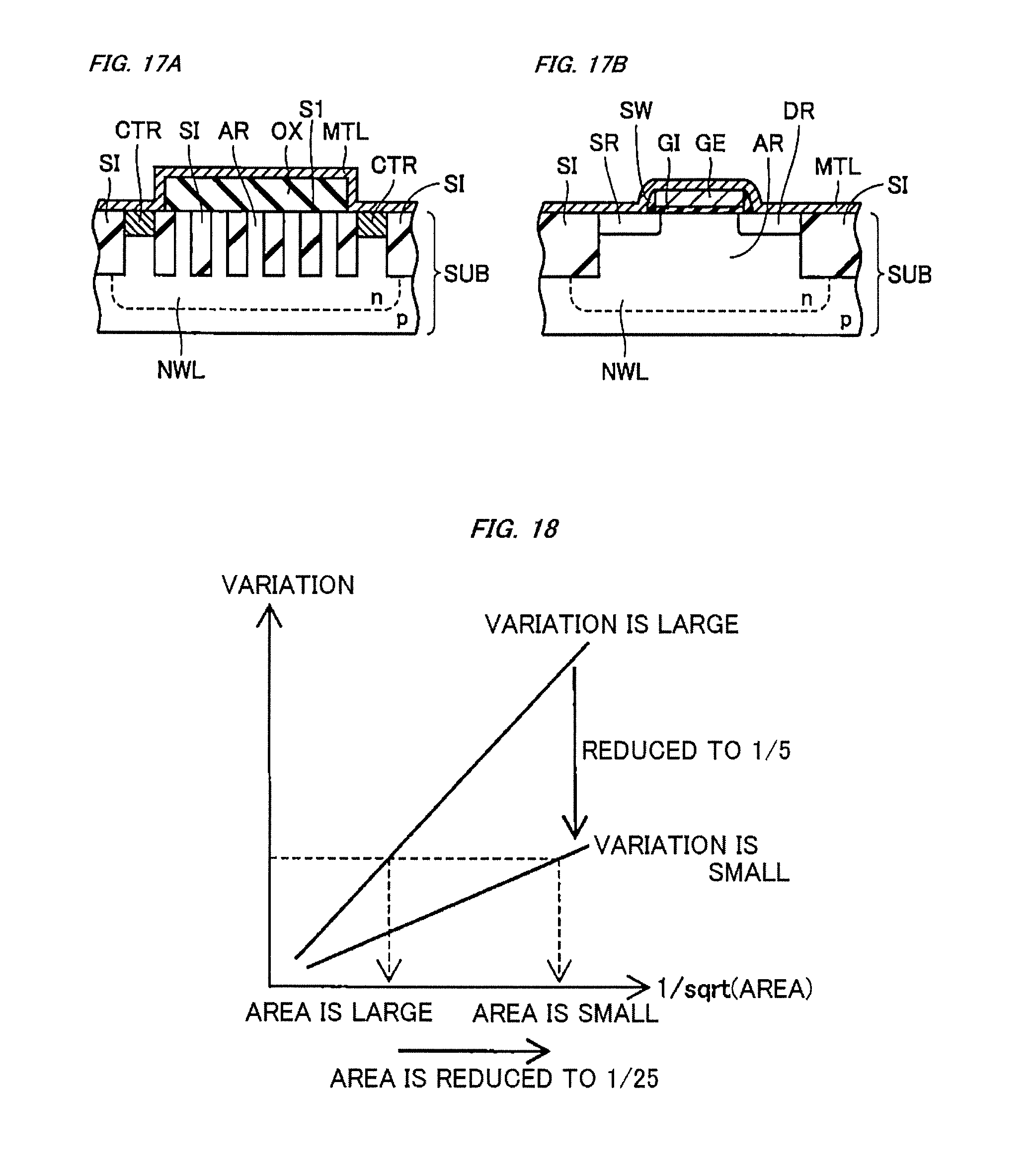

[0028] FIG. 17A is a schematic cross-sectional view showing a ninth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 4 in the region where the well resistance element should be formed, and FIG. 17B is a schematic cross-sectional view showing the ninth process of the manufacturing method of the first embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

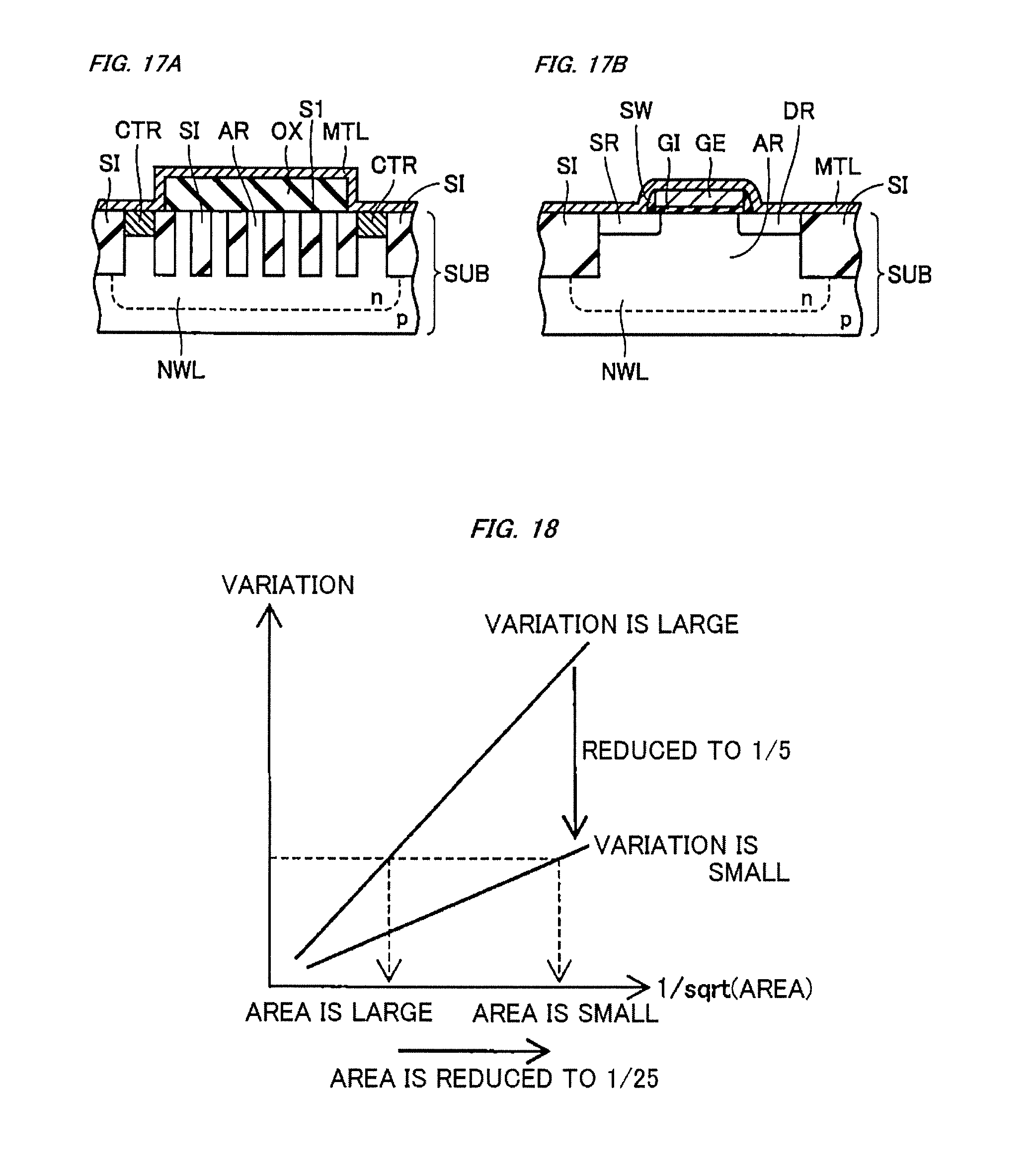

[0029] FIG. 18 is a graph showing a relationship between the area in plan view of the well resistance element and a variation of a resistance value of the well resistance element;

[0030] FIG. 19 is a schematic plan view showing a configuration of a resistance element region of a second embodiment;

[0031] FIG. 20 is a schematic cross-sectional view taken along line XX-XX in FIG. 19;

[0032] FIG. 21 is a schematic cross-sectional view taken along line XXI-XXI in FIG. 19;

[0033] FIG. 22 is a schematic cross-sectional view taken along line XXII-XXII in FIG. 19;

[0034] FIG. 23A is a schematic cross-sectional view showing a first process of a manufacturing method of the second embodiment in a region shown in the cross-sectional view in FIG. 20 in a region where a well resistance element should be formed, FIG. 23B is a schematic cross-sectional view showing the first process of the manufacturing method of the second embodiment in a region shown in the cross-sectional view in FIG. 21 in the region where the well resistance element should be formed, and FIG. 23C is a schematic cross-sectional view showing the first process of the manufacturing method of the second embodiment in a region shown in the cross-sectional view in FIG. 22 in the region where the well resistance element should be formed;

[0035] FIG. 24A is a schematic cross-sectional view showing a second process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 20 in a region where the well resistance element should be formed, FIG. 24B is a schematic cross-sectional view showing the second process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 21 in the region where the well resistance element should be formed, and FIG. 24C is a schematic cross-sectional view showing the second process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 22 in the region where the well resistance element should be formed;

[0036] FIG. 25A is a schematic cross-sectional view showing a third process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 20 in a region where the well resistance element should be formed, FIG. 25B is a schematic cross-sectional view showing the third process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 21 in the region where the well resistance element should be formed, and FIG. 25C is a schematic cross-sectional view showing the third process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 22 in the region where the well resistance element should be formed;

[0037] FIG. 26A is a schematic cross-sectional view showing a fourth process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 20 in a region where the well resistance element should be formed, FIG. 26B is a schematic cross-sectional view showing the fourth process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 21 in the region where the well resistance element should be formed, and FIG. 26C is a schematic cross-sectional view showing the fourth process of the manufacturing method of the second embodiment in the region shown in the cross-sectional view in FIG. 22 in the region where the well resistance element should be formed;

[0038] FIG. 27 is a schematic plan view showing a configuration of a resistance element region of a third embodiment;

[0039] FIG. 28 is a schematic cross-sectional view taken along line XXVIII-XXVIII in FIG. 27;

[0040] FIG. 29 is a schematic cross-sectional view taken along line XXIX-XXIX in FIG. 27;

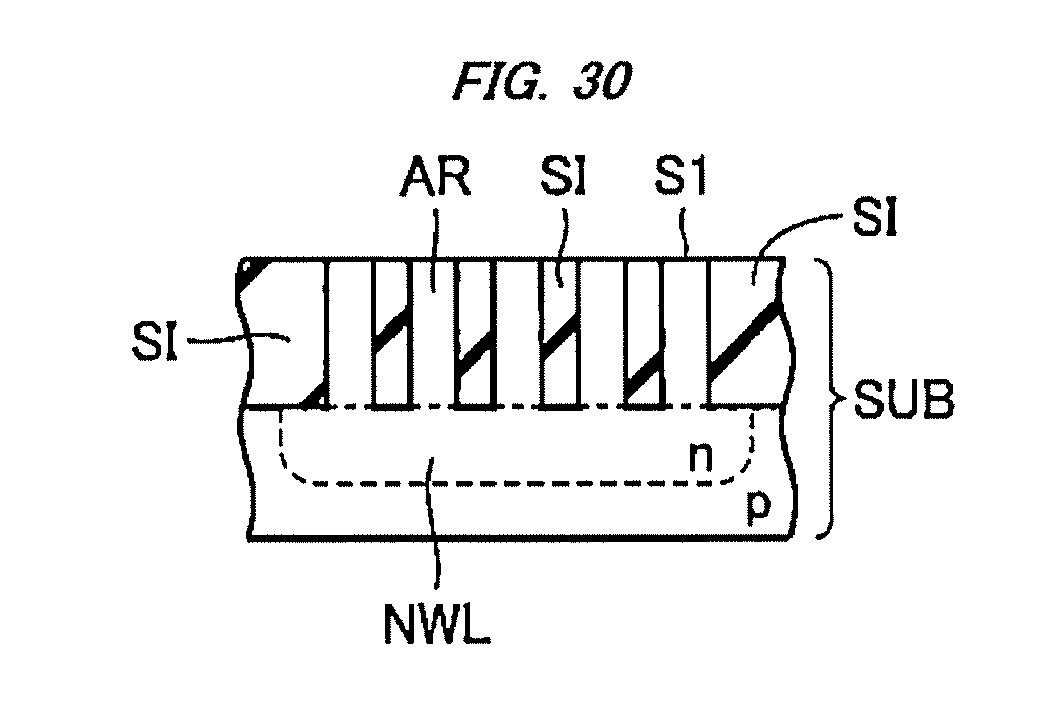

[0041] FIG. 30 is a schematic cross-sectional view taken along line XXX-XXX in FIG. 27;

[0042] FIG. 31A is a schematic cross-sectional view showing a first process of a manufacturing method of the third embodiment in a region shown in the cross-sectional view in FIG. 28 in a region where a well resistance element should be formed, and FIG. 31B is a schematic cross-sectional view showing the first process of the manufacturing method of the third embodiment in a region shown in the cross-sectional view in FIG. 29 in a region where the well resistance element should be formed;

[0043] FIG. 32A is a schematic cross-sectional view showing a second process of the manufacturing method of the third embodiment in the region shown in the cross-sectional view in FIG. 28 in the region where the well resistance element should be formed, and FIG. 32B is a schematic cross-sectional view showing the second process of the manufacturing method of the third embodiment in the region shown in the cross-sectional view in FIG. 29 in the region where the well resistance element should be formed;

[0044] FIG. 33A is a schematic cross-sectional view showing a third process of the manufacturing method of the third embodiment in the region shown in the cross-sectional view in FIG. 28 in the region where the well resistance element should be formed, and FIG. 33B is a schematic cross-sectional view showing the third process of the manufacturing method of the third embodiment in the region shown in the cross-sectional view in FIG. 29 in the region where the well resistance element should be formed;

[0045] FIG. 34A is a schematic cross-sectional view showing a fourth process of the manufacturing method of the third embodiment in the region shown in the cross-sectional view in FIG. 28 in the region where the well resistance element should be formed, and FIG. 34B is a schematic cross-sectional view showing the fourth process of the manufacturing method of the third embodiment in the region shown in the cross-sectional view in FIG. 29 in the region where the well resistance element should be formed;

[0046] FIG. 35 is a schematic plan view showing a configuration of a resistance element region of a fourth embodiment;

[0047] FIG. 36 is a schematic cross-sectional view taken along line XXXVI-XXXVI in FIG. 35;

[0048] FIG. 37 is a schematic cross-sectional view taken along line XXXVII-XXXVII in FIG. 35;

[0049] FIG. 38 is a schematic cross-sectional view taken along line XXXVIII-XXXVIII in FIG. 35;

[0050] FIG. 39A is a schematic cross-sectional view showing a first process of a manufacturing method of the fourth embodiment in a region shown in the cross-sectional view in FIG. 36 in a region where a well resistance element should be formed, and FIG. 39B is a schematic cross-sectional view showing the first process of the manufacturing method of the fourth embodiment in the region shown in the cross-sectional view in FIG. 8 in a region where a transistor should be formed;

[0051] FIG. 40A is a schematic cross-sectional view showing a second process of the manufacturing method of the fourth embodiment in the region shown in the cross-sectional view in FIG. 36 in the region where the well resistance element should be formed, and FIG. 40B is a schematic cross-sectional view showing the second process of the manufacturing method of the fourth embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

[0052] FIG. 41A is a schematic cross-sectional view showing a third process of the manufacturing method of the fourth embodiment in the region shown in the cross-sectional view in FIG. 36 in the region where the well resistance element should be formed, and FIG. 41B is a schematic cross-sectional view showing the third process of the manufacturing method of the fourth embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed;

[0053] FIG. 42 is a schematic plan view showing a configuration of a resistance element region of a fifth embodiment;

[0054] FIG. 43 is a schematic cross-sectional view taken along line XLIII-XLIII in FIG. 42;

[0055] FIG. 44 is a schematic cross-sectional view taken along line XLIV-XLIV in FIG. 42;

[0056] FIG. 45 is a schematic cross-sectional view taken along line XLV-XLV in FIG. 42;

[0057] FIG. 46 is a schematic plan view showing a configuration of a resistance element region of a sixth embodiment;

[0058] FIG. 47 is a schematic cross-sectional view taken along line XLVII-XLVII in FIG. 46;

[0059] FIG. 48 is a schematic cross-sectional view taken along line XLVIII-XLVIII in FIG. 46;

[0060] FIG. 49 is a schematic cross-sectional view taken along line XLIX-XLIX in FIG. 46;

[0061] FIG. 50 is a schematic plan view showing a configuration of a resistance element region of a seventh embodiment;

[0062] FIG. 51 is a schematic cross-sectional view taken along line LI-LI in FIG. 50;

[0063] FIG. 52 is a schematic cross-sectional view taken along line LII-LII in FIG. 50;

[0064] FIG. 53 is a schematic cross-sectional view taken along line LIII-LIII in FIG. 50;

[0065] FIG. 54A is a schematic cross-sectional view showing a first process of a manufacturing method of the seventh embodiment in a region shown in the cross-sectional view in FIG. 51 in a region where a well resistance element should be formed, FIG. 54B is a schematic cross-sectional view showing the first process of the manufacturing method of the seventh embodiment in the region shown in the cross-sectional view in FIG. 8 in a region where a transistor should be formed, and FIG. 54C is a schematic cross-sectional view showing the first process of the manufacturing method of the seventh embodiment in a region shown in the cross-sectional view in FIG. 53 in the region where the well resistance element should be formed;

[0066] FIG. 55A is a schematic cross-sectional view showing a second process of the manufacturing method of the seventh embodiment in the region shown in the cross-sectional view in FIG. 51 in the region where the well resistance element should be formed, FIG. 55B is a schematic cross-sectional view showing the second process of the manufacturing method of the seventh embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed, and FIG. 55C is a schematic cross-sectional view showing the second process of the manufacturing method of the seventh embodiment in the region shown in the cross-sectional view in FIG. 53 in the region where the well resistance element should be formed;

[0067] FIG. 56A is a schematic cross-sectional view showing a third process of the manufacturing method of the seventh embodiment in the region shown in the cross-sectional view in FIG. 51 in the region where the well resistance element should be formed, FIG. 56B is a schematic cross-sectional view showing the third process of the manufacturing method of the seventh embodiment in the region shown in the cross-sectional view in FIG. 8 in the region where the transistor should be formed, and FIG. 56C is a schematic cross-sectional view showing the third process of the manufacturing method of the seventh embodiment in the region shown in the cross-sectional view in FIG. 53 in the region where the well resistance element should be formed;

[0068] FIG. 57 is a schematic plan view showing a configuration of a resistance element region of an eighth embodiment;

[0069] FIG. 58 is a schematic cross-sectional view taken along line LVIII-LVIII in FIG. 57;

[0070] FIG. 59 is a schematic cross-sectional view taken along line LIX-LIX in FIG. 57;

[0071] FIG. 60A is a schematic cross-sectional view showing a first process of a manufacturing method of the eighth embodiment in a region shown in the cross-sectional view in FIG. 58 in a region where a well resistance element should be formed, and FIG. 60B is a schematic cross-sectional view showing the first process of the manufacturing method of the eighth embodiment in a region shown in the cross-sectional view in FIG. 59 in a region where a transistor should be formed;

[0072] FIG. 61A is a schematic cross-sectional view showing a second process of the manufacturing method of the eighth embodiment in the region shown in the cross-sectional view in FIG. 58 in the region where the well resistance element should be formed, and FIG. 61B is a schematic cross-sectional view showing the second process of the manufacturing method of the eighth embodiment in the region shown in the cross-sectional view in FIG. 59 in the region where the transistor should be formed;

[0073] FIG. 62A is a schematic cross-sectional view showing a third process of the manufacturing method of the eighth embodiment in the region shown in the cross-sectional view in FIG. 58 in the region where the well resistance element should be formed, and FIG. 62B is a schematic cross-sectional view showing the third process of the manufacturing method of the eighth embodiment in the region shown in the cross-sectional view in FIG. 59 in the region where the transistor should be formed;

[0074] FIG. 63 is a schematic plan view showing a configuration of a resistance element region of a ninth embodiment;

[0075] FIG. 64 is a schematic plan view showing a configuration of a resistance element region of a tenth embodiment;

[0076] FIG. 65 is a schematic cross-sectional view taken along line LXV-LXV in FIG. 64;

[0077] FIG. 66 is a schematic cross-sectional view taken along line LXVI-LXVI in FIG. 64;

[0078] FIG. 67 is a schematic plan view showing a configuration of a resistance element region of an eleventh embodiment;

[0079] FIG. 68 is a schematic cross-sectional view taken along line LXVIII-LXVIII in FIG. 67;

[0080] FIG. 69 is a schematic cross-sectional view taken along line LXIX-LXIX in FIG. 67;

[0081] FIG. 70 is a schematic plan view showing a configuration of a resistance element region of a twelfth embodiment;

[0082] FIG. 71 is a schematic plan view showing a configuration of a resistance element region of a first comparative example;

[0083] FIG. 72 is a schematic cross-sectional view taken along line LXXII-LXXII in FIG. 71;

[0084] FIG. 73 is a schematic cross-sectional view taken along line LXXIII-LXXIII in FIG. 71;

[0085] FIG. 74 is a schematic cross-sectional view showing a first process of a manufacturing method of the first comparative example in the region shown in the cross-sectional view in FIG. 72 in the region where a well resistance element should be formed;

[0086] FIG. 75 is a schematic cross-sectional view showing a second process of the manufacturing method of the first comparative example in the region shown in the cross-sectional view in FIG. 72 in the region where the well resistance element should be formed;

[0087] FIG. 76 is a schematic cross-sectional view showing a third process of the manufacturing method of the first comparative example in the region shown in the cross-sectional view in FIG. 72 in the region where the well resistance element should be formed;

[0088] FIG. 77 is a schematic cross-sectional view showing a fourth process of the manufacturing method of the first comparative example in the region shown in the cross-sectional view in FIG. 72 in the region where the well resistance element should be formed;

[0089] FIG. 78 is a schematic cross-sectional view showing a fifth process of the manufacturing method of the first comparative example in the region shown in the cross-sectional view in FIG. 72 in the region where the well resistance element should be formed;

[0090] FIG. 79 is a schematic plan view showing a configuration of a resistance element region of a second comparative example;

[0091] FIG. 80 is a schematic cross-sectional view taken along line LXXX-LXXX in FIG. 79; and

[0092] FIG. 81 is a schematic cross-sectional view taken along line LXXXI-LXXXI in FIG. 79.

DETAILED DESCRIPTION

[0093] Hereinafter, embodiments will be described with reference to the drawings.

First Embodiment

[0094] First, a semiconductor device in a wafer state will be described as an embodiment.

[0095] With reference to FIG. 1, a plurality of chip regions IMC of an solid state image sensing element is formed in a semiconductor wafer SCW formed of a semiconductor substrate SUB. Each of the chip regions IMC has a rectangular planar shape and the chip regions INC are arranged in a matrix shape. In the semiconductor wafer SCW, a dicing line region DLR is formed between the chip regions IMC. The semiconductor wafer SCW is diced by the dicing line region DLR, so that the semiconductor wafer SCW is divided into a plurality of semiconductor chips.

[0096] With reference to FIG. 2, in the chip region IMC that forms a divided semiconductor chip, for example, a resistance element region RE where a resistance element is arranged and a transistor region TR where a MOS (Metal Oxide Semiconductor) transistor used as a peripheral circuit is arranged are arranged. In FIG. 2, as an example, a plurality of resistance element regions RE and a plurality of transistor regions TR are arranged in different regions in a matrix shape. However, the arrangement is not limited to this.

[0097] Next, a well resistance element arranged in the resistance element region RE of the present embodiment will be described with reference to FIGS. 3 to 6.

[0098] With reference to FIGS. 3 to 6, the resistance element region RE of the present embodiment is formed in a silicon semiconductor substrate SUB containing, for example, p-type conductive impurities. The well resistance element in the resistance element region RE mainly includes a well region NWL, input-side contacts CT1 used as input terminals, output-side contacts CT2 used as output terminals, a separation insulating film SI, and active regions AR.

[0099] The well region NWL is a region which is formed inside the semiconductor substrate SUB and which contains n-type conductive impurities. FIG. 3 shows that the well region NWL is formed to have a rectangular planar shape. However, the shape is not limited to a rectangular planar shape.

[0100] The input-side contact CT1 and the output-side contact CT2 are arranged over a main surface S1 of the semiconductor substrate SUB so as to be electrically coupled to the well region NWL. For example, a plurality of (here, five) input-side contacts CT1 and a plurality of (here, five) output-side contacts CT2 may be arranged in the horizontal direction of FIG. 3 with a gap between them. It is preferable that the number of the arranged input-side contacts CT1 and the number of the arranged output-side contacts CT2 are the same. Here, one of the input-side contacts CT1 and one of the output-side contacts CT2 are arranged to face each other in the vertical direction of FIG. 3. It is preferable that an electrical signal such as an electric current is transmitted and received between a pair of the input-side contact CT1 and the output-side contact CT2 that are arranged to face each other in the vertical direction of FIG. 3 in this way. However, it is not limited to this.

[0101] The separation insulating film SI is arranged around the well resistance element, so that the separation insulating film SI electrically separates the well resistance element from other elements around the well resistance element. Further, the separation insulating film SI is arranged in some regions in a central region (intermediate region) of the well resistance element between the input-side contact CT1 and the output-side contact CT2. Specifically, the separation insulating film SI in the intermediate region is arranged to be in contact with the upper surface of the well region NWL. A plurality of separation insulating films SI has an elongated shape (for example, a shape of a long rectangle) in plan view, which are arranged side by side with a gap between them. The separation insulating film SI in the intermediate region (in the well resistance element) is formed as the same layer as that of the separation insulating film SI around the well resistance element.

[0102] The active region AR is formed integrally with the well region NWL inside the semiconductor substrate SUB. In particular, the active region AR is a conductive region which contains n-type impurities and which extends upward above a boundary line indicated by a dotted line in FIGS. 4 and 5 and reaches the main surface S1 of the semiconductor substrate SUB. In other words, a conductive region containing n-type impurities above the boundary line is defined as the active region AR here, and a conductive region containing n-type impurities below the boundary line is defined as the well region NWL here.

[0103] For example, in the semiconductor substrate SUB immediately below the input-side contact CT1 and the output-side contact CT2, the active region AR is arranged through a silicide layer SC and a contact region CTR. The active region AR is arranged to be in contact with the upper surface of the well region NWL (because the active region AR is integrated with the well region NWL as described above).

[0104] The silicide layer SC and the contact region CTR are regions which are formed in regions close to the contact CT1 or CT2 (upper regions of FIGS. 4 and 5) in the active region AR and whose conductivity is increased. The silicide layer SC is a region which is formed on the uppermost surface of the active region AR (the uppermost surface of the semiconductor substrate SUB) in contact with the contact CT1 or CT2 and which is formed when a metallic material reacts with silicon included in the semiconductor substrate SUB. The contact region CTR is a region (n+ region) which is formed in a region immediately below the silicide layer SC in the active region AR so that the density of the n-type conductive impurities is increased. The contacts CT1 and CT2 are well electrically coupled with the well region NWL by the presence of the contact region CTR and the like whose conductivity is higher than that of the active region AR.

[0105] The active region AR in the intermediate region is arranged to be in contact with the upper surface of the well region NWL. A plurality of active regions AR has an elongated shape (for example, a shape of a long rectangle, in other words, a striped shape) in plan view, which are arranged side by side with a gap between them.

[0106] Therefore, in the intermediate region, a plurality of separation insulating films SI and a plurality of active regions AR, each of which has an elongated shape in plan view, are arranged so that the separation insulating film SI and the active region AR are alternately and repeatedly arranged in a direction perpendicular to a direction in which the separation insulating film SI and the active region AR extend. The separation insulating film SI and the active region AR, which are adjacent to each other in the direction in which the separation insulating films SI and the active regions AR are alternately arranged, are in contact with each other.

[0107] Although FIG. 3 shows that the length of the active region AR in the horizontal direction is substantially the same as that of the silicide layer SC, the active region AR may have any length. For example, the active region AR may be formed to have a length greater than that of the well region NWL in the horizontal direction.

[0108] In the present embodiment, in the region between the input-side contact CT1 and the output-side contact CT2, the separation insulating films SI and the active regions AR, which have a striped shape, are formed so that the heights of the uppermost surfaces of the separation insulating films SI and the active regions AR are substantially the same. In other words, in the region between the input-side contact CT1 and the output-side contact CT2, the separation insulating films SI and the active regions AR are formed so that the uppermost surfaces of the separation insulating films SI and the active regions AR form the same surface. The uppermost surface of the active region AR corresponds to the main surface S1 of the semiconductor substrate SUB, so that the separation insulating film SI is formed so that the uppermost surface of the separation insulating film SI is the same surface as the main surface S1 of the semiconductor substrate SUB (so that the uppermost surface of the separation insulating film SI and the main surface S1 of the active region AR (the semiconductor substrate SUB) are flush with each other).

[0109] In the present embodiment, in the region between the input-side contact CT1 and the output-side contact CT2, the separation insulating film SI and the active region AR are formed to extend in a direction (the horizontal direction of FIG. 3) perpendicular to a direction (the vertical direction of FIG. 3) connecting the input-side contact CT1 and the output-side contact CT2 in plan view.

[0110] The conductivity types of components included in the well resistance element described above may be reversed. For example, a well region containing p-type conductive impurities may be formed in a semiconductor substrate SUB containing n-type conductive impurities.

[0111] Here, a mechanism of the well resistance element, which functions as a resistance in the semiconductor device, will be described. When the well resistance element is driven, a voltage is applied between the input-side contact CT1 and the output-side contact CT2, so that an electric current flows from the input-side contact CT1 to the output-side contact CT2 mainly in the well region NWL. In particular, the present embodiment has a configuration in which the electric current passing through the silicide layer SC and the contact region CTR immediately below the input-side contact CT1 can automatically flow from the active region AR immediately below the contact region CTR into the well region NWL (because the circumference of the active region AR immediately below the contact region CTR is covered by the separation insulating film SI). The resistance value of the well resistance element depends in particular on the cross-sectional area and the shape of the well region NWL shown in the cross-sectional view in FIG. 6.

[0112] Next, a MOS transistor arranged in the transistor region TR will be described with reference to FIGS. 7 and 8.

[0113] With reference to FIGS. 7 and 8, the transistor region TR is also formed in the silicon semiconductor substrate SUB including, for example, p-type conductive impurities. The MOS transistor in the transistor region TR mainly includes a source region SR, a drain region DR, a gate insulating film GI, and a gate electrode GE. The source region SR and the drain region DR are arranged with a gap between them in the main surface of the semiconductor substrate SUB. Also in the transistor region TR, the well region NWL is formed inside the semiconductor substrate SUB, and the source region SR and the drain region DR are formed in the well region NWL. The silicide layer SC is formed on the surfaces of the source region SR and the drain region DR.

[0114] The gate electrode GE is formed over the main surface of the semiconductor substrate SUB, which is sandwiched by the source region SR and the drain region DR, through the gate insulating film GI. The MOS transistor is formed inside the separation insulating film SI which is the same layer as the separation insulating film SI in the resistance element region RE and which surrounds the circumference of the transistor region TR in plan view. A side wall insulating film SW is formed on a side wall of the gate electrode GE. The configuration of the MOS transistor formed in the transistor region TR described above is basically the same in each embodiment described below.

[0115] Next, a method of manufacturing a semiconductor device including the resistance element region RE and the transistor region TR of the present embodiment will be described with reference to FIGS. 9A to 17B.

[0116] With reference to FIGS. 9A and 9B, a thin film of, for example, a silicon nitride film to form a pattern is formed over, for example, the main surface S1 of the semiconductor substrate SUB which is formed of p-type silicon and which forms the chip region IMC (see FIG. 1). Next, the thin film of the silicon nitride film is formed as a plurality of mask patterns SN by a normal photoengraving technique (exposure and development) using photoresist as a photosensitizing agent not shown in the drawings and etching of the silicon nitride film. Here, basically, the mask pattern SN is formed immediately above a region where the active region AR is finally formed, and an opening of the mask pattern SN is formed immediately above a region other than the region where the active region AR is formed.

[0117] With reference to FIGS. 10A and 10B, normal etching is performed by using the plurality of mask patterns SN as an etching mask. Thereby, the semiconductor substrate SUB is etched from the main surface S1 in the depth direction (the vertical direction in FIGS. 10A and 10B) of the semiconductor substrate SUB, so that a plurality of trenches TCH (grooves) is formed in the semiconductor substrate SUB. In particular, in the resistance element region RE shown in FIG. 10A, a plurality of the trenches TCH is formed with a gap between them in a direction along the main surface S1 (the horizontal direction in FIG. 10A). Therefore, a plurality of the trenches TCH having an elongated shape in plan view is formed with a gap between them in the same manner as a plurality of the separation insulating films SI, in particular, in the intermediate region in FIG. 3. The extending direction of the elongated shape of the trench TCH is a direction crossing a direction finally connecting the contact CT1 and the contact CT2. Also in the transistor region TR shown in FIG. 10B, a plurality of trenches TCH is formed in the semiconductor substrate SUB according to the shape of the mask pattern SN.

[0118] With reference to FIGS. 11A and 11B, an insulating film II such as a silicon oxide film is formed by, for example, a normal CVD (Chemical Vapor Deposition) method over the main surface of the semiconductor substrate SUB so as to fill the inside of the trenches TCH and cover the surface of the mask patterns SN.

[0119] With reference to FIGS. 12A and 12B, the insulating film II formed in the process of FIGS. 11A and 11B is removed, so that the upper surfaces of the mask patterns SN that have been covered by the insulating film II are exposed. Specifically, for example, the insulating film II is polished and removed by, for example, the CMP until the upper surfaces of the mask patterns SN are exposed and the upper surfaces of the exposed mask patterns SN and the insulating film II are flattened. When removing the insulating film II in the process described above, for example, normal etching using hydrofluoric acid may be performed instead of the polishing process described above.

[0120] With reference to FIGS. 13A and 13B, in regions whose vertical height in FIGS. 13A and 13B is the same as that of the mask patterns SN, the insulating film II adjacent to the mask pattern SN (in the horizontal direction in FIGS. 13A and 13B) is removed. Specifically, for example, in FIG. 13A, the insulating films II located between a plurality of mask patterns SN are removed. At this time, specifically, the insulating films II in the regions are removed by, for example, normal etching using hydrofluoric acid. In FIG. 13B, a pair of insulating films II adjacent to the central mask pattern SN is removed.

[0121] Thereby, the insulating films II become the separation insulating films SI whose uppermost surface has substantially the same height as the main surface S1 of the semiconductor substrate SUB (in the vertical direction of FIGS. 13A and 13B) and which are formed to fill the trenches TCH.

[0122] With reference to FIGS. 14A and 14B, the mask patterns SN protruding above the separation insulating films SI are removed by the process of FIGS. 13A and 13B. Thereby, the separation insulating films SI and the semiconductor substrate SUB are formed so that the same surface, that is, the main surface S1, becomes the uppermost surface.

[0123] With reference to FIGS. 15A and 15B, a pattern of photoresist PHR used as a photosensitizing agent is formed over the main surface S1 of the semiconductor substrate SUB by a normal photoengraving technique. It is preferable that the pattern of photoresist PHR is formed so as to cover a part of the upper surfaces of the separation insulating films SI, that is, substantially a region other than a region where the well region NWL is formed, or conversely so as to form an opening of the photoresist PHR is formed immediately above the region where the well region NWL is formed in the semiconductor substrate SUB regardless of the presence or absence of the separation insulating film SI.

[0124] Subsequently, n-type conductive impurities are introduced into the semiconductor substrate SUB by using a normal ion implantation technique using the pattern of photoresist PHR. Thereby, in the resistance element region RE and the transistor region TR, the semiconductor substrate SUB which is adjacent to the separation insulating films SI in the horizontal direction of FIGS. 15A and 15B (and whose height is the same as that of the separation insulating films SI) is formed as the active region AR containing n-type conductive impurities, and the well region NWL containing n-type conductive impurities is formed in a region below the lowest portion BTM of the separation insulating films SI in FIGS. 15A and 15B. Thereby, the well region NWL is formed so as to be in contact with the lower surfaces of the separation insulating films SI in the semiconductor substrate SUB, and the active region AR is formed so as to be in contact with the upper surface of the well region NWL in the semiconductor substrate SUB. From the above, the main surface S1 of the semiconductor substrate SUB becomes equal to the uppermost surface of the active region AR.

[0125] As a result, as shown in FIGS. 15A and 3, in the intermediate region, the separation insulating film SI and the active region AR are formed to have an elongated shape in plan view. In the intermediate region, a plurality of separation insulating films SI and a plurality of active regions AR are formed so that the separation insulating film SI and the active region AR are alternately and repeatedly arranged.

[0126] In the following drawings, the dashed line indicating the boundary between the active region AR and the well region NWL is omitted (the same goes for the drawings for explaining a manufacturing method in each embodiment described below).

[0127] With reference to FIG. 16B, in particular, in the transistor region TR, the gate insulating film GI and the gate electrode GE are formed over, for example, a part of the main surface of the semiconductor substrate SUB immediately above a region sandwiched by the separation insulating films SI, which is the well region NWL. Specifically, a silicon oxide film or the like is formed as a gate insulating film over the main surface of the semiconductor substrate SUB by, for example, a thermal oxidation processing method. A polycrystalline silicon film or the like to be the gate electrode is deposited over the gate insulating film. Thereafter, the gate insulating film and the polycrystalline silicon film or the like are patterned.

[0128] Thereafter, a region in which n-type conductive impurities are implanted into the active regions AR by a normal ion implantation technique by using the gate electrode GE as a mask and further using a mask which is not shown in FIG. 16A and which has openings immediately above part of the active regions AR in FIG. 16A (for example, in particular, the active regions AR at the left end and the right end shown in FIG. 16A). Thereby, the contact regions CTR are formed in the resistance element region in FIG. 16A, and the source region SR and the drain region DR are formed in the transistor region in FIG. 16B. It is preferable that the contact regions CTR, the source region SR, and the drain region DR are formed at the same time.

[0129] Thereafter, the side wall insulating film SW that covers the side walls of the gate electrode GE and the gate insulating film GI in the transistor region is formed as needed and the ion implantation technique is further performed by using the side wall insulating film SW as a mask. Thereby, the impurity concentration in the source region SR and the drain region DR may be further increased.

[0130] With reference to FIG. 17A, a processing mask pattern OX formed of, for example, a silicon oxide film is formed so as to cover the active regions AR except for the active regions AR where the contact region CTR is formed and the separation insulating films SI in the intermediate region by a normal photoengraving technique and etching.

[0131] With reference to FIGS. 17A and 17B, a metal film MTL is deposited over the main surface S1 of the semiconductor substrate SUB so as to cover the processing mask pattern OX in the resistance element region and the gate electrode GE and the side wall insulating film SW in the transistor region. The metal film MTL is formed by, for example, depositing a layered structure of cobalt and titanium nitride having a total thickness of more than several nm and less than several tens of nm by a metal thin film formation method such as a publicly known sputtering method. However, the material of the metal film MTL is not limited to the above material.

[0132] With reference to FIGS. 4 and 8, subsequently, a so-called annealing treatment is performed in which the semiconductor substrate SUB is heated for tens of seconds to minutes at several hundreds of degrees in .degree. C. Then, atoms of silicon included in upper portions of the contact regions CTR including n-type impurities and upper portions of the source region SR and the drain region DR and atoms of cobalt and nickel included in the metal film MTL in contact with the contact regions CTR, the source region SR, and the drain region DR react together to form silicide layers SC. An unnecessary metal film MTL that has not reacted here is removed by etching.

[0133] Further, with reference to FIG. 4, in the resistance element region, the input-side contact CT1 and the output-side contact CT2 which are conductive thin film patterns are formed over, in particular, the upper surface of the silicide layers SC over the main surface S1 of the semiconductor substrate SUB by, for example, a sputtering method, a normal photoengraving technique, and etching. The input-side contact CT1 and the output-side contact CT2 are in contact with the silicide layer SC. The silicide layer SC, the contact region CTR, the active region AR immediately below the contact region CTR, and the well region NWL are in contact with each other. Therefore, the input-side contact CT1 and the output-side contact CT2 are formed to be electrically coupled to the well region NWL.

[0134] By the processes described above, the well resistance element is completed. The input-side contact CT1 and the output-side contact CT2 of the well resistance element are coupled to other electrode, terminal, and the like, so that a circuit in which an element including the other electrode and terminal is coupled to the well resistance element is formed.

[0135] Further, by the processes described above, the separation insulating film SI in the intermediate region is formed to extend in a direction crossing a direction connecting the input-side contact CT1 and the output-side contact CT2 in plan view. The contact region CTR is formed between the input-side contact CT1 and the well region NWL and between the output-side contact CT2 and the well region NWL.

[0136] Next, operation and effect of the present embodiment will be described with reference to comparative examples in FIGS. 71 to 81.

[0137] With reference to FIGS. 71 to 73, a resistance element region RE of a first comparative example of the present embodiment is formed so that a p-type silicon semiconductor substrate SUB mainly includes the well region NWL, the contacts CT1 and CT2, the separation insulating film SI, and the active region AR in the same manner as the resistance element region RE of the present embodiment. However, in the comparative example, no active region AR is arranged in the intermediate region between the input-side contact CT1 and the output-side contact CT2 (except for a region immediately below the silicide layer SC and the contact region CTR around the contacts CT1 and CT2 in plan view) and the entire surface of the region is covered by the separation insulating film SI.

[0138] In this case, as shown in FIGS. 72 and 73, in particular in the intermediate region, so-called dishing occurs in the uppermost surface DSH of the separation insulating film SI, so that the uppermost surface DSH may have a curved shape whose center portion is curved downward in the drawings as compared with the end portions. Here, a process in which in particular the curved uppermost surface DSH of the well resistance element of the first comparative example is formed will be described with reference to FIGS. 74 to 78.

[0139] With reference to FIG. 74, a plurality of mask patterns SN is formed over the main surface S1 of the semiconductor substrate SUB in the same manner as in the process of FIGS. 9A and 9B. Also here, the mask pattern SN is formed immediately above a region where the active region AR is finally formed. Therefore, the number of mask patterns SN is smaller than that of FIG. 9A, so that the distance between a pair of mask patterns SN adjacent to each other in FIG. 74 is significantly greater than that in FIG. 9A.

[0140] With reference to FIG. 75, in the same manner as in the process of FIGS. 10A and 10B, normal etching is performed by using the mask patterns SN as an etching mask and a plurality of trenches TCH is formed in the semiconductor substrate SUB.

[0141] With reference to FIG. 76, in the same manner as in the process of FIGS. 11A and 11B, the insulating film II is formed so as to fill the inside of the trenches TCH and cover the surface of the mask patterns SN.

[0142] With reference to FIG. 77, in the same manner as in the process of FIGS. 12A and 12B, the insulating film II is polished by, for example, the CMP until the upper surfaces of the mask patterns SN are exposed.

[0143] At this time, in a region between a pair of portions of the semiconductor substrate SUB which protrude upward in FIG. 77 (a region that will be the intermediate region later), the width of the region is large, so that the flatness of the uppermost surface of the insulating film II after polishing deteriorates due to a difference of polishing rate between the silicon oxide film of the insulating film II and the silicon nitride film of the mask pattern SN. Specifically, in the region described above, the uppermost surface of the insulating film II has a shape whose center portion is curved downward as compared with the end portions.

[0144] With reference to FIG. 78, in the same manner as in the processes of FIGS. 13A, 13B, 14A, and 14B, subsequently, the insulating film II in a region whose height is the same as that of the mask pattern SN is removed by etching using hydrofluoric acid or the like. At this time, the uppermost surface has already been curved in the process of FIG. 77, so that if the amount etched downward from the uppermost surface is substantially the same in the entire region, the state in which the uppermost surface of the insulating film II is curved is maintained even after the etching.

[0145] Although not shown in the drawings, if the well region is formed by an ion implantation technique which is a post-process in the same manner as in the process of FIGS. 15A and 15B in a state in which the uppermost surface of the insulating film II is curved in a region to be the intermediate region, the shape of the well region to be formed varies. Specifically, in particular, the thickness (the depth in the vertical direction in FIG. 78) of the insulating film II varies for each position, so that the depth of the well region formed immediately below the insulating film II varies for each position. An electric current flows through the well region and thereby the well region functions as the well resistance element, so that if the cross-sectional shape such as the depth of the well region varies, the resistance value of the well resistance element varies and it is difficult to improve the accuracy of the resistance value of the well resistance element.

[0146] However, in the present embodiment, a plurality of separation insulating films SI and a plurality of active regions AR are formed so that the separation insulating film SI and the active region AR are alternately and repeatedly arranged in a region to be the intermediate region. Therefore, the width of the separation insulating film SI is smaller than that in the first comparative example. Thus, even when the uppermost surface of the separation insulating film SI is polished by the CMP in the manufacturing process as described above, the possibility that the uppermost surface of the separation insulating film SI forms dishing is reduced. Therefore, the variation of the depth of the well region formed immediately below the separation insulating film SI is also reduced, so that it is possible to improve the accuracy of the well resistance element.

[0147] Next, with reference to FIG. 79, in a resistance element region RE of a second comparative example of the present embodiment, a pattern of the small active regions AR are arranged in a matrix form with a gap between them in the intermediate region between the contact CT1 and the contact CT2. Five small active regions AR are arranged in both the vertical direction and the horizontal direction in FIG. 79, and a pattern of the small active regions AR has a square shape in plan view. However, the pattern of the small active regions AR is not limited to the above arrangement.

[0148] With reference to FIGS. 80 and 81, the active region AR in the intermediate region is formed so as to extend from the main surface S1 of the semiconductor substrate SUB to the upper surface of the well region NWL in the vertical direction of FIGS. 80 and 81 in the same manner as the active region AR of the present embodiment and so as to be in contact with the separation insulating film SI adjacent to the active region AR, and is formed so as to contain, for example, n-type conductive impurities in the same manner as in the present embodiment.

[0149] In this case, as shown in FIGS. 80 and 81, the width of the separation insulating film SI in the intermediate region is smaller than that of the first comparative example in FIGS. 72 and 73. Therefore, even if the separation insulating film SI and the active regions AR in the intermediate region are formed by the same procedure as that of the first comparative example shown in FIGS. 74 to 78, the possibility that the dishing occurs in the uppermost surface of the insulating film II when the insulating film II is removed by the CMP is reduced. Therefore, the well resistance element of the second comparative example can reduce the variation of the shape (the depth) of the well region NWL more than the well resistance element of the first comparative example, so that it is possible to improve the accuracy.

[0150] However, with reference to FIG. 79, in the second comparative example, there is a possibility that the path of the electric current flowing through the well resistance element from the input-side contact CT1 varies. Specifically, for example, as indicated by an arrow represented by A in FIG. 79, normally, the electric current in the well resistance element flows from the input-side contact CT1 through the silicide layer SC immediately below the input-side contact CT1, the contact region CTR, the active region AR, and the well region NWL to the output-side contact CT2. The resistance value of the well resistance element is designed by assuming that the electric current flows through the well region NWL in this way.

[0151] However, there is a case in which a part of the electric current flowing from the input-side contact CT1 through the well resistance element does not pass through the path indicated by the aforementioned A, but passes through another path. Specifically, for example, as indicated by an arrow represented by B in FIG. 79, the electric current flows from the input-side contact CT1 through the silicide layer SC in the horizontal direction and thereafter flows to the separation insulating film SI in the intermediate region.

[0152] First, the electric current flows through the separation insulating film SI having a large resistance value. However, the electric current tends to flow through the small active region AR which is a region having a smaller resistance value, so that the electric current flows to a nearby active region AR. However, the active region AR is small, so that even when the electric current flows into the active region AR, there is a high probability that the electric current pass through the active region AR soon and flows through the separation insulating film SI.

[0153] The electric current repeats such a flow, so that the electric current may meander as indicated by an arrow B in FIG. 79 in plan view. Further, electric currents from a region surrounding the active region AR having a small square shape converge into the active region AR, so that the electric current density in the active region AR increases and the electric current density in the separation insulating film SI around the active region AR decreases. Therefore, unevenness of the electric current density occurs in the intermediate region. As a result, electric field concentration occurs in the active region AR and the withstand voltage of the entire well resistance element may decrease. The well resistance element is designed to have a function to realize high withstand voltage under high voltage environment, so that it is required to suppress the decrease of withstand voltage as described above.

[0154] Therefore, in the present embodiment, (as shown in FIG. 3), the separation insulating film SI and the active region AR (over the upper surface of the well region NWL) in the intermediate region have an elongated shape (a striped shape) in plan view, and the separation insulating film SI and the active region AR are formed to be alternately and repeatedly arranged. In particular, in the present embodiment, the separation insulating film SI in the intermediate region extends in a direction crossing a direction connecting the input-side contact CT1 and the output-side contact CT2 in plan view. Thereby, (on the upper surface) in the intermediate region, the separation insulating films SI are arranged in the entire region, where the separation insulating films SI are arranged, in the horizontal direction in FIG. 3, and the active regions AR are arranged in the entire region, where the active regions AR are arranged, in the horizontal direction in FIG. 3. Therefore, even when the electric current flowing out from the input-side contact CT1 flows out in a spreading manner from the silicide layer SC in any direction with respect to the horizontal direction of FIG. 3, (in a region above the well region NWL in FIGS. 4 and 5) the electric current inevitably flows through a path where the separation insulating film SI and the active region AR alternately appear.

[0155] In the present embodiment, when the electric current flows from the input-side contact CT1 to the output-side contact CT2 through a region above the well region NWL and spreads in a direction crossing the flowing direction, the electric current inevitably passes through the separation insulating film SI. Therefore, the electric current avoids passing through a region above the well region NWL and flows through the well region NWL with less resistance. Therefore, the function as an insulating film (a film that does not pass an electric current) of the separation insulating film SI is ensured, so that it is possible to increase the resistance value and the withstand voltage of the well resistance element. Further, when the electric current can be flown through only the well region, it is possible to accurately control the resistance value of the well resistance element by the design of the cross-sectional shape of the well region NWL.

[0156] Therefore, in the present embodiment, the occurrence of meandering of the electric current as indicated by the arrow B in FIG. 79 is suppressed. The path of the electric current becomes substantially constant regardless of the traveling direction of the electric current, so that it is possible to suppress extreme increase in the current density at a specific position and to suppress occurrence of electric field concentration following the extreme increase in the current density. Thereby, even when the well resistance element is used under the condition of high voltage, it is possible to maintain the withstand voltage of the well resistance element. Further, even when the plane area of the well resistance element is further reduced and the distance between the input-side contact CT1 and the output-side contact CT2 is shortened in the future, it is possible to suppress decrease in the withstand voltage of the well resistance element.

[0157] In the intermediate region, the uppermost surfaces of the separation insulating films SI and the active regions AR are formed to be the same surface (flush), so that, for example, the dimensions of the separation insulating films SI and the active regions AR in the vertical direction of FIG. 4 are substantially the same. For this reason, it is also possible to obtain an effect to suppress the electric field concentration in the vertical direction of FIG. 4.

[0158] The configuration as described above can be realized by performing a process in which in the process to form the separation insulating films, the insulating film II formed so as to cover the mask patterns SN and fill the trenches TCH is removed by polishing or the like until the mask patterns SN are exposed and thereafter the mask patterns SN and each insulating film II between the mask patterns SN are removed by etching or the like. When the separation insulating films are formed by the procedure as described above, the mask patterns SN and the insulating films II are not polished at the same time by the CMP, so that it is possible to suppress the occurrence of the dishing due to a difference of polishing rate of CMP or the like between the mask pattern SN and the separation insulating film SI in the above process.

[0159] Here, a reduction effect of the variation of the resistance value of the well resistance element of the present embodiment and the well resistance element of the first comparative example will be described. With reference to FIG. 18, the horizontal axis of the graph represents the reciprocal of the square root of the area of the well resistance element in plan view and the vertical axis of the graph represents the variation of the resistance value of the well resistance element.

[0160] For example, in the case of the well resistance element of the first comparative example (FIG. 71), the variation of the resistance value is about .+-.7%. However, in the case of the well resistance element of the present embodiment (FIG. 3), the variation of the resistance value is .+-.1.4%. Therefore, it is possible to reduce the variation of the resistance value of the well resistance element to about 1/5 by employing the present embodiment. Further, by employing the present embodiment, as the variation of the resistance value decreases, the value of local variation that represents a mismatch coefficient of the resistance value in the chip region IMC (see FIG. 1) where the well resistance element is formed is reduced to about 1/5 in the same manner as the above. Therefore, when the well resistance element of the present embodiment is employed, it is possible to reduce the area of the well resistance element to about 1/25 of the area of the well resistance element of the first comparative example.

[0161] As described above, in the present embodiment, the variation of the resistance value of the well resistance element can be reduced and the electric field concentration can be avoided. Therefore, it is possible to reduce the plane area of the well resistance element to obtain the same resistance value, so that it is possible to reduce the area of a chip region where the well resistance element is formed.

Second Embodiment

[0162] First, a well resistance element arranged in a resistance element region RE of the present embodiment will be described with reference to FIGS. 19 to 22.

[0163] With reference to FIGS. 19 to 22, in the resistance element region RE of the present embodiment, a well resistance element is arranged, which is formed so that a p-type silicon semiconductor substrate SUB mainly includes the well region NWL, the contacts CT1 and CT2, the separation insulating films SI, and the active regions AR basically in the same manner as the well resistance element of the first embodiment. In the intermediate region between the input-side contact CT1 and the output-side contact CT2, the separation insulating film SI and the active regions AR, each of which has an elongated shape in plan view, are alternately and repeatedly arranged to be in contact with the upper surface of the well region NWL.

[0164] However, in the present embodiment, the separation insulating film SI and the active region AR in the intermediate region extend in a direction (the vertical direction of FIG. 19) along the direction connecting the input-side contact CT1 and the output-side contact CT2 in plan view. As a result, in particular as shown in FIG. 22, the separation insulating film SI and the active region AR are alternately and repeatedly arranged over the upper surface of the well region NWL in the horizontal direction of FIG. 19.

[0165] A plurality of (here, five) input-side contacts CT1 and a plurality of (here, five) output-side contacts CT2 may be arranged in the horizontal direction of FIG. 19 with a gap between them. It is preferable that the number of the arranged input-side contacts CT1 and the number of the arranged output-side contacts CT2 are the same. Here, one of the input-side contacts CT1 and one of the output-side contacts CT2 are arranged to face each other in the vertical direction of FIG. 19. A plurality of (here, five) active regions AR is arranged to couple each of the input-side contacts CT1 to an output-side contact CT2 facing the input-side contact CT1. The active regions AR are arranged with a gap between them in the horizontal direction of FIG. 19 and the separation insulating film SI is arranged in each region between a pair of active regions AR adjacent to each other.

[0166] In a region along the line XX-XX that does not pass through the contacts CT1 and CT2 and passes through the separation insulating film SI, as shown in FIG. 20, the entire upper surface of the well region NWL in the intermediate region between a pair of active regions AR (arranged immediately below the contact regions CTR) is covered by the separation insulating film SI. The uppermost surface of the active region AR (silicide layer SC) and the uppermost surface of the separation insulating film SI are the same surface (the same surface as the main surface of the semiconductor substrate SUB).

[0167] In a region along the line XXI-XXI that passes through the contacts CT1 and CT2 and passes through the active region AR, as shown in FIG. 21, the entire upper surface of the well region NWL in the intermediate region between a pair of active regions AR (arranged immediately below the contact regions CTR) is covered by the active region AR. The active region AR in the intermediate region and the active regions AR immediately below the contact regions CTR are integrated together.

[0168] The configuration of the MOS transistor formed in the transistor region TR is the same as that of the first embodiment, so that the detailed description is omitted here (the same goes for embodiments described hereinafter).