Semiconductor Package Including A Step Type Substrate

LEE; Kyu Won ; et al.

U.S. patent application number 14/882557 was filed with the patent office on 2016-12-29 for semiconductor package including a step type substrate. The applicant listed for this patent is SK hynix Inc.. Invention is credited to Cheol Woo HAN, Kyu Won LEE, Ki Ill MOON.

| Application Number | 20160379961 14/882557 |

| Document ID | / |

| Family ID | 55906084 |

| Filed Date | 2016-12-29 |

| United States Patent Application | 20160379961 |

| Kind Code | A1 |

| LEE; Kyu Won ; et al. | December 29, 2016 |

SEMICONDUCTOR PACKAGE INCLUDING A STEP TYPE SUBSTRATE

Abstract

Disclosed herein are semiconductor packages. A semiconductor package may include a substrate configured to include a first face and a second face opposite the first face and to have a recess formed in the first face. The semiconductor package may include a first semiconductor chip disposed on the bottom of the recess. The semiconductor package may include a second semiconductor chip disposed on the second face of the substrate. The semiconductor package may include a third semiconductor chip disposed over the first face of the substrate and the first semiconductor chip. The semiconductor package may include a fourth semiconductor chip disposed over the third semiconductor chip.

| Inventors: | LEE; Kyu Won; (Seoul, KR) ; MOON; Ki Ill; (Seoul, KR) ; HAN; Cheol Woo; (Cheongju-si Chungcheongbuk-do, KR) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 55906084 | ||||||||||

| Appl. No.: | 14/882557 | ||||||||||

| Filed: | October 14, 2015 |

| Current U.S. Class: | 257/738 |

| Current CPC Class: | H01L 23/49822 20130101; H01L 2225/06555 20130101; H01L 2225/06562 20130101; H01L 2924/15311 20130101; H01L 2924/181 20130101; H01L 2225/06572 20130101; H01L 2224/73253 20130101; H01L 2225/06517 20130101; H01L 25/0657 20130101; H01L 2225/06513 20130101; H01L 2225/06558 20130101; H01L 23/49816 20130101; H01L 23/3128 20130101; H01L 2225/06586 20130101; H01L 2225/0651 20130101; H01L 2924/181 20130101; H01L 23/13 20130101; H01L 2924/00012 20130101; H01L 2924/15153 20130101; H01L 2224/16225 20130101; H01L 2224/32145 20130101 |

| International Class: | H01L 25/065 20060101 H01L025/065 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Jun 26, 2015 | KR | 10-2015-0090940 |

Claims

1. A semiconductor package, comprising: a substrate having a first face and a second face opposite the first face, and having a recess formed in the first face; a first semiconductor chip disposed to a bottom of the recess; a second semiconductor chip disposed to the second face of the substrate; a third semiconductor chip disposed over the first face of the substrate and the first semiconductor chip; a fourth semiconductor chip disposed over the third semiconductor chip, wherein each of the first to fourth semiconductor chips comprises an active face and a back side opposite the active face, and the first to fourth semiconductor chips comprise first to fourth bonding pads arranged adiacently to an edge and another edge opposing the edge of each of the active faces, wherein the third semiconductor chip is disposed to the first face of the substrate through a plurality of flip chip bumps so that the active face of the third semiconductor chip faces the first face of the substrate and the back side of the first semiconductor chip, and wherein the fourth semiconductor chip is disposed over the back side of the third semiconductor chip so that the back side of the fourth semiconductor chip faces the back side of the third semiconductor chip, first to third bumps configured to electrically couple between the substrate and the first to third semiconductor chips; and a bonding wire configured to electrically couple the substrate and the fourth semiconductor chip.

2. The semiconductor package of claim 1, wherein the first semiconductor chip is disposed to the bottom of the recess through a plurality of flip-chip bumps, and wherein the second semiconductor chip is disposed to the second face of the substrate through a plurality of flip-chip bumps.

3. The semiconductor package of claim 1, wherein the substrate comprises: first bonding fingers arranged in the bottom of the recess, second bonding fingers arranged in the second face, third bonding fingers arranged in portions of the first face outside the recess, and fourth bonding fingers arranged in portions of the first face outside the third bonding fingers.

4. The semiconductor package of claim 3, wherein the substrate further comprises ball lands arranged in portions of the second face of the substrate outside the second bonding fingers.

5. The semiconductor package of claim 1, wherein a length of the recess in a second direction perpendicular to a first direction is longer than a length of the recess in the first direction.

6. (canceled)

7. The semiconductor package of claim 1, wherein each of the first semiconductor chip and the second semiconductor has a longer length in a second direction perpendicular to a first direction than a length in the first direction in response to the recess and generally have an identical size and shape each other.

8. The semiconductor package of claim 1, wherein each of the third semiconductor chip and the fourth semiconductor chip has a longer length in a first direction than a length in a second direction perpendicular to the first direction and generally have an identical size and shape each other.

9-10. (canceled)

11. The semiconductor package of claim 1, further comprising an adhesive member interposed between the back side of the third semiconductor chip and the back side of the fourth semiconductor chip.

12. A semiconductor package, comprising: a substrate having a first face and a second face opposite the first face, and having a recess formed in the first face; a first semiconductor chip disposed to a bottom of the recess; a second semiconductor chip disposed to the second face of the substrate; a third semiconductor chip disposed over the first face of the substrate and the first semiconductor chip; and a fourth semiconductor chip disposed over the third semiconductor chip, wherein each of the first to fourth semiconductor chips comprises an active face and a back side opposite the active face, and the first to fourth semiconductor chips comprise first to fourth bonding pads arranged adjacently to an edge and another edge opposing the edge of each of the active faces, and wherein the third semiconductor chip is disposed over the first face of the substrate so that the back side of the third semiconductor chip faces the first face of the substrate and the back side of the first semiconductor chip, and wherein the fourth semiconductor chip is disposed over the active face of the third semiconductor chip so that the back side of the fourth semiconductor chip faces the active face of the third semiconductor chip.

13. The semiconductor package of claim 12, further comprising: first and second bumps configured to electrically couple the substrate and the first and the second semiconductor chips; and first and second bonding wires configured to electrically couple the substrate and the third and the fourth semiconductor chips.

14. The semiconductor package of claim 12, further comprising: a first adhesive member interposed between the first face of the substrate and the back side the first semiconductor chip and the back side of the third semiconductor chip; and a second adhesive member interposed between the active face of the third semiconductor chip and the back side of the fourth semiconductor chip.

15. The semiconductor package of claim 14, wherein the second adhesive member comprises a penetrate wafer backside lamination (PWBL) film.

16. The semiconductor package of claim 1, further comprising a sealing member formed on the first face of the substrate to substantially cover the first, the third, and the fourth semiconductor chips and formed on the second face of the substrate to substantially cover the second semiconductor chip.

17. The semiconductor package of claim 16, wherein the sealing member is substantially formed on the first face of the substrate and is only partially formed on the second face of the substrate.

18. The semiconductor package of claim 17, wherein the sealing member is formed to bury the recess in which the first semiconductor chip has been disposed.

19. The semiconductor package of claim 4, further comprising external connection electrodes formed on the ball lands arranged in the second face of the substrate.

20. The semiconductor package of claim 19, wherein the external connection electrodes comprise solder balls, the solder ball having a height identical with or greater than a thickness of a sealing member formed on the second face of the substrate.

21. The semiconductor package of claim 12, wherein the substrate comprises: first bonding fingers arranged in the bottom of the recess, second bonding fingers arranged in the second face, third bonding fingers arranged in portions of the first face outside the recess, fourth bonding fingers arranged in portions of the first face outside the third bonding fingers, and ball lands arranged in portions of the second face of the substrate outside the second bonding fingers.

22. The semiconductor package of claim 12, wherein a length of the recess in a second direction perpendicular to a first direction is longer than a length of the recess in the first direction, wherein each of the first semiconductor chip and the second semiconductor has a longer length in a second direction perpendicular to a first direction than a length in the first direction in response to the recess and generally have an identical size and shape each other, and each of the third semiconductor chip and the fourth semiconductor chip has a longer length in a first direction than a length in a second direction perpendicular to the first direction and generally have an identical size and shape each other.

23. The semiconductor package of claim 12, further comprising a sealing member formed on the first face of the substrate to substantially cover the first, the third, and the fourth semiconductor chips and formed on the second face of the substrate to substantially cover the second semiconductor chip.

Description

CROSS-REFERENCE TO RELATED APPLICATION

[0001] The present application claims priority under 35 U.S.C. .sctn.119(a) to Korean Patent Application No. 10-2015-0090940 filed on Jun. 26, 2015, in the Korean Intellectual Property Office, which is incorporated herein by reference in its entirety.

BACKGROUND

[0002] 1. Technical Field

[0003] Various embodiments generally relate to a semiconductor package, and more particularly, to a semiconductor package including a step type substrate.

[0004] 2. Related Art

[0005] As electronic products are reduced in size and have higher functionality, semiconductor chips having higher capacities have been required to satisfy certain functions. Furthermore, there has been a need to mount a larger number of semiconductor chips on an electronic product having a smaller size.

[0006] However, technologies in which a semiconductor chip having a high capacity is manufactured or a larger number of semiconductor chips are disposed in a limited space have reached their limits. Thus, recently, a larger number of semiconductor chips are now being embedded in a single package.

[0007] To this end, various technologies have been developed in which one or more semiconductor chips are embedded and electrical properties are improved without increasing a total thickness of a package.

SUMMARY

[0008] In an embodiment, a semiconductor package may be provided. The semiconductor package may include a substrate configured to include a first face and a second face opposite the first face and to have a recess formed in the first face. The semiconductor package may include a first semiconductor chip disposed to the bottom of the recess, and a second semiconductor chip disposed to the second face of the substrate. The semiconductor package may include a third semiconductor chip disposed over the first face of the substrate and the first semiconductor chip. The semiconductor package may include a fourth semiconductor chip disposed over the third semiconductor chip.

[0009] In an embodiment, an electronic system may be provided. The electronic system to which a semiconductor package has been applied may include a controller, an interface, an input/output device, and a memory device coupled by a bus. The controller and the memory device may include a semiconductor package, including a substrate configured to include a first face and a second face opposite the first face and to have a recess formed in the first face, a first semiconductor chip disposed to the bottom of the recess, a second semiconductor chip disposed to the second face of the substrate, a third semiconductor chip disposed over the first face of the substrate and the first semiconductor chip, and a fourth semiconductor chip disposed over the third semiconductor chip.

[0010] In an embodiment, a memory card may be provided. The memory card may include a semiconductor package. The memory card may include memory including a semiconductor package and a memory controller to control the memory. The semiconductor package may include a substrate configured to include a first face and a second face opposite the first face and to have a recess formed in the first face, a first semiconductor chip disposed to the bottom of the recess, a second semiconductor chip disposed to the second face of the substrate, a third semiconductor chip disposed over the first face of the substrate and the first semiconductor chip, and a fourth semiconductor chip disposed over the third semiconductor chip.

BRIEF DESCRIPTION OF THE DRAWINGS

[0011] FIG. 1 is a plan view illustrating a representation of an example of a semiconductor package according to an embodiment other than a sealing member.

[0012] FIG. 2 is a bottom view illustrating a representation of an example of the semiconductor package according to an embodiment.

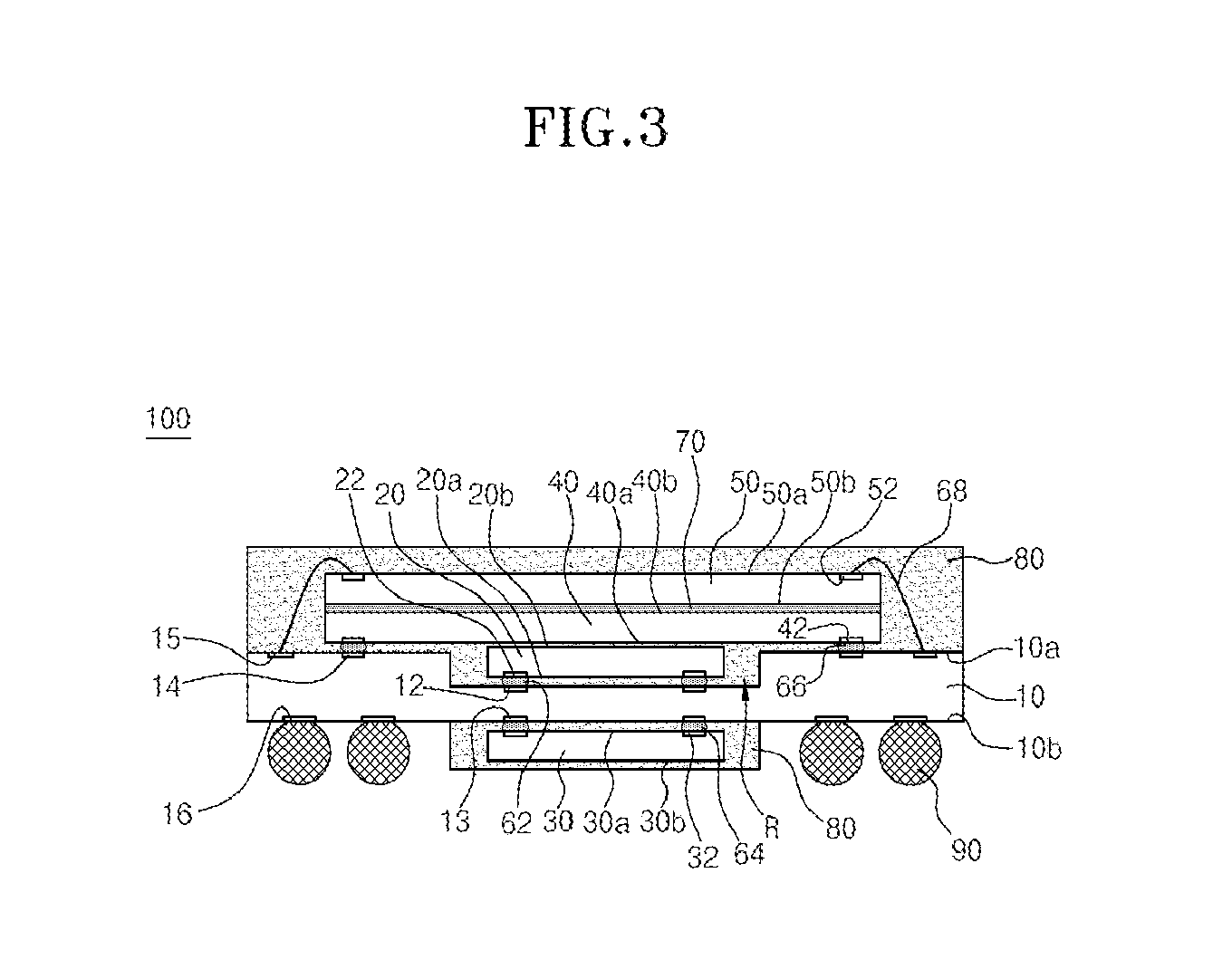

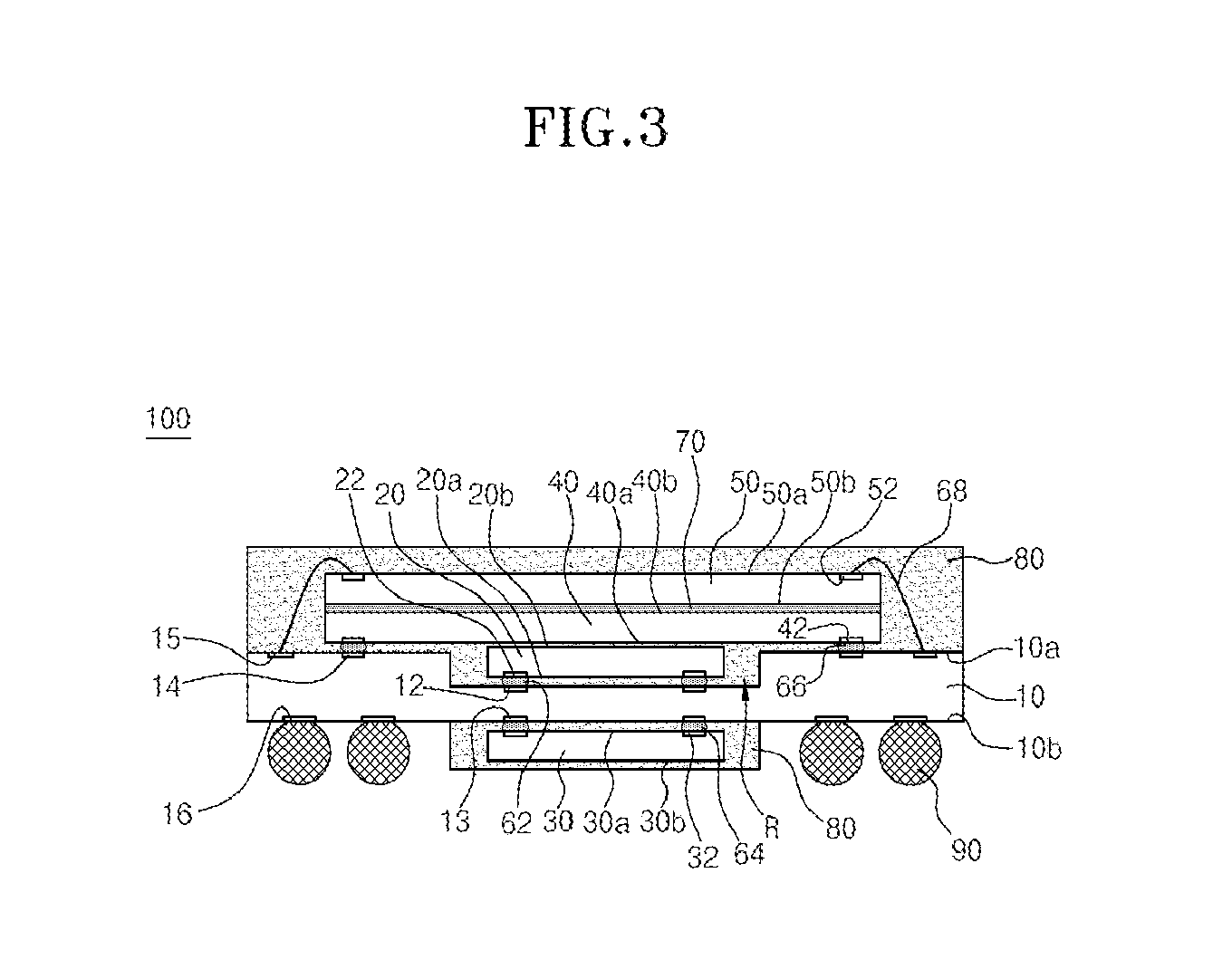

[0013] FIG. 3 is a cross-sectional view illustrating a representation of an example of the semiconductor package taken along line A-A' of FIG. 1 according to an embodiment.

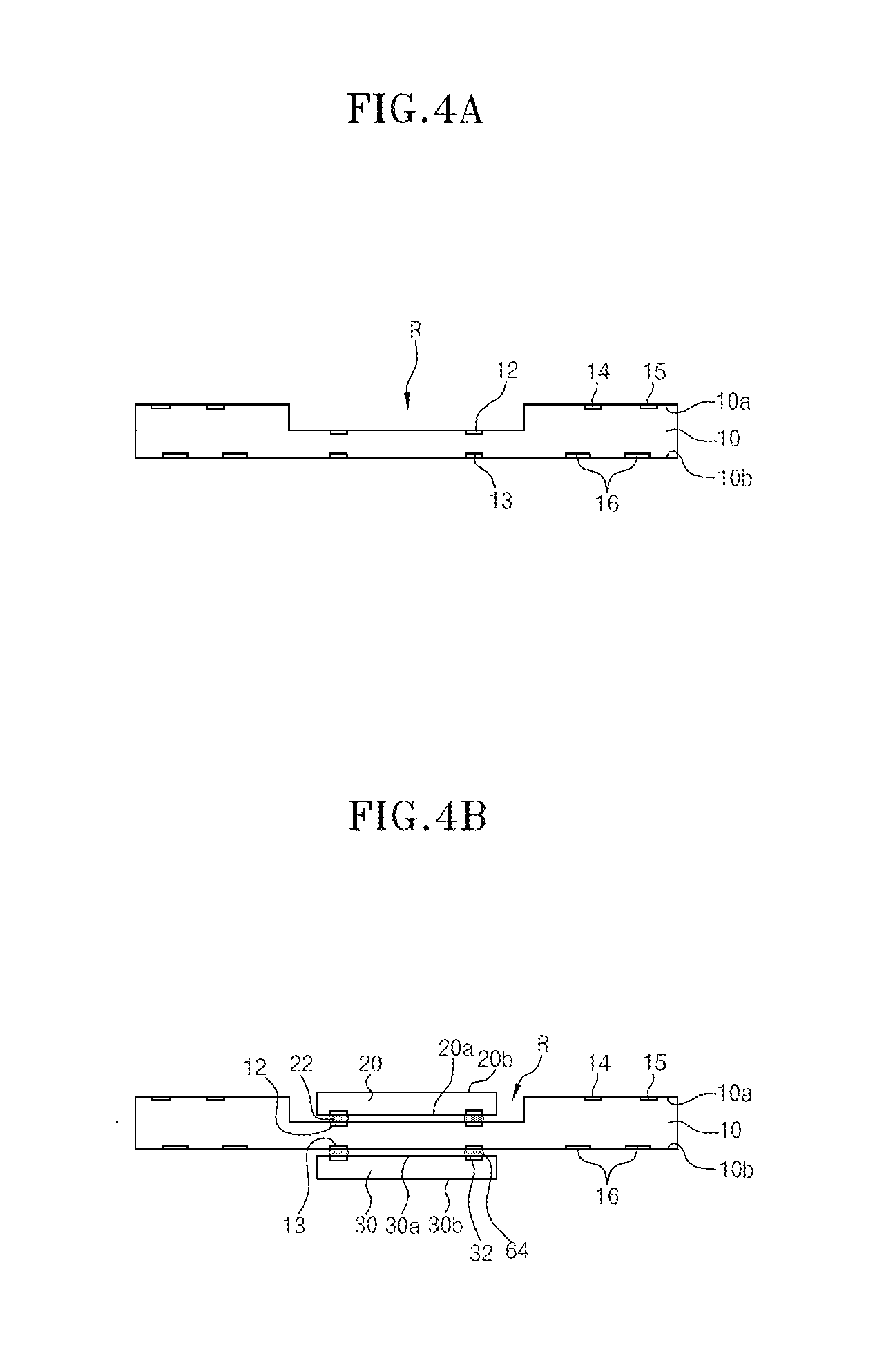

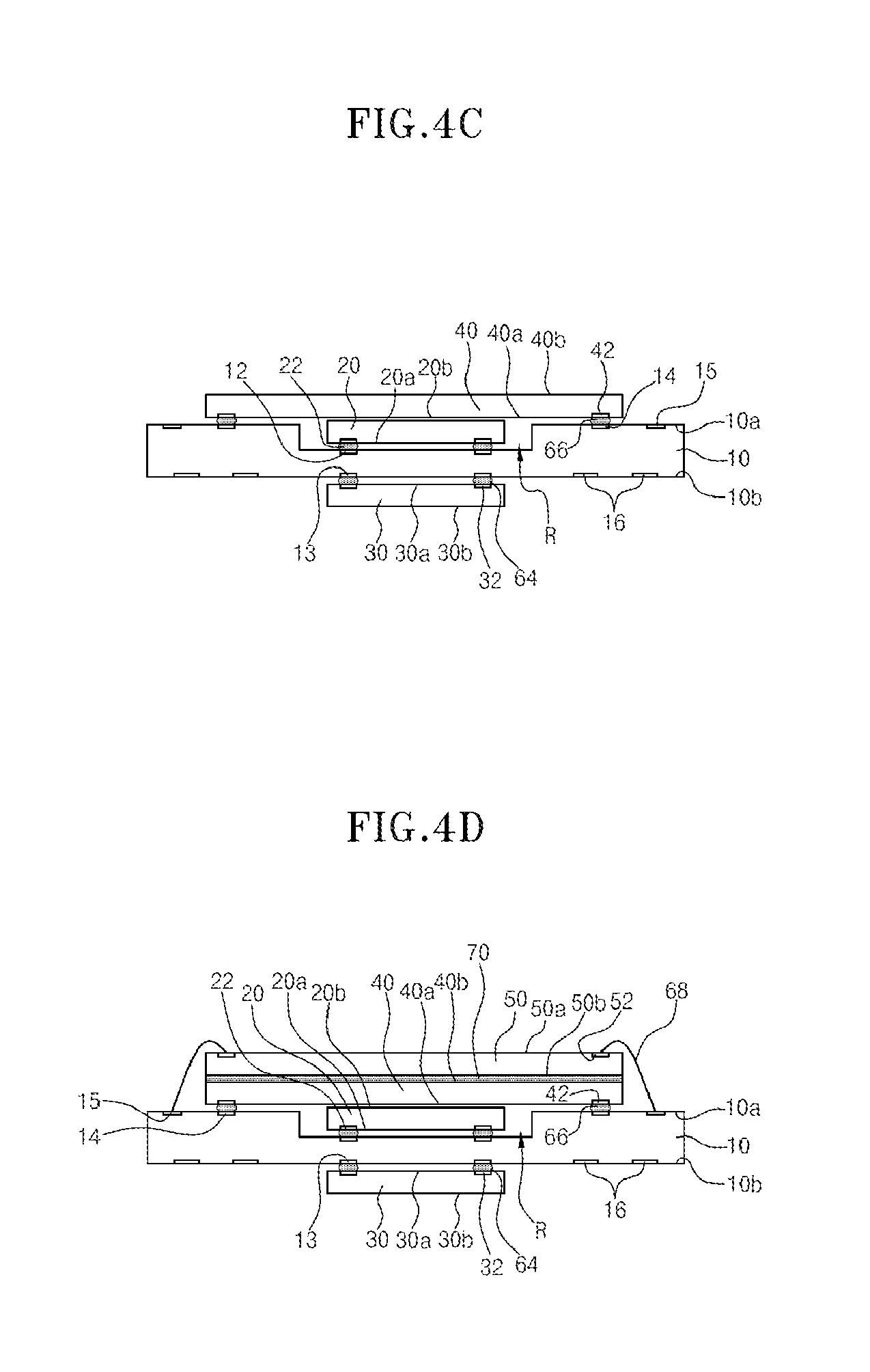

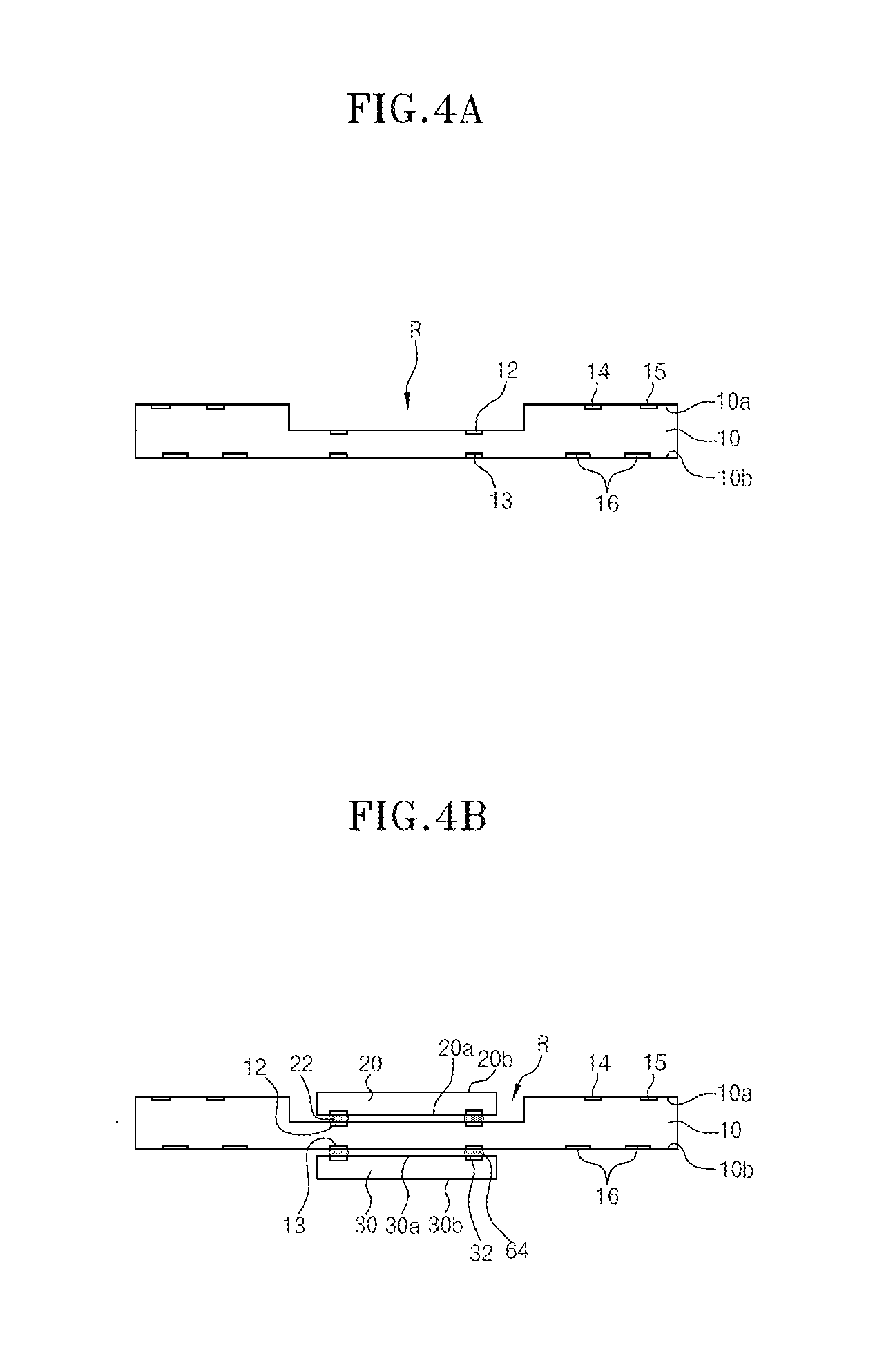

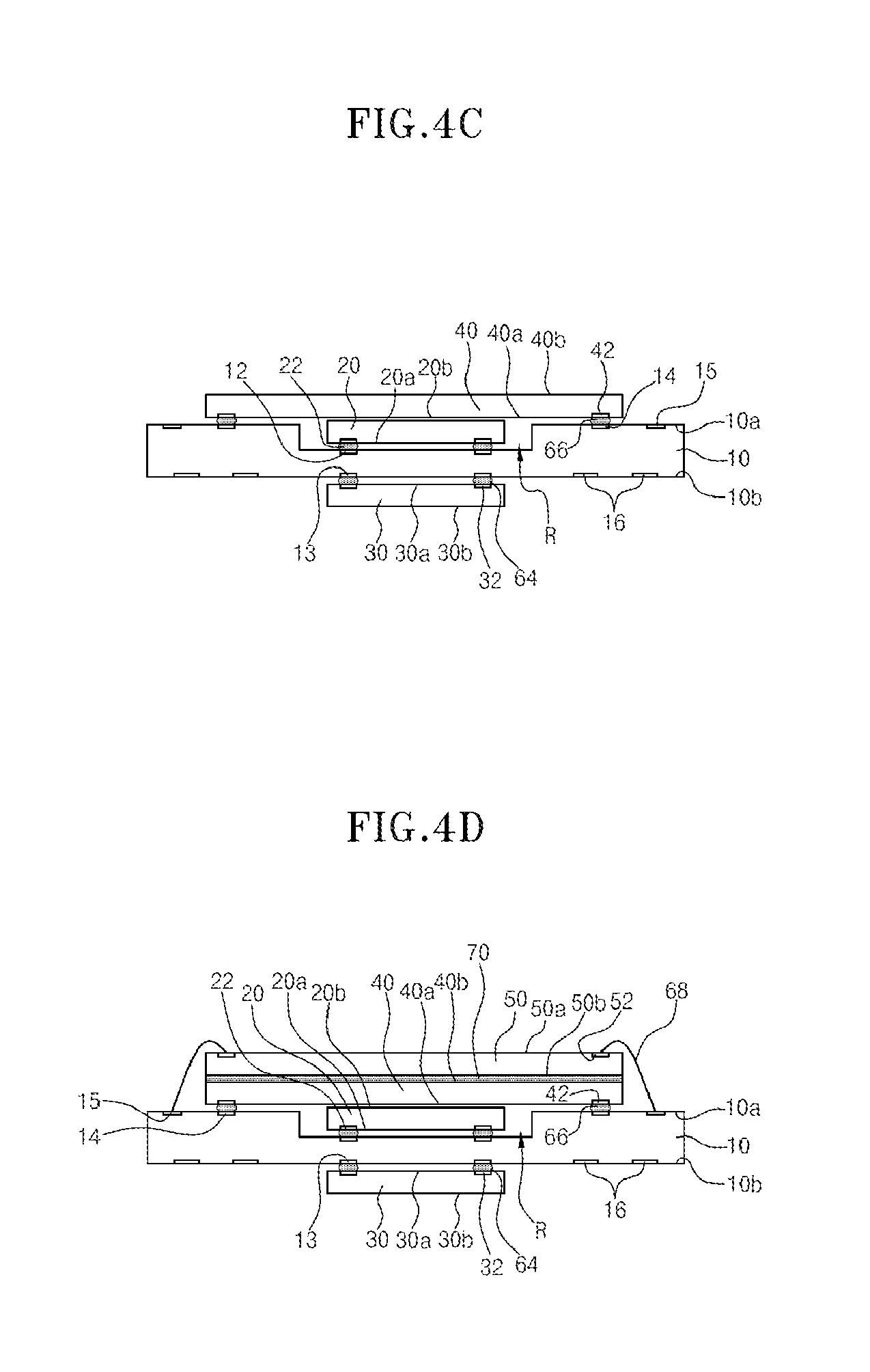

[0014] FIGS. 4A to 4F are cross-sectional views illustrating representations of examples for each process which illustrate a method of manufacturing a semiconductor package according to an embodiment.

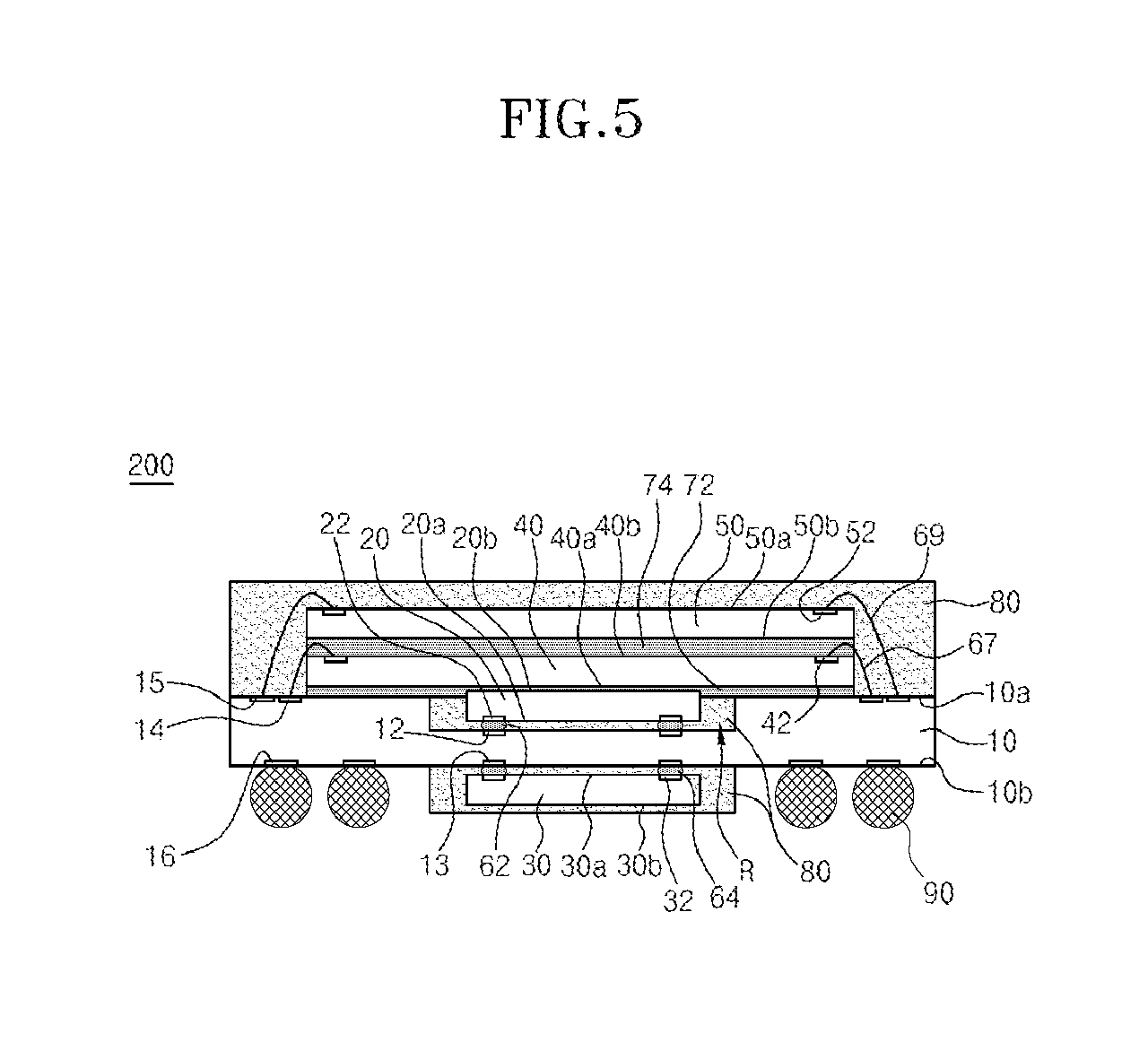

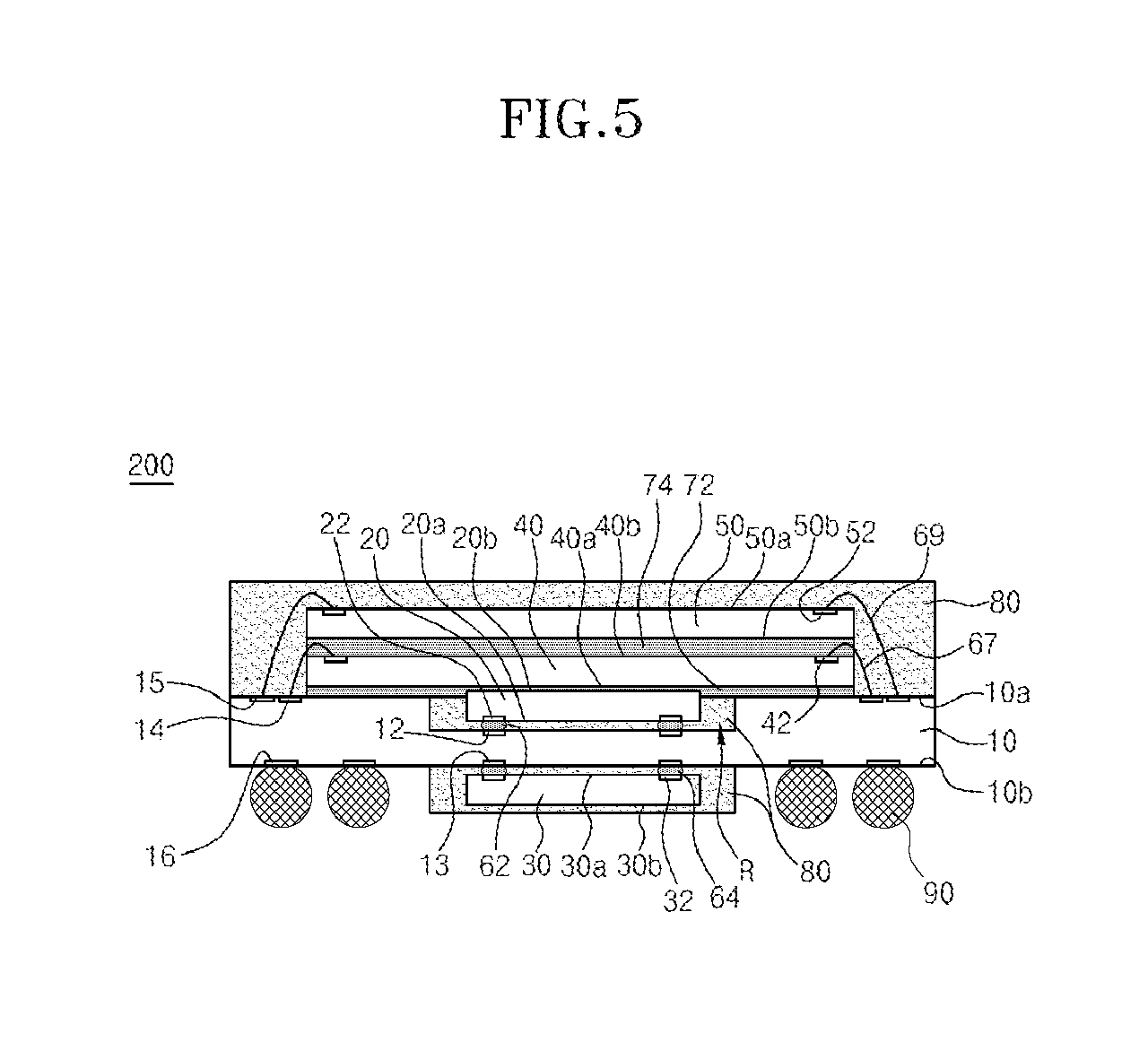

[0015] FIG. 5 is a cross-sectional view illustrating a representation of an example of a semiconductor package according to an embodiment.

[0016] FIG. 6 is a block diagram illustrating a representation of an example of an electronic system to which a semiconductor package according to various embodiments has been applied.

[0017] FIG. 7 is a block diagram illustrating a representation of an example of a memory card including a semiconductor package according to various embodiments.

DETAILED DESCRIPTION

[0018] Hereinafter, a semiconductor package including a step type substrate may be described below with reference to the accompanying drawings through various examples of embodiments.

[0019] Various embodiments may provide a semiconductor package including a step type substrate.

[0020] Referring to FIGS. 1 to 3, a semiconductor package 100 according to an embodiment may include a substrate 10, semiconductor chips 20, 30, 40, and 50, first to third bumps 62, 64, and 66, bonding wires 68, a sealing member 80, and external connection electrodes 90. The semiconductor package 100 according to an embodiment may include an adhesive member 70.

[0021] The substrate 10 may be a printed circuit substrate of a multi-layer structure, for example. The substrate 10 may generally have a square plate shape when viewed on a plane. The substrate 10 may have a first face 10a corresponding to the top and a second face 10b facing the first face 10a and corresponding to the bottom. The substrate 10 may have a recess R in the first face 10a thereof so that it has a step type in terms of a cross section. When viewed on a plane, the recess R may have a rectangular shape in which a length in a first direction X is shorter than a length in a second direction Y perpendicular to the first direction X. The recess R may be formed in the central part of the first face 10a of the substrate 10 in such a way as to extend in the second direction Y. In an embodiment, the first direction may be an X direction, and the second direction may be a Y direction.

[0022] The substrate 10 may include a plurality of first bonding fingers 12 arranged at the bottom of the recess R, a plurality of third and fourth bonding fingers 14 and 15 arranged in the first face 10a, and second bonding fingers 13 arranged in the second face 10b. The substrate 10 may include a plurality of ball lands 16 arranged in the second face 10b. In an embodiment, the first bonding fingers 12 may be formed so that they are arranged in the second direction Y at edges that belong to the bottom of the recess R and that are placed on both sides in the first direction X. The second bonding fingers 13 may be formed so that they are arranged in portions of the second face 10b of the substrate 10 that faces the first bonding fingers 12. The third bonding fingers 14 may be formed so that they are arranged in the second direction Y in portions of the first face 10a of the substrate 10 adjacent to the recess R in the first direction X. The fourth bonding fingers 15 may be formed so that they are arranged in the second direction Y outside the third bonding fingers 14 in the first face 10a of the substrate 10. The ball lands 16 may be arranged in plural columns outside the second bonding fingers 13 in the second face 10b of the substrate 10, for example, in two columns at respective edges on both sides of the second face 10b of the substrate 10 in the first direction X.

[0023] Although not illustrated, the substrate 10 may include circuit patterns respectively formed in the first face 10a and the second face 10b including the recess R and via patterns formed on the inner surfaces of the circuit patterns. The first to fourth bonding fingers 12, 13, 14, and 15 may be end parts of the circuit patterns. The first to fourth bonding fingers 12, 13, 14, and 15 and the ball lands 16 may be electrically coupled by the circuit patterns and the via patterns. The substrate 10 may include solder resists formed on the first face 10a and the second face 10b and formed to cover the respective circuit patterns, but to expose the first to fourth bonding fingers 12, 13, 14, and 15 and the ball lands 16.

[0024] The first semiconductor chip 20 may include an active face 20a and a back side 20b opposite the active face 20a. In an embodiment, four or more sides may be provided between the active face 20a and the back side 20b. The first semiconductor chip 20 may include a plurality of first bonding pads 22 arranged in the second direction Y at edges on both sides in the first direction X of the active face 20a. In an embodiment, the first bonding pads 22 of the active face 20a may be arranged in the second direction Y at an edge and at another edge opposing the edge. The first semiconductor chip 20 may be disposed so that the active face 20a faces the bottom of the recess R. The first semiconductor chip 20 may be dispose to flip-chip bonding through the medium of the first bumps 62 formed on the first bonding pads 22 so that the first bonding pads 22 are electrically coupled to the first bonding fingers 12.

[0025] In an embodiment, when viewed on a plane, the first semiconductor chip 20 may have a shape corresponding to the recess R, that is, a rectangular shape in which a length in the second direction Y is longer than that in the first direction X. The first semiconductor chip 20 may be a memory chip. For example, the semiconductor chip 20 may be a memory chip for a mobile.

[0026] The second semiconductor chip 30 may include an active face 30a and a back side 30b opposite the active face 30a. In an embodiment, four or more sides may be provided between the active face 30a and the back side 30b. The second semiconductor chip 30 may include a plurality of second bonding pads 32 arranged in the second direction Y at an edge on both sides in the first direction X of the active face 30a. In an embodiment, the second bonding pads 32 of the active face 30a may be arranged in the second direction Y at an edge and at another edge opposing the edge. The second semiconductor chip 30 may be disposed so that the active face 30a faces the second face 10b of the substrate 10. The second semiconductor chip 30 may be dispose to flip-chip bonding through the medium of the second bumps 64 formed on the second bonding pads 32 so that the second bonding pads 32 are electrically coupled to the second bonding fingers 13.

[0027] In an embodiment, the second semiconductor chip 30 may generally have the same shape and size as the first semiconductor chip 20. The second semiconductor chip 30 may be disposed in the second face 10b of the substrate 10. The second semiconductor chip 30 may be a memory chip like the first semiconductor chip 20. In an embodiment, the sides of the first semiconductor chip 20 may vertically align with the sides of the second semiconductor chip 30 to provide little or no overhang between the two chips as illustrated in FIGS. 1-3.

[0028] The third semiconductor chip 40 may include an active face 40a and a back side 40b opposite the active face 40a. In an embodiment, four or more sides may be provided between the active face 40a and the back side 40b. The third semiconductor chip 40 may include a plurality of third bonding pads 42 arranged in the second direction Y at edges on both sides in the first direction X of the active face 40a. In an embodiment, the third bonding pads 42 of the active face 40a may be arranged in the second direction Y at an edge and at another edge opposing the edge. The third semiconductor chip 40 may be disposed so that the active face 40a faces the first face 10a of the substrate 10 and the back side 20b of the first semiconductor chip 20. The third semiconductor chip 40 may be dispose to flip-chip bonding through the medium of the third bumps 66 formed on the third bonding pads 42 so that the third bonding pads 42 are electrically coupled to the third bonding fingers 14.

[0029] In an embodiment, when viewed on a plane, the third semiconductor chip 40 may have a rectangular shape in which a length in the first direction X is longer or much longer than that in the second direction Y. The third semiconductor chip 40 may be disposed so that it is perpendicular to the first semiconductor chip 20 or the recess R. The first semiconductor chip 20 is disposed in the recess R of the substrate 10, and the third semiconductor chip 40 is mounted on the first semiconductor chip 20 and the first face 10a of the substrate 10. In an embodiment, the first semiconductor chip 20 is disposed in the recess R of the substrate 10, and the third semiconductor chip is mounted on the first face 10a of the substrate and crosses over, passes over, or bridges over the first semiconductor chip 20 and recess R. The first directions X of the first semiconductor chip 20 and the third semiconductor chip 40 that are crossed and stacked have different lengths, but an overhang structure is not formed because part of the third semiconductor chip 40 more protruded than a boundary surface in the first direction X of the first semiconductor chip 20 is directly supported by the substrate 10. The third semiconductor chip 40 may be a memory chip.

[0030] The fourth semiconductor chip 50 may include an active face 50a and a back side 50b opposite the active face 50a. In an embodiment, four or more sides may be provided between the active face 50a and the back side 50b. The fourth semiconductor chip 50 may include a plurality of fourth bonding pads 52 arranged in the second direction Y at edges on both sides in the first direction X of the active face 50a. In an embodiment, the fourth bonding pads 52 of the active face 50a may be arranged in the second direction Y at an edge and at another edge opposing the edge. The fourth semiconductor chip 50 may be disposed on the back side 40b of the third semiconductor chip 40 through the medium of an adhesive member 70 so that the back side 50b faces the back side 40b of the third semiconductor chip 40. The fourth bonding pads 42 of the fourth semiconductor chip 50 may be electrically coupled to the fourth bonding fingers 15 of the substrate 10 by the bonding wires 68. The loop of the bonding wires 68 may be controlled by taking into consideration a total thickness of the semiconductor package 100 according to an embodiment.

[0031] In an embodiment, the fourth semiconductor chip 50 may generally have the same size and shape as the third semiconductor chip 40. That is, when viewed on a plane, the fourth semiconductor chip 50 may have a rectangular shape in which a length in the first direction X is longer than that in the second direction Y and may be disposed so that it is perpendicular to the first semiconductor chip 20. The fourth semiconductor chip 50 may be a memory chip. In an embodiment, the sides of the third semiconductor chip 40 may vertically align with the sides of the fourth semiconductor chip 50 to provide little or no overhang between the two chips as illustrated in FIGS. 1-3.

[0032] The adhesive member 70 functions to attach the fourth semiconductor chip 50 on the back side 30b of the third semiconductor chip 40 and may include an adhesive tape or an adhesive paste. The thickness of the adhesive member 70 may be properly controlled by taking into consideration a total thickness of the semiconductor package 100 according to an embodiment.

[0033] The sealing member 80 may include an epoxy molding compound. The sealing member 80 may be formed on the first face 10a of the substrate 10 so that it covers the first semiconductor chip 20, the third semiconductor chip 40, the fourth semiconductor chip 50, and the bonding wires 68 and may also be formed on part of the second face 10b of the substrate 10 so that it covers the second semiconductor chip 30. In this example, the sealing member 80 formed on the first face 10a of the substrate 10 may be formed to fill the recess R in which the first semiconductor chip 20 has been disposed.

[0034] The external connection electrodes 90 may include solder balls and may be formed on the respective ball lands 16 arranged in the second face 10b of the substrate 10. For example, the external connection electrodes 90 including solder balls may be formed by attaching the solder balls in the state in which a flux has been dotted on the ball lands 16 of the substrate 10 and reflowing the attached solder balls.

[0035] In an embodiment, the height of the solder ball may be set as a range in which the second semiconductor chip 30 and the sealing member 80 surrounding the second semiconductor chip 30 do not generate interface when the semiconductor package according to an embodiment is mounted on an external circuit, that is, a system board. In other words, the solder ball may be formed to have a height that is equal to or greater than the thickness of the sealing member 80 formed on the second face 10b of the substrate 10.

[0036] The aforementioned semiconductor package according to an embodiment is implemented by performing flip-chip bonding on the first and the second semiconductor chips over and under the step type substrate and stacking the third and the fourth semiconductor chips over the step type substrate.

[0037] Accordingly, the semiconductor package according to an embodiment can suppress a phenomenon in which the package is bent in one direction due to an asymmetrical structure because the chips are crossed and stacked. Furthermore, the semiconductor package according to an embodiment may be very stable in structure because all the semiconductor chips are firmly supported by the substrate or other chips without an overhang structure. Furthermore, the semiconductor package according to an embodiment can implement a relatively thin package compared to a package in which four semiconductor chips are vertically stacked on a substrate of the same thickness, for example, because the first semiconductor chip is disposed in the recess of the substrate. Furthermore, the semiconductor package according to an embodiment can implement a thin package because the thickness of the substrate or the external connection terminal is reduced to a minimum and the thickness of the chip is designed to determine the thickness of the package.

[0038] The semiconductor package according to an embodiment may be fabricated through the following processes.

[0039] Referring to FIG. 4A, the substrate 10 configured to include the first face 10a and the second face 10b opposite the first face 10a and to have the recess R formed in the central part of the first face 10a is prepared. As described above, when viewed on a plane, the recess R may have a shape in which a length in the second direction perpendicular to the first direction is much longer than a length in the first direction. The substrate 10 may include the plurality of first bonding fingers 12 arranged at the bottom of the recess R, the second bonding fingers 13 arranged in portions of the second face 10b of the substrate 10 corresponding to the first bonding fingers 12, the third bonding fingers 14 arranged in portions of the first face 10a adjacent to the recess R, and the fourth bonding fingers 15 arranged in portions of the first face 10a outside the third bonding fingers 14. The substrate 10 may include the ball lands 16 arranged in portions of the second face 10b outside the second bonding fingers 13.

[0040] Although not illustrated in FIG. 4A, the substrate 10 may include the circuit patterns respectively formed in the first face 10a and the second face 10b including the bottom of the recess R and the via patterns formed in the circuit patterns. Furthermore, the substrate 10 may include the solder resists formed to expose the second to fourth bonding fingers 13, 14, and 15 and the ball lands 16 on the first face 10a and the second face 10b, respectively.

[0041] Referring to FIG. 4B, the first semiconductor chip 20 is disposed at the bottom of the recess R of the substrate 10 in accordance with a flip-chip bonding method. The first semiconductor chip 20 may have a shape similar to that of the recess R of the substrate 10, but may have a smaller size than the recess R when viewed on a plane. The first semiconductor chip 20 may include the first bonding pads 22 arranged at edges on both sides of the active face 20a. The first semiconductor chip 20 is physically attached within the recess R of the substrate 10 by the first bumps 62 respectively formed on the first bonding pads 22. The first bonding pads 22 of the first semiconductor chip 20 are electrically coupled to the first bonding fingers 12 of the substrate 10.

[0042] The second semiconductor chip 30 is disposed on the second face 10b of the substrate 10 in accordance with a flip-chip bonding method. The second semiconductor chip 30 may generally have the same shape as the first semiconductor chip 20. The second semiconductor chip 30 may include the second bonding pads 32 arranged at edges on both sides of the active face 30a. The second semiconductor chip 30 is physically attached to a portion of the second face 10b of the substrate 10 corresponding to the recess R by the second bumps 64 respectively formed on the second bonding pads 22. Furthermore, the second bonding pads 32 of the second semiconductor chip 30 are electrically coupled to the second bonding fingers 13 of the substrate 10.

[0043] Referring to FIG. 4C, the third semiconductor chip 40 is disposed on the first semiconductor chip 20 and the first face 10a of the substrate 10 in accordance with a flip-chip bonding method. When viewed on a plane, the third semiconductor chip 40 may have a shape in which a length in the first direction is much greater than a length in the second direction perpendicular or substantially perpendicular to the first direction and may be disposed in such a way as to cross the first semiconductor chip 20. The third semiconductor chip 40 may include the third bonding pads 42 arranged at edges on both sides of the active face 40a of the third semiconductor chip 40. The third semiconductor chip 40 is physically attached to the first face 10a of the substrate 10 by the third bumps 66 respectively formed on the third bonding pads 42. Furthermore, the third bonding pads 42 of the third semiconductor chip 40 is electrically coupled to the third bonding fingers 14 of the substrate 10.

[0044] Referring to FIG. 4D, the fourth semiconductor chip 50 is disposed on the third semiconductor chip 40 in a space-up type. The fourth semiconductor chip 50 may generally have the same shape as the third semiconductor chip 40. The fourth semiconductor chip 50 may include the fourth bonding pads 52 arranged at edges on both sides of the active face 50a of the fourth semiconductor chip 50. The fourth semiconductor chip 50 is physically fixed on the third semiconductor chip 40 through the medium of the adhesive member 70. The fourth bonding pads 42 of the fourth semiconductor chip 50 and the fourth bonding fingers 15 of the substrate 10 are electrically coupled by the bonding wires 68.

[0045] Referring to FIG. 4E, the sealing member 80 is formed on the entire first face 10a of the substrate 10 and on part of the second face 10b of the substrate 10 opposite the recess R through a molding process so that the first semiconductor chip 20, the third semiconductor chip 40, the fourth semiconductor chip 50, and the bonding wires 68 are covered and the second semiconductor chip 30 is also covered. During the molding process, the materials of the sealing member 80 are filled in the recess R disposed in the first semiconductor chip 20. Furthermore, the materials are filled in the spaces between the substrate 10 and the first semiconductor chip 20 and the third semiconductor chip 40 and the space between the second face 10b of the substrate 10 and the second semiconductor chip 30.

[0046] Referring to FIG. 4F, after a flux is dotted on the ball lands 16 arranged at the edges of the second face 10b of the substrate 10, the solder ball is attached on each of the ball land to which the flux has been dotted. Thereafter, a reflow process is performed on the attached solder balls, thereby forming the external connection electrodes 90 formed of the solder balls on the ball lands 16. As a result, the fabrication of the semiconductor package 100 according to an embodiment is completed.

[0047] Referring to FIG. 5, a semiconductor package 200 according to an embodiment may include a substrate 10, semiconductor chips 20, 30, 40, and 50, first and second bumps 62 and 64, first and second bonding wires 67 and 69, a sealing member 80, and external connection electrodes 90. The semiconductor package 200 according to an embodiment may further include first and second adhesive members 72 and 74.

[0048] The substrate 10 may include a first face 10a corresponding to the top and a second face 10b opposite the first face 10a and corresponding to the bottom. The substrate 10 may include a recess R in the first face 10a. The substrate 10 may include a plurality of first, third, and fourth bonding fingers 12, 14, and 15 arranged in the first face 10a and at the bottom of the recess R and second bonding fingers 13 arranged in the second face 10b of the substrate 10. The substrate 10 may include a plurality of ball lands 16 arranged in the second face 10b. In an embodiment, the third bonding fingers 14 may be placed outside a portion where the third semiconductor chip 40 is disposed in the first face 10a of the substrate 10.

[0049] Although not illustrated in FIG. 5, the substrate 10 may include circuit patterns respectively formed in the first face 10a and the second face 10b including the bottom of the recess R and via patterns formed within the circuit patterns. Furthermore, the substrate 10 may include a solder resist formed to expose the second to fourth bonding fingers 13, 14, and 15 and the ball lands 16 on the first face 10a and the second face 10b.

[0050] The first semiconductor chip 20 may include an active face 20a and a back side 20b opposite the active face 20a. The first semiconductor chip 20 may include a plurality of first bonding pads 22 arranged at edges on both sides of the active face 20a. The first semiconductor chip 20 may be dispose to flip-chip bonding to the bottom of the recess R through the medium of the first bump 62 formed on the first bonding pads 22.

[0051] The second semiconductor chip 30 may include an active face 30a and a back side 30b opposite the active face 30a. The second semiconductor chip 30 may include a plurality of second bonding pads 32 arranged at edges on both sides of the active face 30a. The second semiconductor chip 30 may be dispose to flip-chip bonding to the second face 10b of the substrate 10 through the medium of the second bumps 64 formed on the second bonding fingers 32.

[0052] The third semiconductor chip 40 may include an active face 40a and a back side 40b opposite the active face 40a. The third semiconductor chip 40 may include a plurality of third bonding pads 42 arranged at edges on both sides of the active face 40a. The third semiconductor chip 40 may be disposed so that the back side 40b faces the active face 20a of the first semiconductor chip 20 and the first face 10a of the substrate 10. The third semiconductor chip 40 may be disposed on the substrate 10 and the first semiconductor chip 20 through the medium of the first adhesive member 72 so that it crosses the first semiconductor chip 20.

[0053] The fourth semiconductor chip 50 may include an active face 50a and a back side 50b opposite the active face 50a. The fourth semiconductor chip 50 may include a plurality of fourth bonding pads 52 arranged at edges on both sides of the active face 40a. The fourth semiconductor chip 50 may be disposed on the third semiconductor chip 40 through the medium of the second adhesive member 74 so that the back side 50b faces the active face 40a of the third semiconductor chip 40. The fourth semiconductor chip 50 may generally have the same size and shape as the third semiconductor chip 40. The fourth semiconductor chip 50 may be disposed so that it is perpendicular or substantially perpendicular to the first semiconductor chip 20.

[0054] The first bumps 62 may electrically couple the first bonding fingers 12 of the substrate 10 and the first bonding pads 22 of the first semiconductor chip 20. The second bumps 64 may electrically couple the second bonding fingers 13 of the substrate 10 and the second bonding pads 32 of the second semiconductor chip 30. The first bonding wires 67 may electrically couple the third bonding fingers 14 of the substrate 10 and the third bonding pads 42 of the third semiconductor chip 40. The second bonding wires 69 may electrically couple the fourth bonding fingers 15 of the substrate 10 and the fourth bonding pads 52 of the fourth semiconductor chip 50.

[0055] The first and the second adhesive members 72 and 74 may include an adhesive tape or an adhesive paste. In particular, the second adhesive member 74 may have a sufficient thickness in which the wire loop of the first bonding wires 67 electrically coupling the third bonding fingers 14 of the substrate 10 and the third bonding pads 42 of the third semiconductor chip 40 is taken into consideration. For example, the second adhesive member 74 may be a penetrate wafer backside lamination (PWBL) film.

[0056] Although not illustrated in FIG. 5, the semiconductor package 200 according to an embodiment may include a spacer interposed between the third semiconductor chip 40 and the fourth semiconductor chip 50 in order to secure the wire loop of the first bonding wires 67.

[0057] The sealing member 80 may include an epoxy molding compound. The sealing member 80 may be formed on the first face 10a of the substrate 10 so that it covers the first, the third, and the fourth semiconductor chips 20, 40, and 50 and the first and the second bonding wires 67 and 69. Furthermore, the sealing member 80 may be formed on part of the second face 10b of the substrate 10 so that it covers or substantially covers the second semiconductor chip 30. Furthermore, the sealing member 80 may be formed to fill the recess R in which the first semiconductor chip 20 has been disposed.

[0058] The external connection electrodes 90 may include solder balls and may be formed on the ball lands 16 arranged in the second face 10b of the substrate 10.

[0059] The aforementioned semiconductor packages may be applied to a variety of types of semiconductor devices and package modules including the same.

[0060] FIG. 6 is a block diagram of an electronic system to which a semiconductor package according to various embodiments has been applied.

[0061] As illustrated in FIG. 6, the electronic system 1000 may include a controller 1100, an input/output device 1200, and a memory device 1300. The controller 1100, the input/output device 1200, and the memory device 1300 may be coupled through a bus 1500 providing a passage through which data moves.

[0062] For example, the controller 1100 may include at least one of at least one microprocessor, at least one digital signal processor, at least one microcontroller, and logic elements capable of performing a function similar to that of the microprocessor, digital signal processor, and microcontroller. The controller 1100 and the memory device 1300 may include the semiconductor package according to the various embodiments. The input/output device 1200 may include at least one of a keypad, a keyboard, and a display device.

[0063] The memory device 1300 may store data and/or instructions executed by the controller 1100. The memory device 1300 may include a volatile memory device, such as DRAM, and/or a nonvolatile memory device, such as flash memory. For example, flash memory may be mounted on a mobile device or an information processing system, such as a desktop computer. Such flash memory may include a semiconductor disk device (e.g., SSD). In this case, the electronic system 1000 may stably store a large amount of data in a flash memory system.

[0064] The electronic system 1000 may further include an interface 1400 for sending data to a communication network or receiving data from a communication network. The interface 1400 may have a wired/wireless form. For example, the interface 1400 may include an antenna or a wired/wireless transceiver.

[0065] Although not illustrated in FIG. 6, the electronic system 1000 may further include an application chip set, a camera image processor, and an input/output device.

[0066] The electronic system 1000 may be implemented as a mobile system, a personal computer, an industry computer, or a logic system performing various functions. For example, the mobile system may be any one of a person digital assistant (PDA), a portable computer, a web tablet, a mobile phone, a smart phone, a wireless phone, a laptop computer, a memory card, a digital music system digital, and an information transmission/reception system.

[0067] If the electronic system 1000 is equipment capable of performing wireless communication, the electronic system 1000 may be used in communication systems, such as code division multiple access (CDMA), global system for mobile communication (GSM), north American digital cellular (NADC), enhanced-time division multiple access (E-TDMA), wideband code division multiple access (WCDMA), CDMA2000, long term evolution (LTE), and Wibro wireless broadband Internet.

[0068] FIG. 7 is a block diagram of a memory card including the semiconductor package according to the various embodiments. As illustrated in FIG. 7, the semiconductor package according to various embodiments may be provided in the form of the memory card 2000. For example, the memory card 2000 may include memory 2100, such as a nonvolatile memory device, and a memory controller 2200. The memory 2100 and the memory controller 2200 may store data or read stored data.

[0069] The memory 2100 may include at least one of nonvolatile memory devices to which the semiconductor package according to various embodiments has been applied. The memory controller 2200 may control the memory 2100 so that it reads stored data or stores data in response to a read/write request from the host 2300.

[0070] While various embodiments have been described above, it will be understood to those skilled in the art that the embodiments described are by way of example only. Accordingly, the semiconductor package described herein should not be limited based on the described embodiments.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.