Phase-change Random Access Memory Device And Method Of Manufacturing The Same

YOO; Myoung Sul ; et al.

U.S. patent application number 13/326490 was filed with the patent office on 2012-12-27 for phase-change random access memory device and method of manufacturing the same. Invention is credited to Ky Hyun Han, Jae Min Oh, Myoung Sul YOO.

| Application Number | 20120326114 13/326490 |

| Document ID | / |

| Family ID | 47360981 |

| Filed Date | 2012-12-27 |

| United States Patent Application | 20120326114 |

| Kind Code | A1 |

| YOO; Myoung Sul ; et al. | December 27, 2012 |

PHASE-CHANGE RANDOM ACCESS MEMORY DEVICE AND METHOD OF MANUFACTURING THE SAME

Abstract

A phase-change random access memory device includes a semiconductor substrate, an interlayer dielectric layer formed over the semiconductor substrate and having contact holes defined therein, metal contacts formed in the contact holes, an ohmic contact layer formed over the metal contacts and having recesses defined therein, and switching elements formed over the recesses of the ohmic contact layer.

| Inventors: | YOO; Myoung Sul; (Ichon-si, KR) ; Oh; Jae Min; (Ichon-si, KR) ; Han; Ky Hyun; (Ichon-si, KR) |

| Family ID: | 47360981 |

| Appl. No.: | 13/326490 |

| Filed: | December 15, 2011 |

| Current U.S. Class: | 257/5 ; 257/E21.09; 257/E45.002; 438/382 |

| Current CPC Class: | H01L 27/2409 20130101 |

| Class at Publication: | 257/5 ; 438/382; 257/E45.002; 257/E21.09 |

| International Class: | H01L 45/00 20060101 H01L045/00; H01L 21/20 20060101 H01L021/20 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Jun 21, 2011 | KR | 10-2011-0060112 |

Claims

1. A phase-change random access memory device comprising: a semiconductor substrate; an interlayer dielectric layer formed over the semiconductor substrate and having contact holes defined therein; metal contacts formed in the contact holes; an ohmic contact layer formed over the metal contacts and having recesses defined therein; and switching elements formed over the recesses of the ohmic contact layer.

2. The phase-change random access memory device according to claim 1, wherein the switching elements include at least three switching elements and are separated from one another by an equal distance.

3. The phase-change random access memory device according to claim 1, wherein the switching elements are formed of polysilicon.

4. The phase-change random access memory device according to claim 1, wherein the ohmic contact layer is formed to have a cross section of a substantially U-shape.

5. The phase-change random access memory device according to claim 4, wherein the metal contacts are formed to have a surface with a height lower than a top surface of the interlayer dielectric layer.

6. The phase-change random access memory device according to claim 1, wherein the ohmic contact layer partially fills the contact holes, extends outside the contact holes, and covers a periphery of the interlayer dielectric layer outside the contact holes.

7. A method for manufacturing a phase-change random access memory device, comprising: providing a semiconductor substrate; forming a first interlayer dielectric layer over the semiconductor substrate, wherein the first interlayer dielectric layer has contact holes formed therein; forming metal contacts by filling a metallic substance in the contact holes; forming a second interlayer dielectric layer over the metal contacts and the first interlayer dielectric layer, wherein the second interlayer dielectric layer have holes formed therein; forming an ohmic contact layer with recesses by filling and etching titanium nitride (TiN) in the holes; and forming switching elements over the recesses of the ohmic contact layer.

8. The method according to claim 7, wherein, in the forming of the ohmic contact layer, the recesses are defined through a photolithographic process or an etch-back process.

9. A phase-change random access memory device comprising: a semiconductor substrate; a first interlayer dielectric layer formed over the semiconductor substrate and having contact holes defined therein; metal contacts formed in the contact holes; a second interlayer dielectric layer formed over the first interlayer dielectric layer and the metal contacts and having holes; an ohmic contact layer partially filling the holes; and switching elements formed over the ohmic contact layer and filling the holes.

10. The phase-change random access memory device according to claim 9, wherein the second interlayer dielectric layer is formed by being deposited to a height reaching a position corresponding to one third of the switching elements in height.

11. The phase-change random access memory device according to claim 9, wherein the switching elements include at least three switching elements and are separated from one another by an equal distance.

12. A method for manufacturing a phase-change random access memory device, comprising: providing a semiconductor substrate; forming a first interlayer dielectric layer over the semiconductor substrate to have contact holes; forming metal contacts in the contact holes; forming a second interlayer dielectric layer over the metal contacts and the first interlayer dielectric layer to have holes; partially filling the holes with an ohmic contact layer; and forming switching elements over the ohmic contact layer to fill the holes.

13. The method according to claim 12, wherein, in the forming of the second interlayer dielectric layer, the second interlayer dielectric layer is formed by being deposited to a height reaching a position corresponding to one third of the switching elements in height.

14. The method according to claim 12, wherein, in the forming of the ohmic contact layer, the ohmic contact layer is defined through a photolithographic process or an etch-back process.

15. A method for manufacturing a phase-change random access memory device, comprising: providing a semiconductor substrate; forming an interlayer dielectric layer over the semiconductor substrate to have contact holes; forming metal contacts by filling a metallic substance in the contact holes; partially etching the metal contacts; forming an ohmic contact layer over the etched metal contacts and over a peripheral of the interlayer dielectric layer outside the contact holes, wherein the ohmic contact layer has a cross section of a substantially U-shape; and forming switching elements over the ohmic contact layer.

16. The method according to claim 15, wherein, in the etching of the metal contacts, the metal contacts are etched to have surface with a height lower than a top surface of the interlayer dielectric layer.

17. The method according to claim 16, wherein, in the partial etching of the metal contacts, the metal contacts are etched through an etch-back process.

Description

CROSS-REFERENCES TO RELATED APPLICATION

[0001] The present application claims priority under 35 U.S.C. .sctn.119(a) to Korean application number 10-2011-0060112, filed on Jun. 21, 2011, in the Korean Intellectual Property Office, which is incorporated herein by reference in its entirety as set forth in full.

BACKGROUND

[0002] 1. Technical Field

[0003] The present invention relates to a memory device, and more particularly, to a phase-change random access memory device and a method for manufacturing the same.

[0004] 2. Related Art

[0005] In general, a phase-change random access memory (PRAM) device stores data using a difference in resistance between an amorphous state and a crystalline state due to a phase change of a chalcogenide compound.

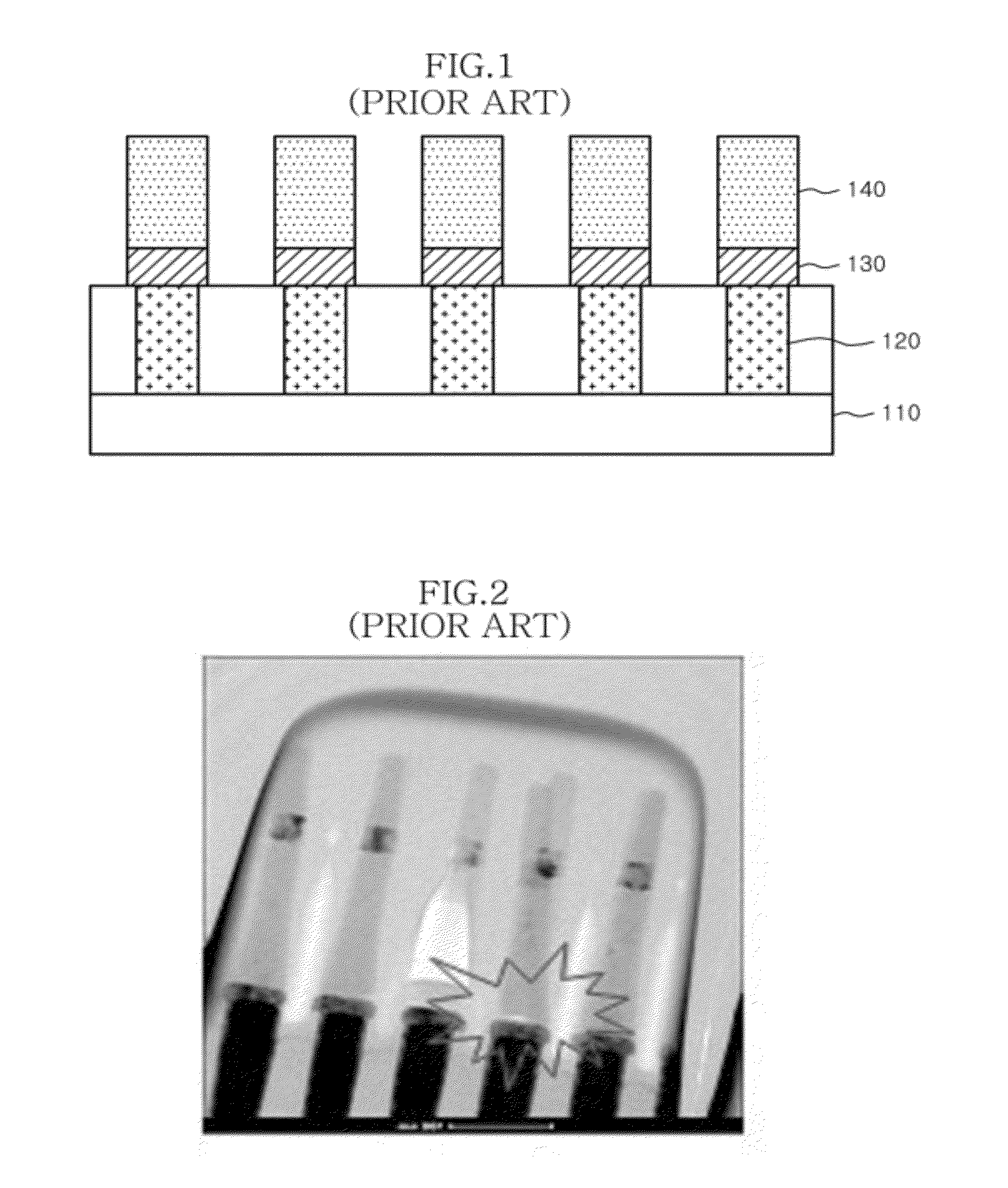

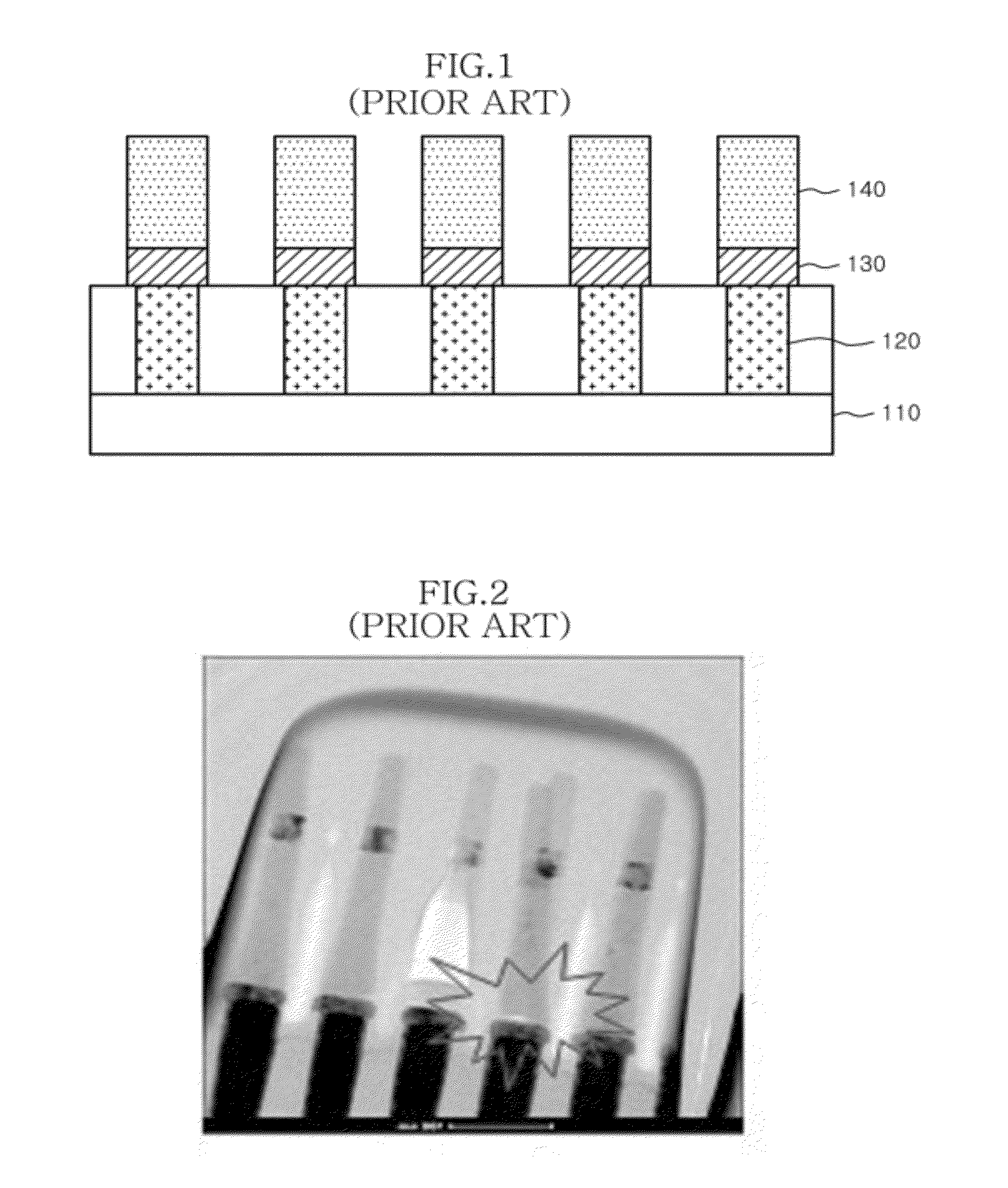

[0006] FIG. 1 is a cross-sectional view illustrating a conventional phase-change random access memory device, and FIG. 2 is a photograph showing inclining of diode patterns in the conventional phase-change random access memory device.

[0007] Referring to FIG. 1, in the conventional phase-change random access memory device, metal contacts 120 are formed on a semiconductor substrate 110 using a metallic substance, and diodes 140 are formed on the metal contacts 120.

[0008] In this regard, when the diodes 140 of the conventional phase-change random access memory device may be formed of polysilicon, the adhesion force between the metal contacts 120 formed of the metallic substance and the diodes 140 formed of polysilicon becomes poor. In order to address such a feature, an ohmic contact layer 130 is formed using titanium nitride (TiN).

[0009] However, in the conventional phase-change random access memory device, titanium nitride (TiN) constituting the ohmic contact layer 130 is likely to be degraded in a subsequent annealing process, causing a problem in the interface between the titanium nitride (TiN) and polysilicon. Consequently, as shown in FIG. 2, when etching the patterns of the diodes 140 or performing a cleaning process, a phenomenon occurs in which the diode patterns incline/slant.

SUMMARY

[0010] A phase-change random access memory device and a method for manufacturing the same, which can prevent diode patterns from inclining, thereby improving the reliability of a phase-change random access memory device, are described herein.

[0011] In one embodiment of the present invention, a phase-change random access memory device includes: a semiconductor substrate; an interlayer dielectric layer formed over the semiconductor substrate and having contact holes defined therein; metal contacts in the contact holes; an ohmic contact layer formed over the metal contacts and having recesses defined therein; and switching elements formed over the recesses of the ohmic contact layer.

[0012] In one embodiment of the present invention, a method for manufacturing a phase-change random access memory device includes: providing a semiconductor substrate; forming a first interlayer dielectric layer over the semiconductor substrate, wherein the first interlayer dielectric layer has contact holes formed therein; forming metal contacts by filling a metallic substance in the contact holes; forming a second interlayer dielectric layer over the metal contacts and the first interlayer dielectric layer, wherein the second interlayer dielectric layer have holes formed therein; forming an ohmic contact layer with recesses by filling and etching titanium is nitride (TiN) in the holes; and forming switching elements over the recesses of the ohmic contact layer.

[0013] In another embodiment of the present invention, a phase-change random access memory device includes: a semiconductor substrate; a first interlayer dielectric layer formed over the semiconductor substrate and having contact holes defined therein; metal contacts formed in the contact holes; a second interlayer dielectric layer formed over the first interlayer dielectric layer and the metal contacts and having holes; an ohmic contact layer partially filling the holes; and switching elements formed over the ohmic contact layer and filling the holes.

[0014] In another embodiment of the present invention, a method for manufacturing a phase-change random access memory device includes: providing a semiconductor substrate; forming a first interlayer dielectric layer over the semiconductor substrate to have contact holes; forming metal contacts in the contact holes; forming a second interlayer dielectric layer over the metal contacts and the first interlayer dielectric layer to have holes; partially filling the holes with an ohmic contact layer; and forming switching elements over the ohmic contact layer to fill the holes.

[0015] In another embodiment of the present invention, a method for manufacturing a phase-change random access memory device includes: providing a semiconductor substrate; forming an interlayer dielectric layer over the semiconductor substrate to have contact holes; forming metal contacts by filling a metallic substance in the contact holes; partially etching the metal contacts; forming an ohmic contact layer over the etched metal contacts and over a peripheral of the interlayer dielectric layer outside the contact holes, wherein the ohmic contact layer has a cross section of a substantially U-shape; and forming switching elements over the ohmic contact layer.

BRIEF DESCRIPTION OF THE DRAWINGS

[0016] Features, aspects, and embodiments are described in conjunction with the attached drawings, in which:

[0017] FIG. 1 is a cross-sectional view illustrating a conventional phase-change random access memory device;

[0018] FIG. 2 is a photograph showing inclining of diode patterns in the conventional phase-change random access memory device;

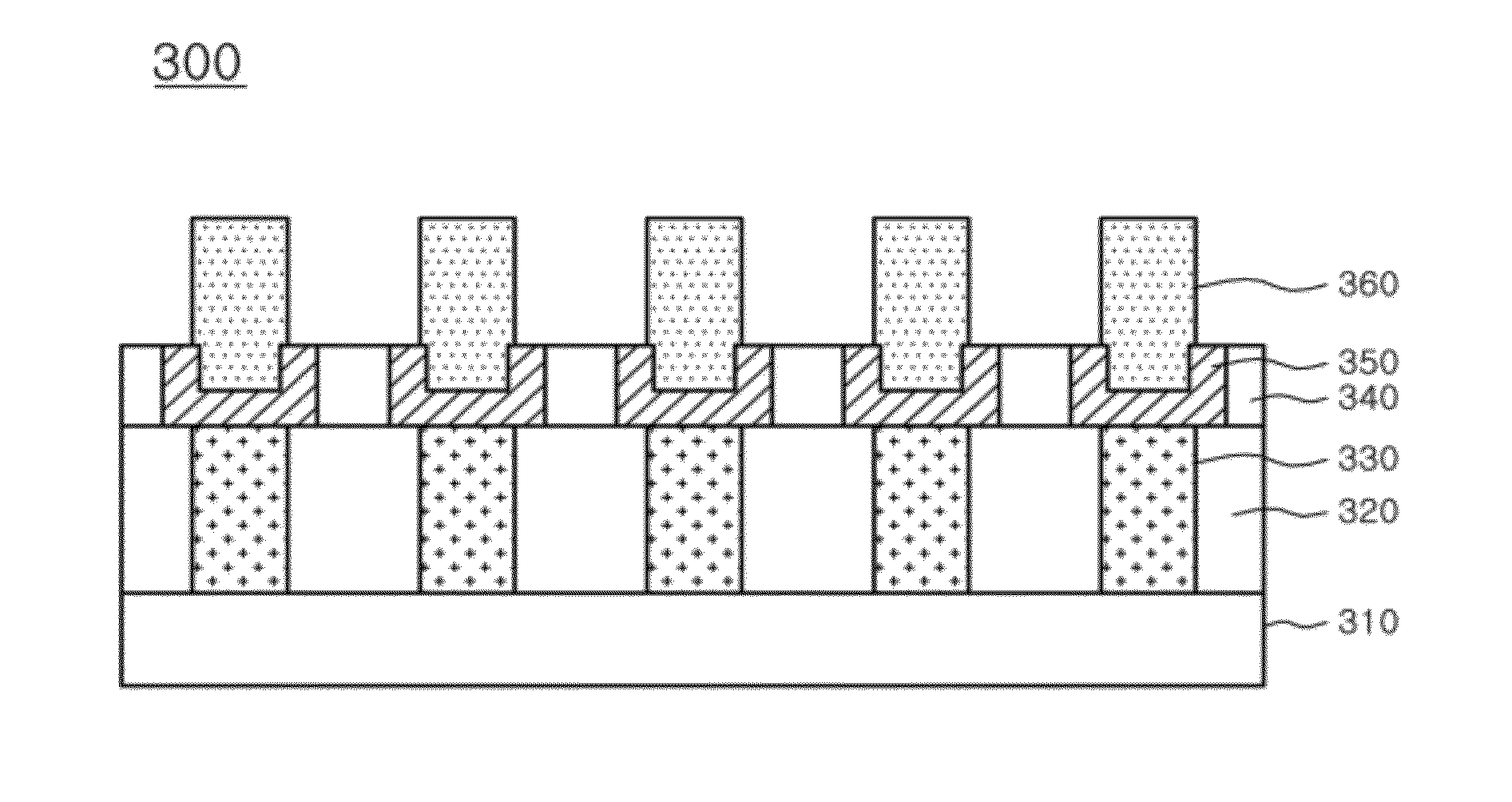

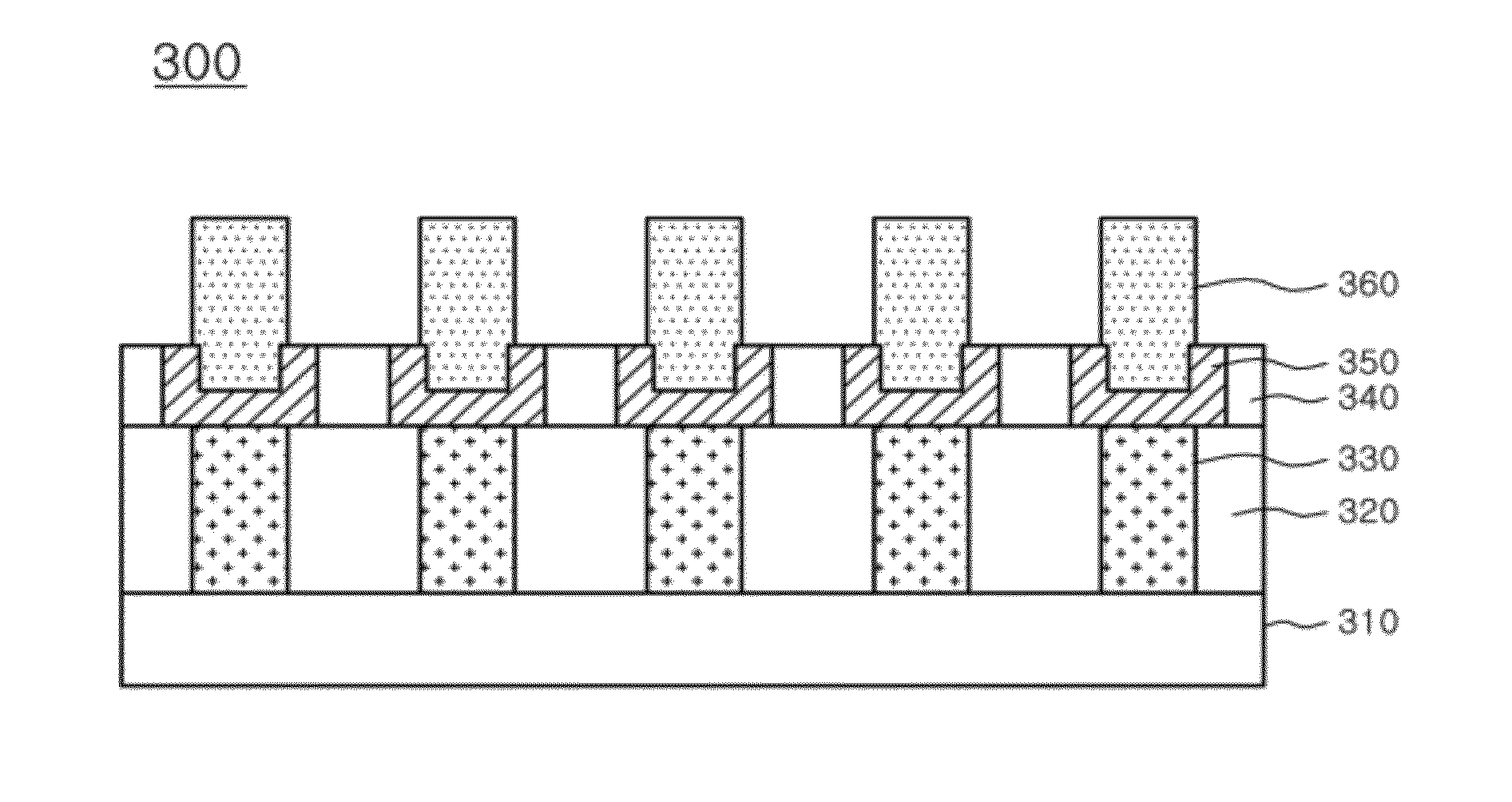

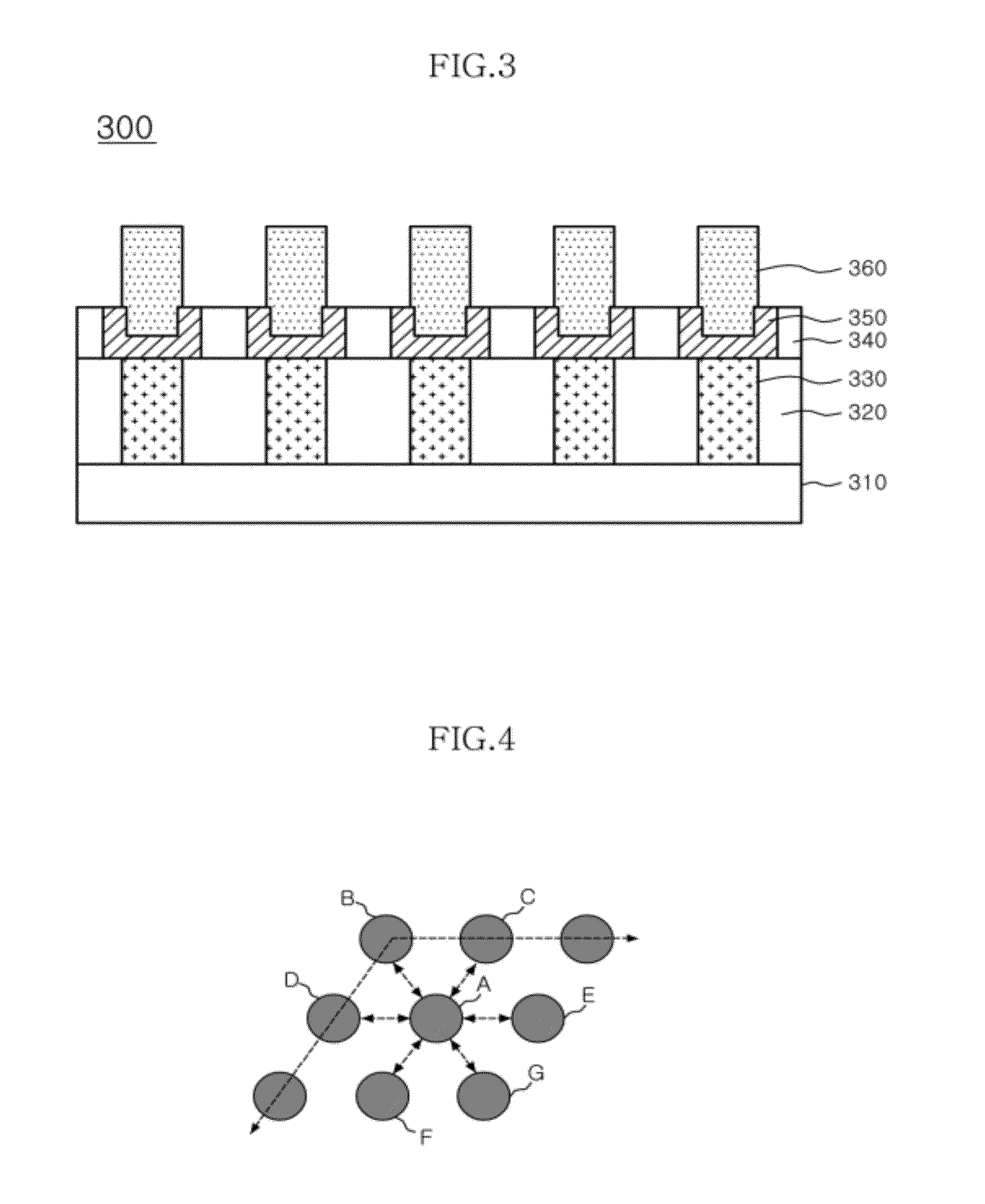

[0019] FIG. 3 is a cross-sectional view illustrating a phase-change random access memory device in accordance with a first embodiment of the present invention;

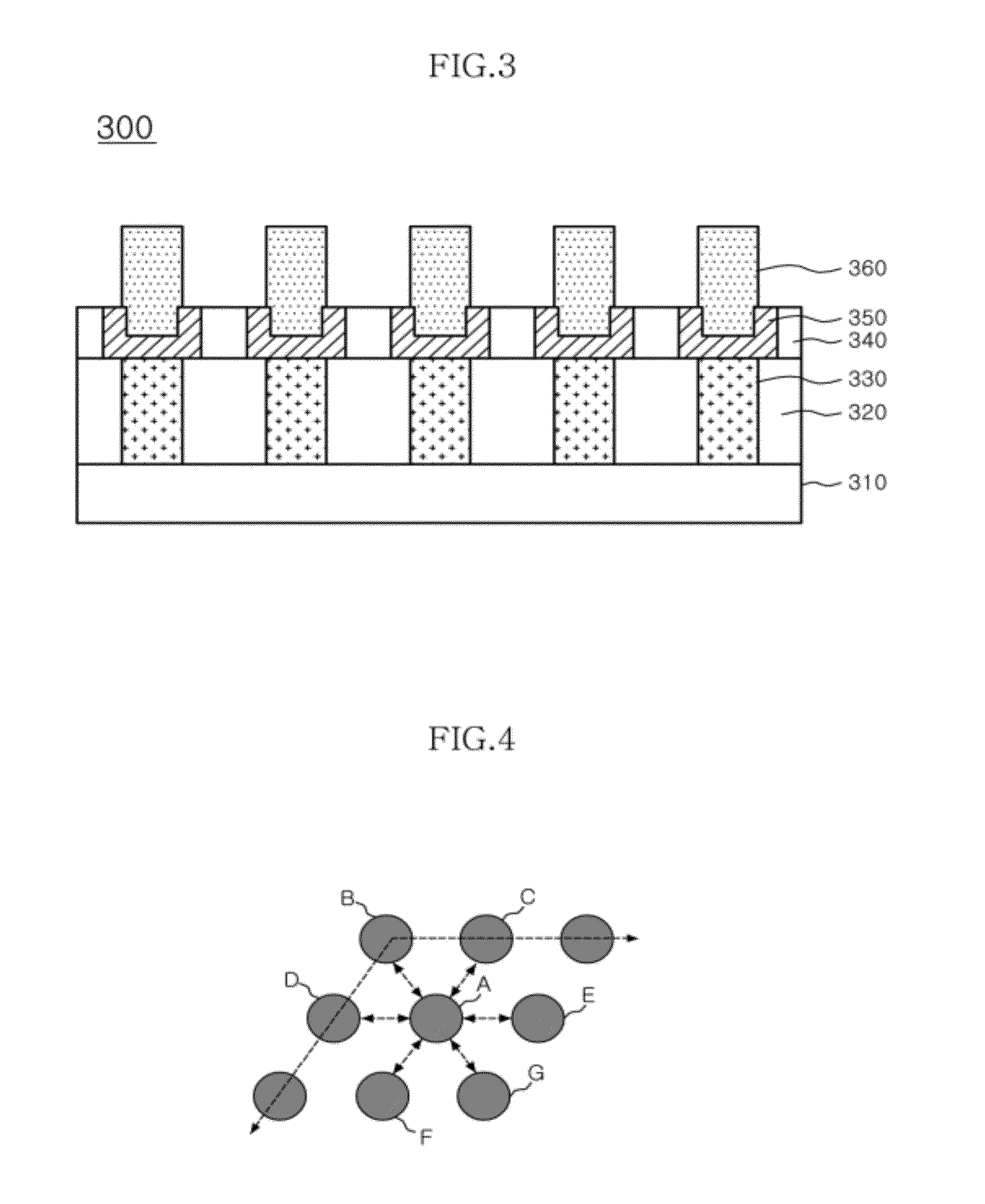

[0020] FIG. 4 is a plan view showing the arrangement of diodes in the phase-change random access memory device in accordance with the first embodiment of the present invention;

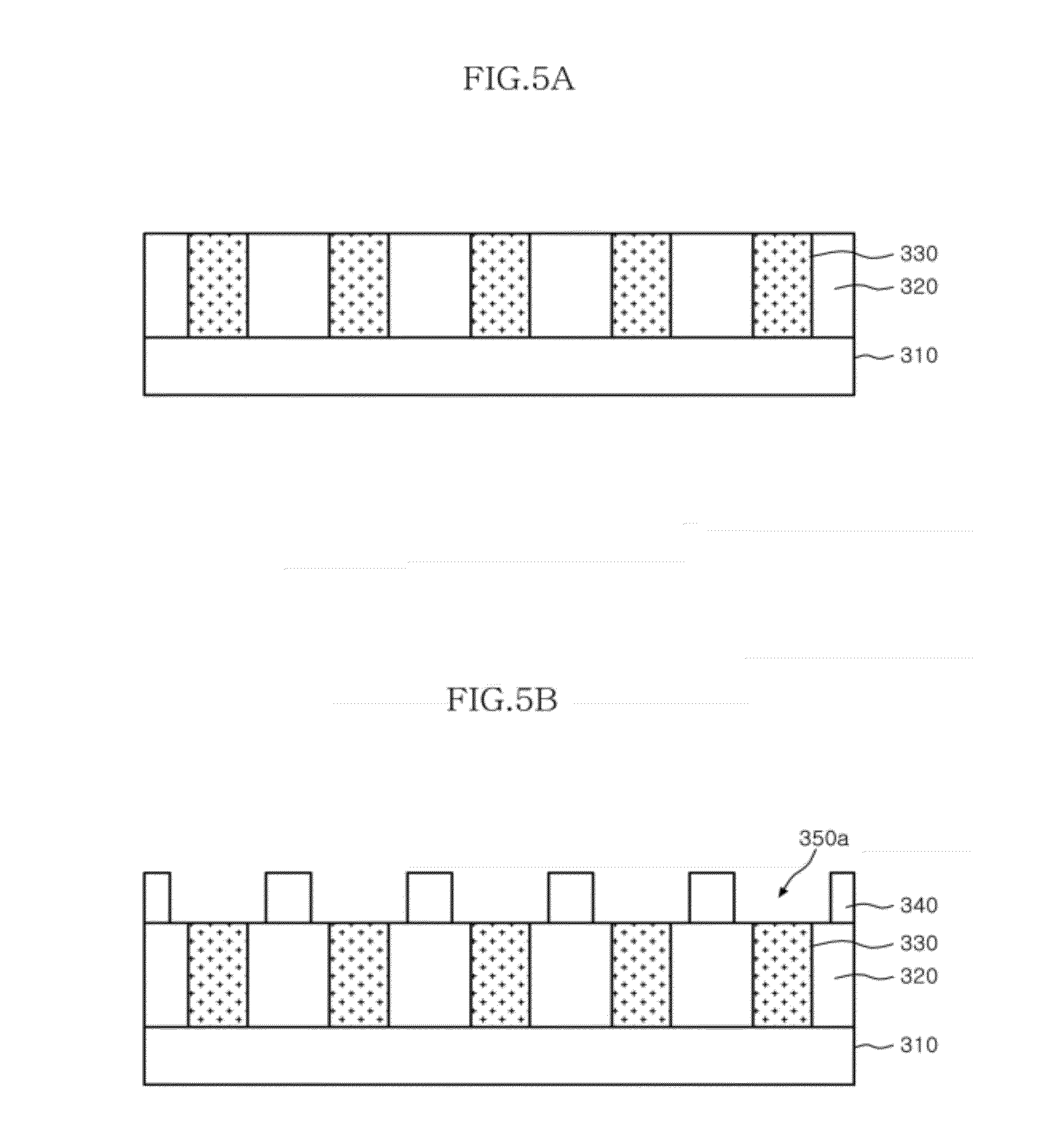

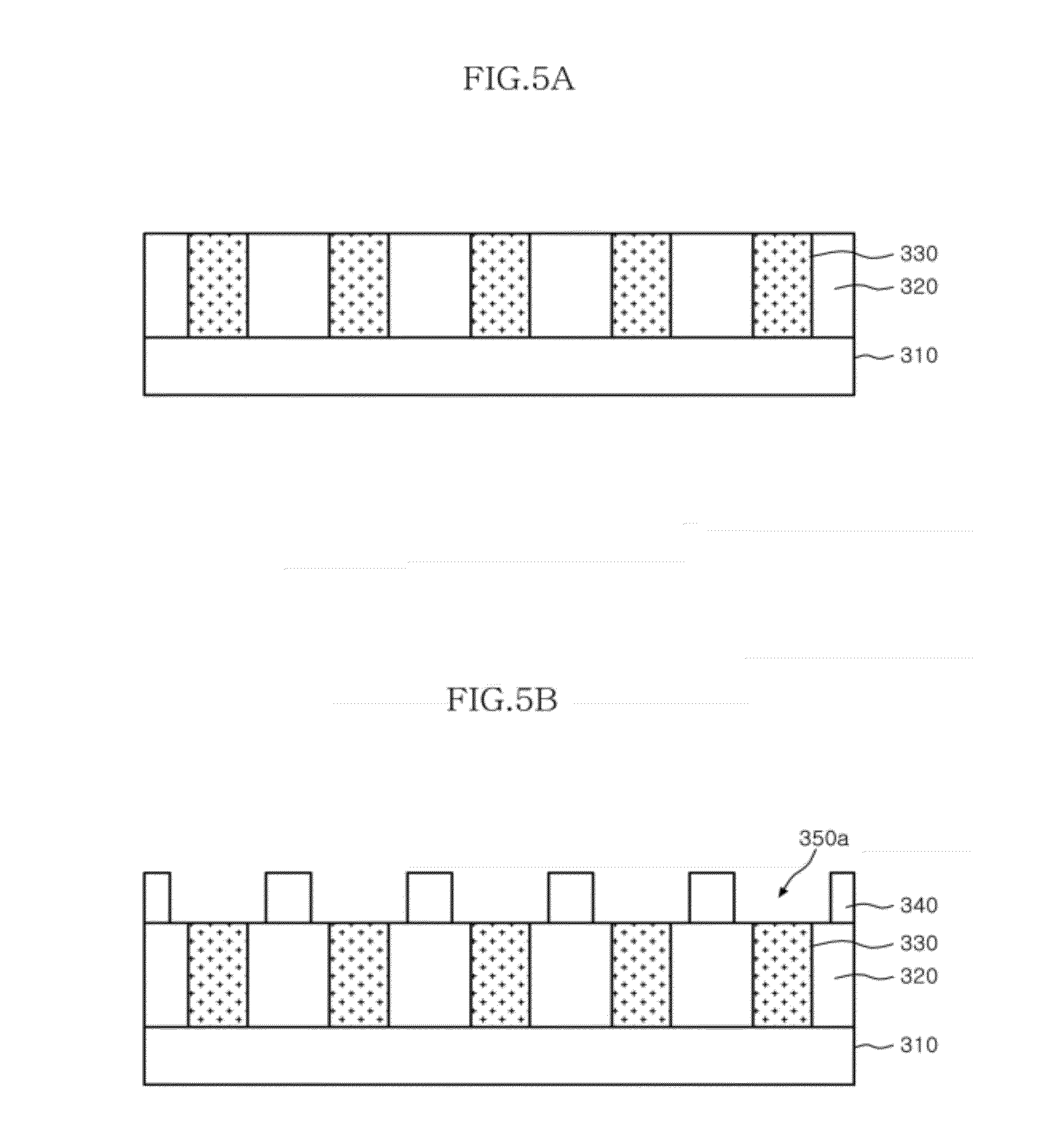

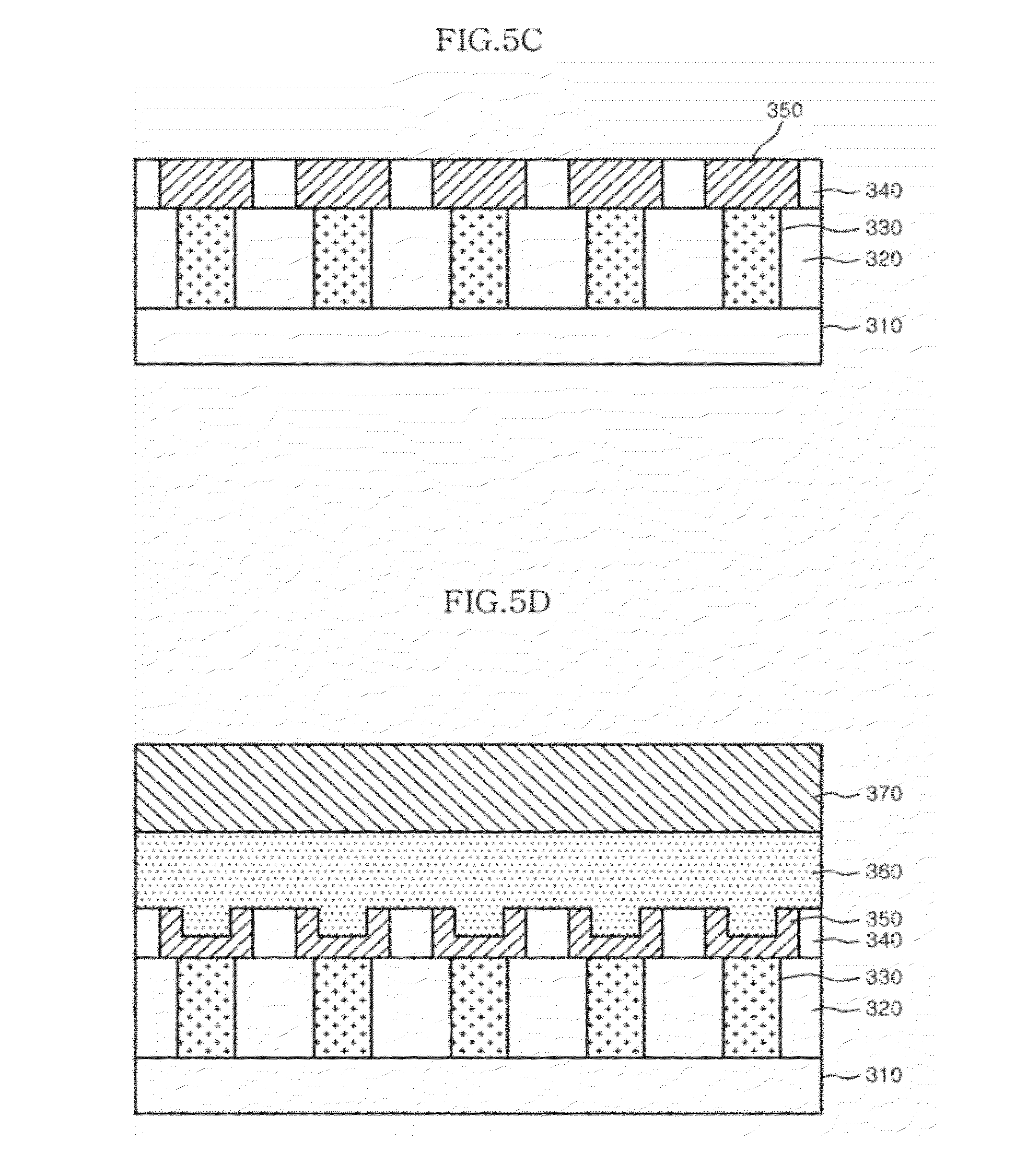

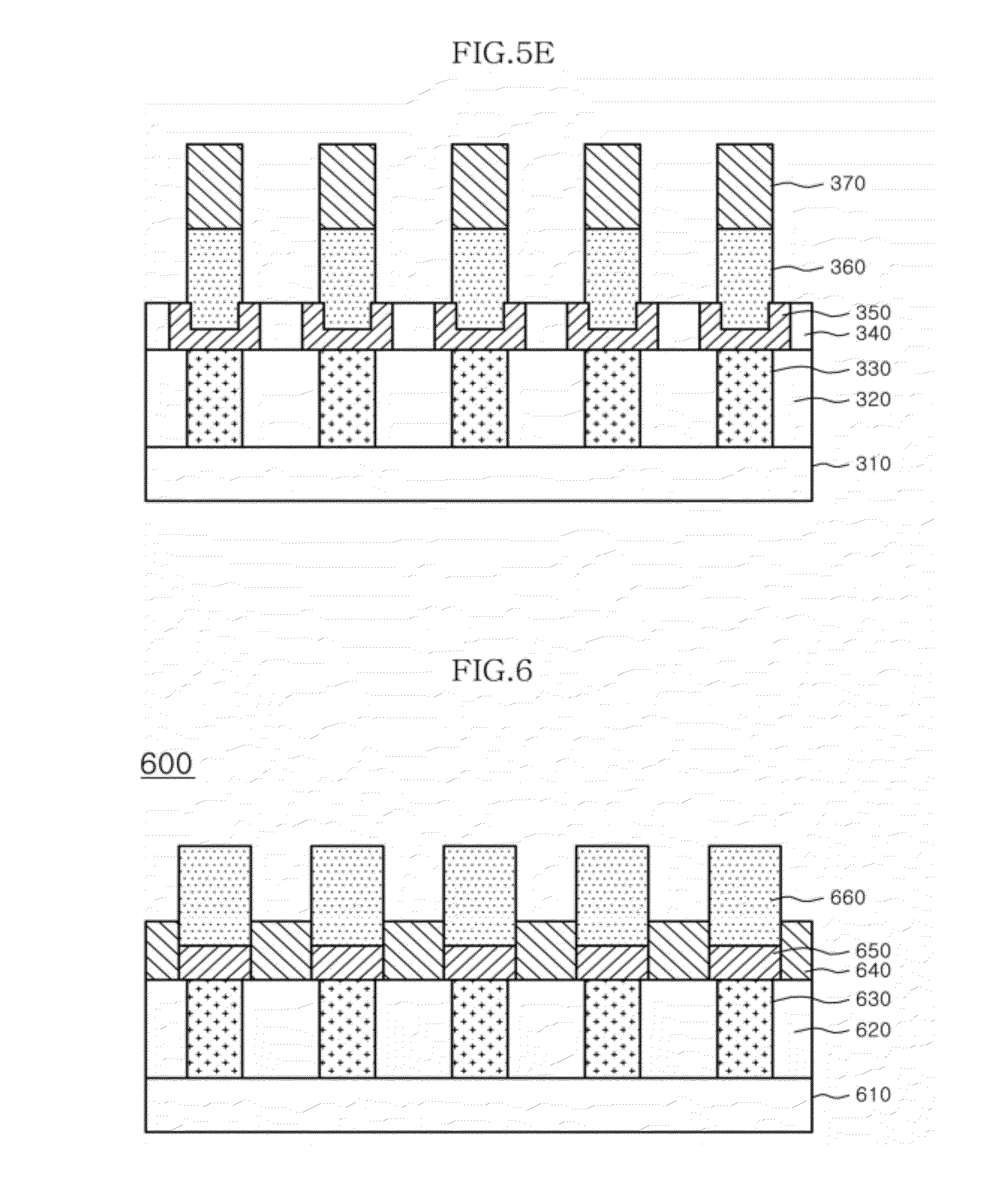

[0021] FIGS. 5A to 5E are cross-sectional views sequentially showing the processes of a method for forming diodes of the phase-change random access memory device in accordance with the first embodiment of the present invention;

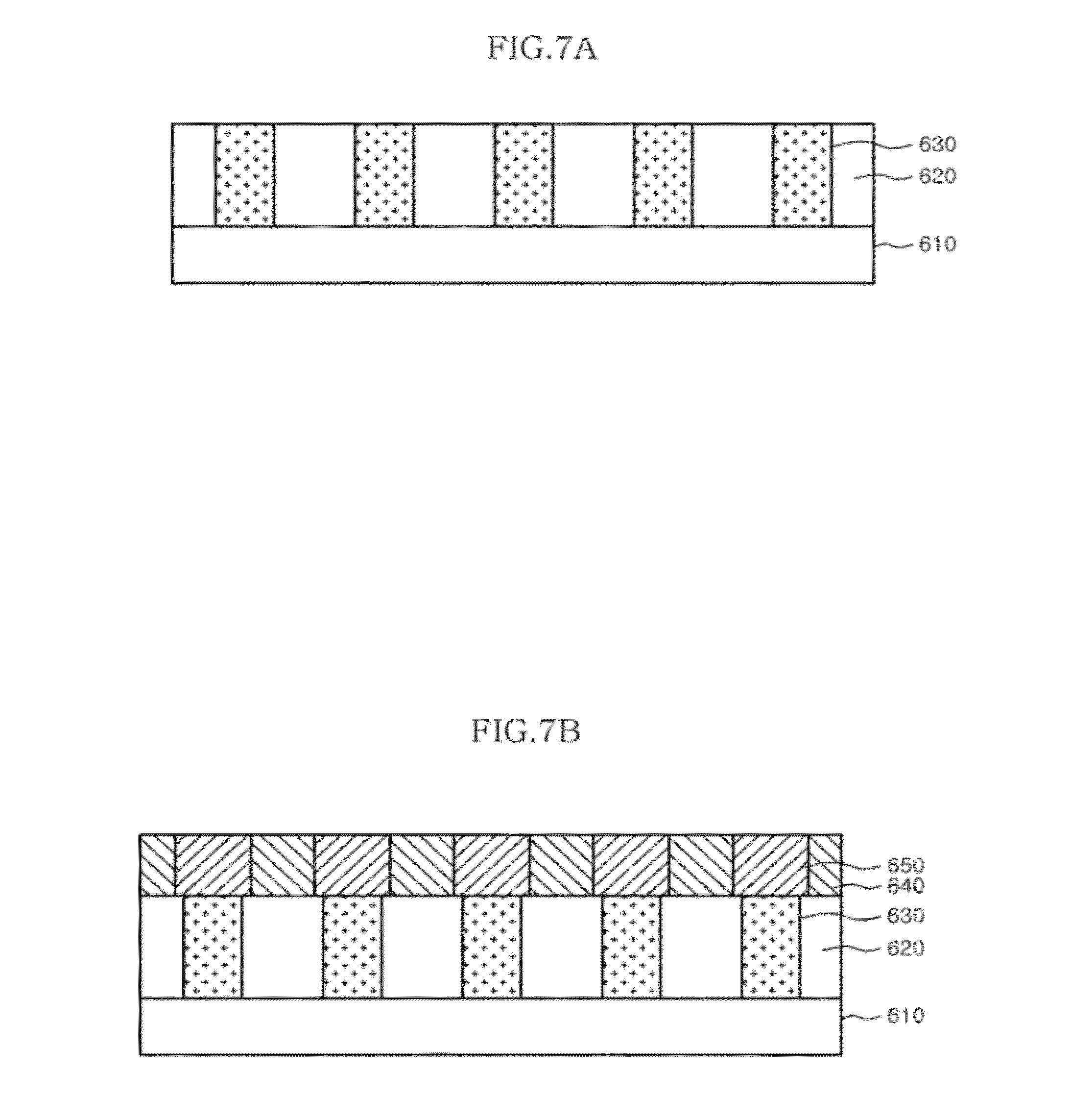

[0022] FIG. 6 is a cross-sectional view illustrating a phase-change random access memory device in accordance with a second embodiment of the present invention;

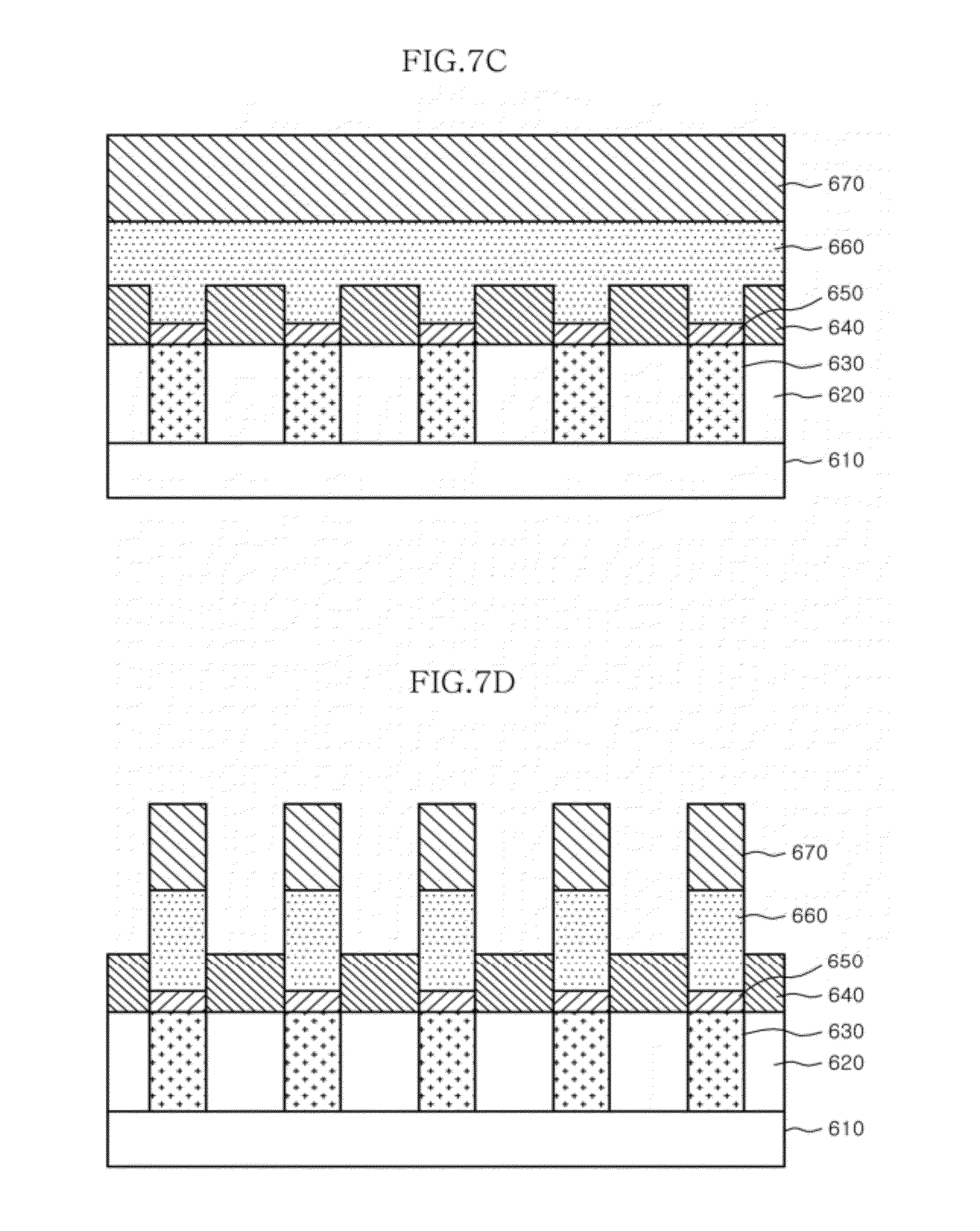

[0023] FIGS. 7A to 7D are cross-sectional views sequentially showing the processes of a method for forming diodes of the phase-change random access memory device in accordance with the second embodiment of the present invention;

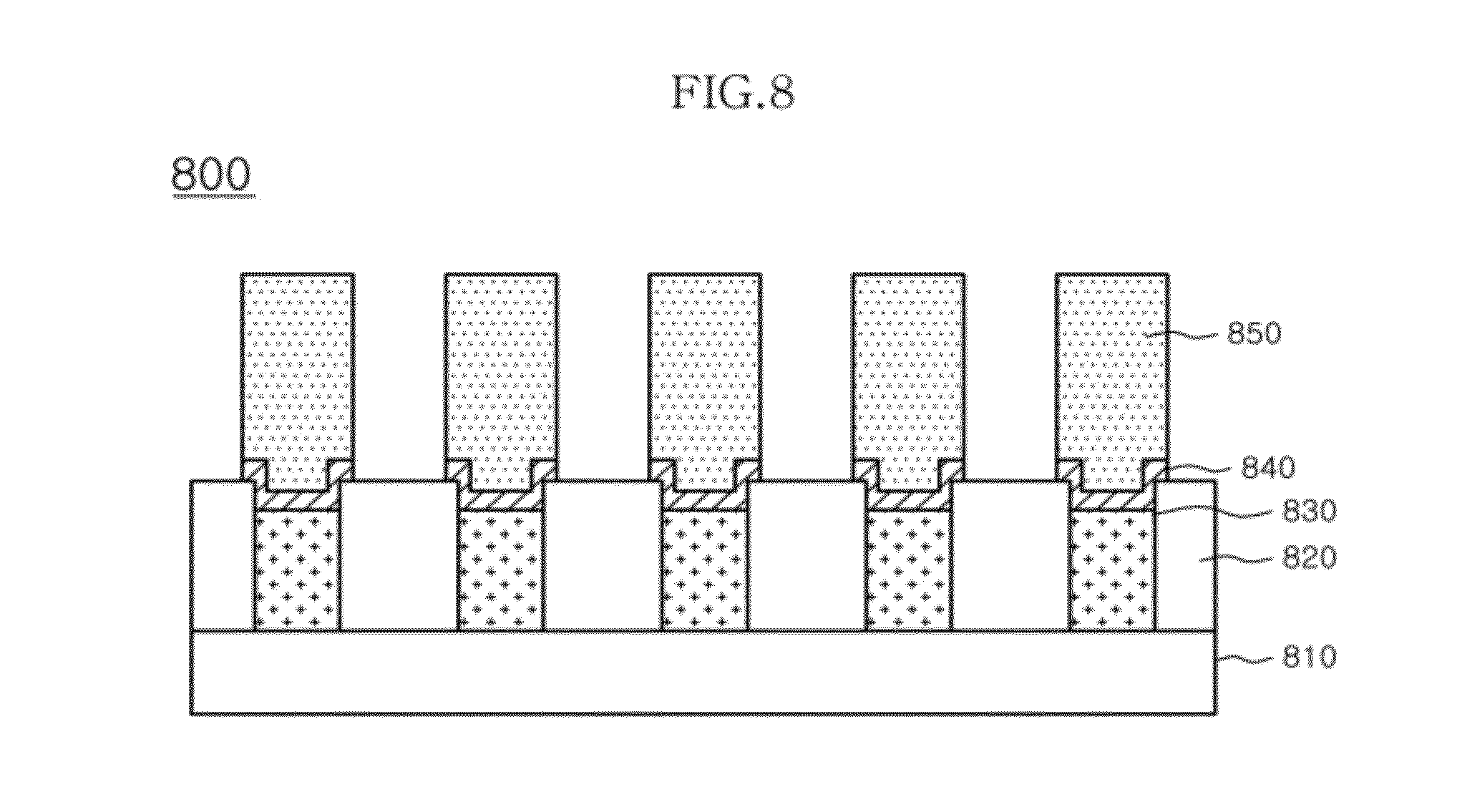

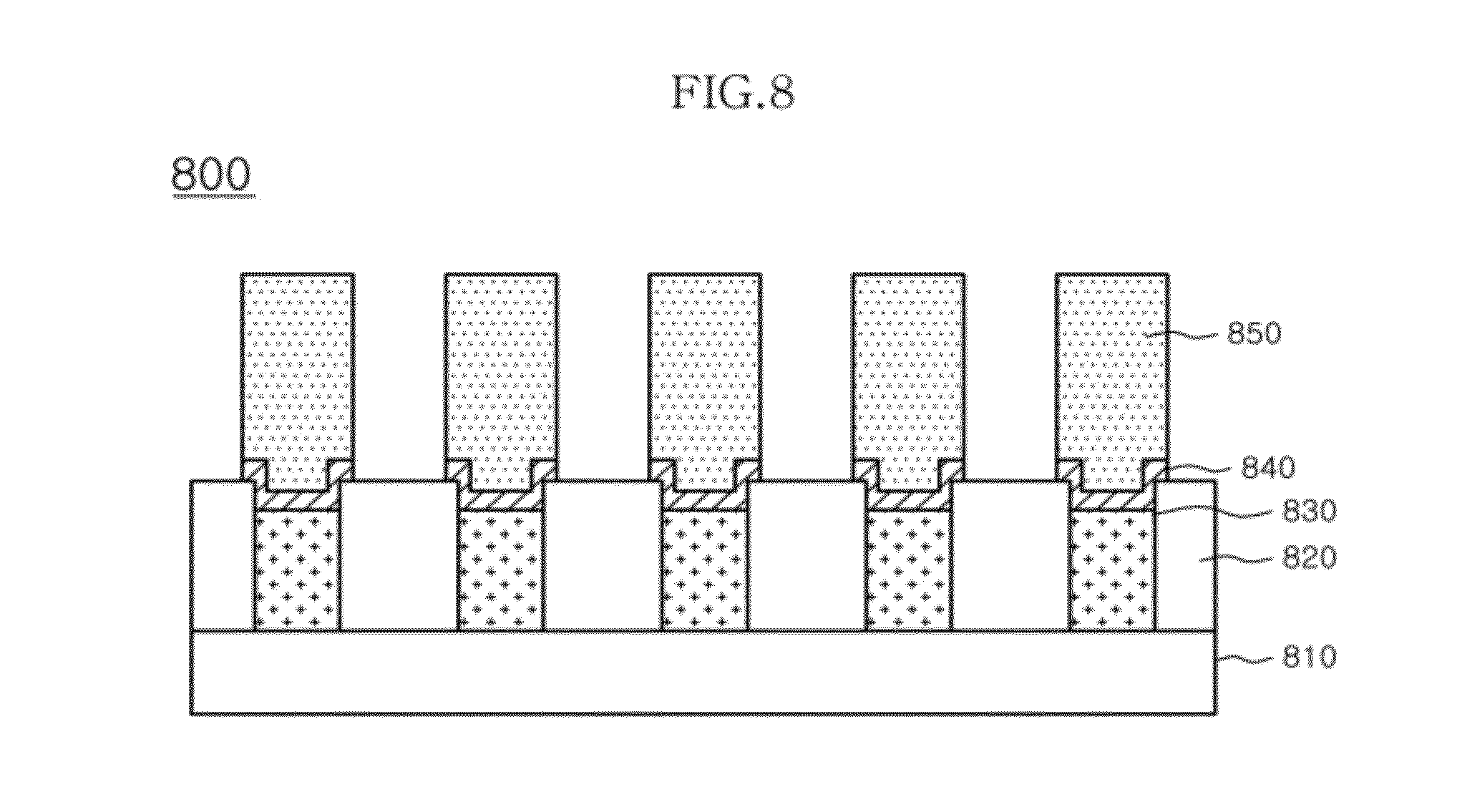

[0024] FIG. 8 is a cross-sectional view illustrating a phase-change random access memory device in accordance with a third embodiment of the present invention; and

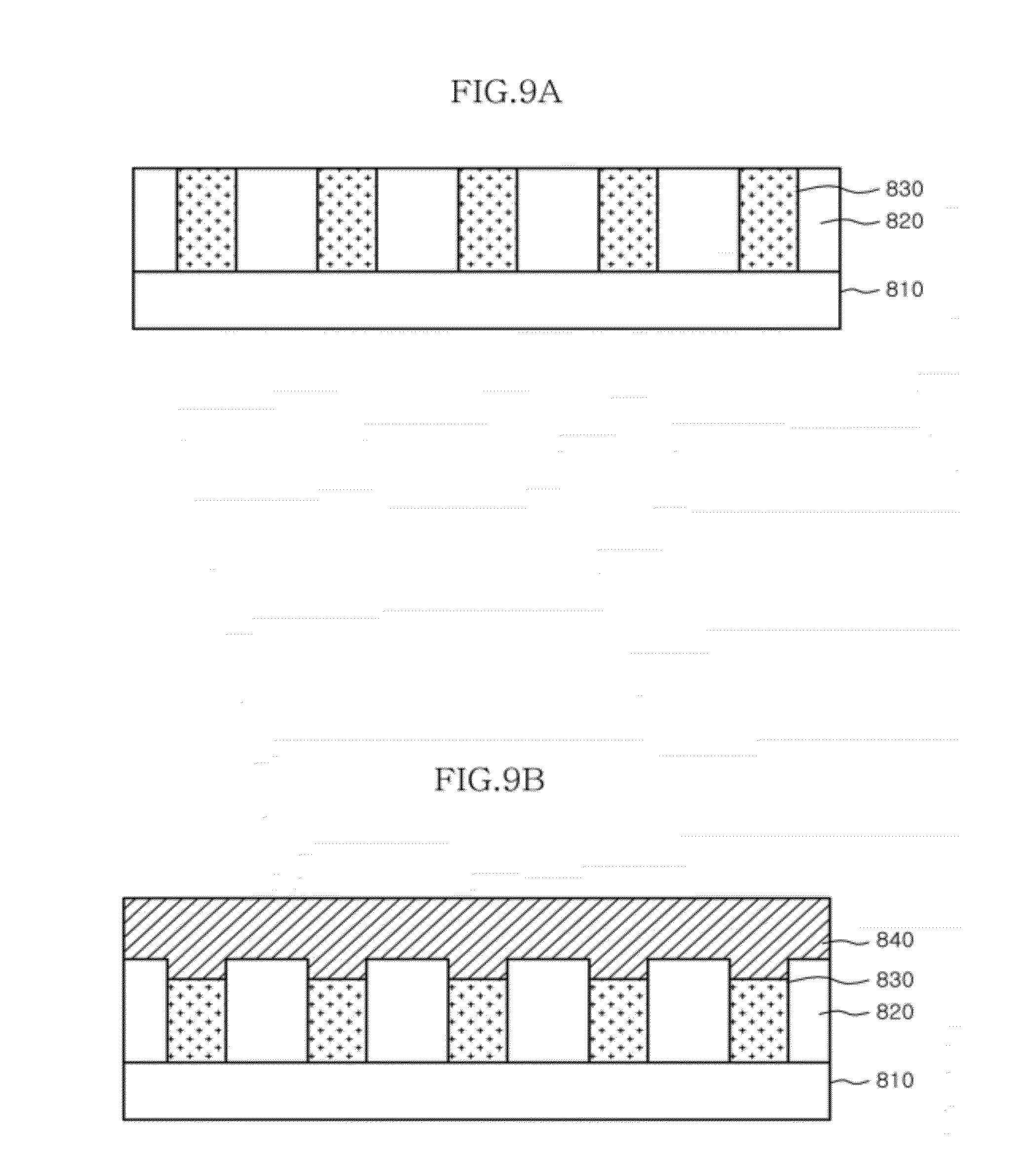

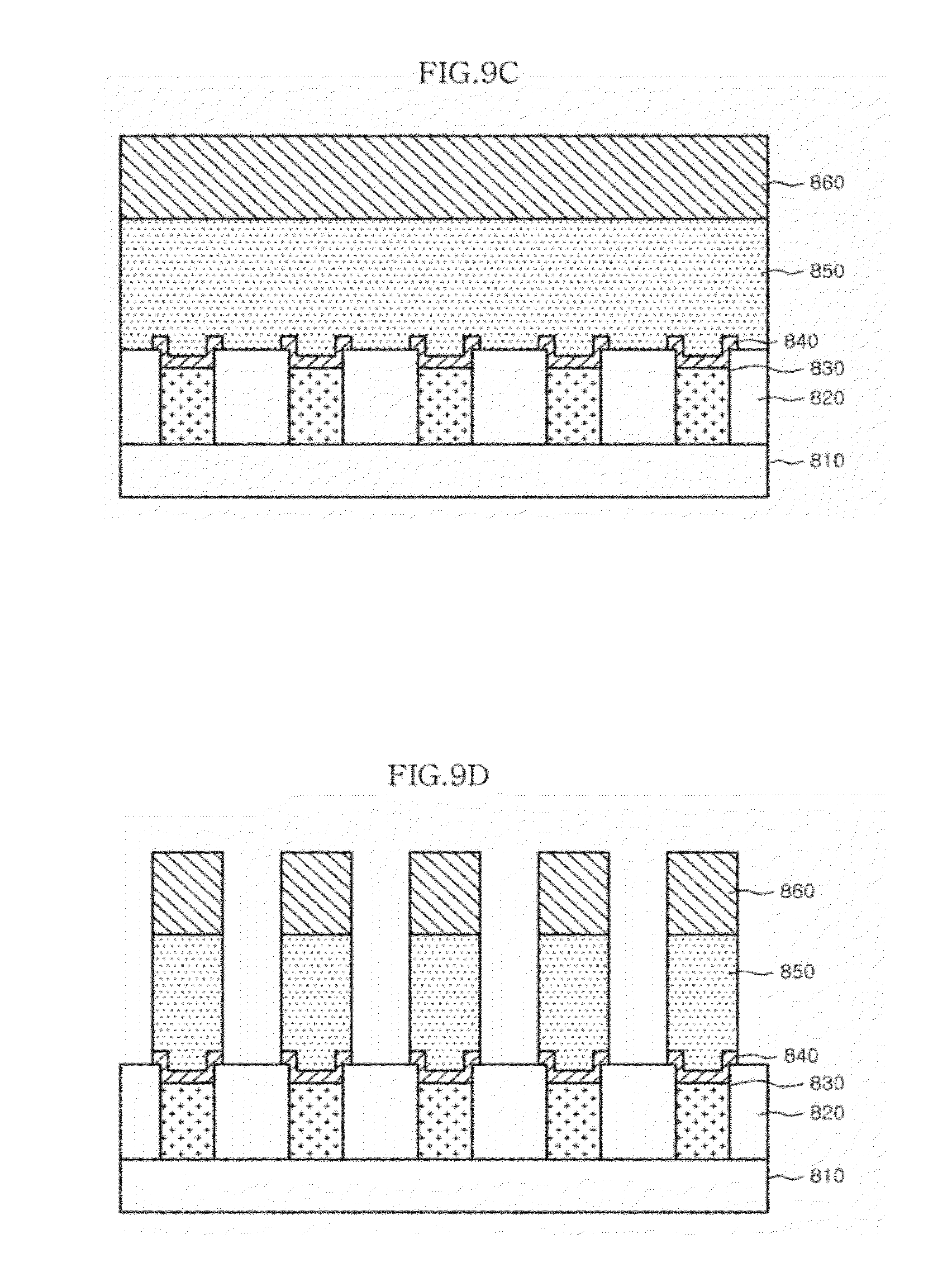

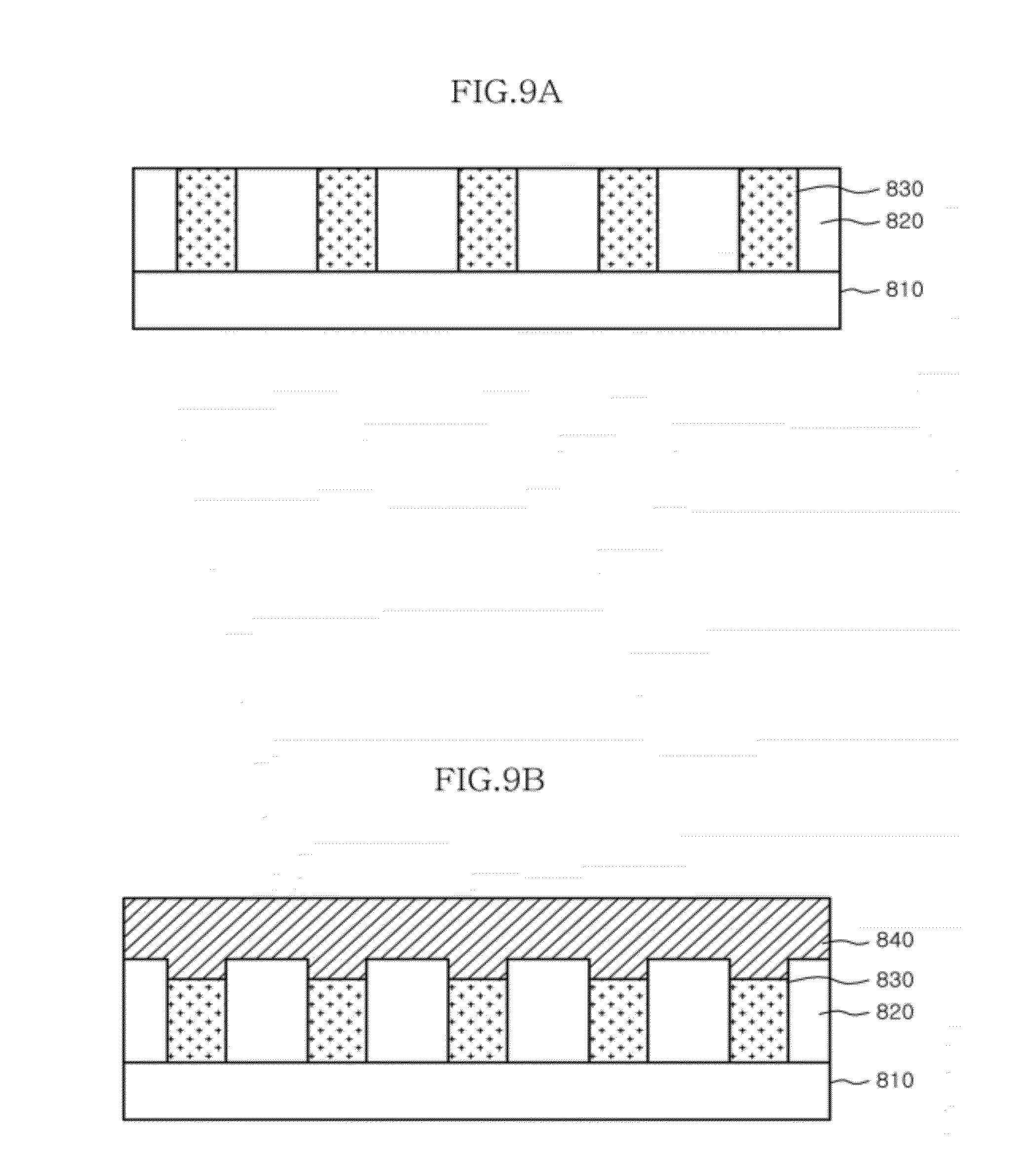

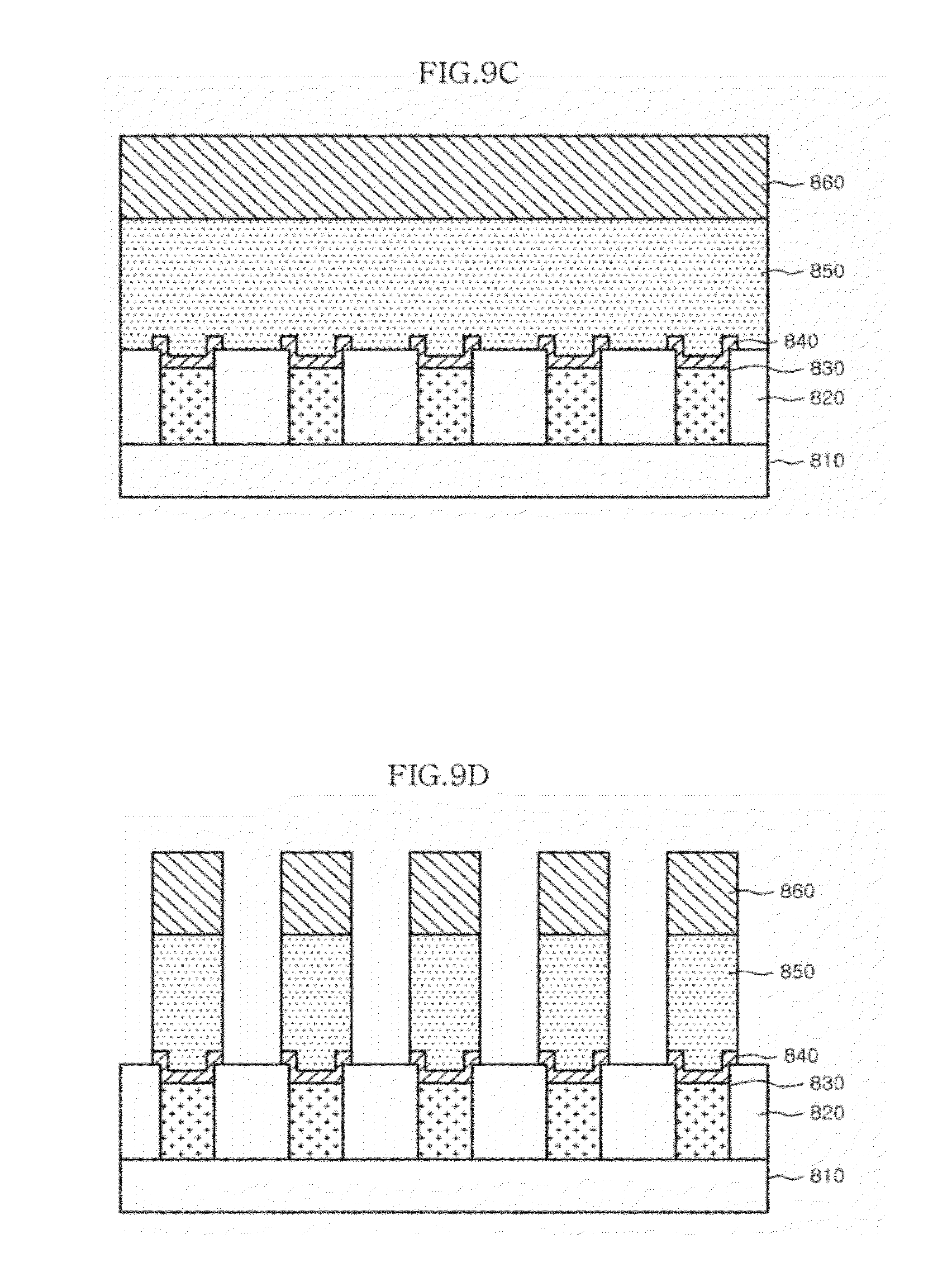

[0025] FIGS. 9A to 9D are cross-sectional views sequentially showing the processes of a method for forming diodes of the phase-change random access memory device in accordance with the third embodiment of the present invention.

DETAILED DESCRIPTION

[0026] Hereinafter, a phase-change random access memory device and a method for manufacturing the same according to the present invention will be described below with reference to the accompanying drawings through exemplary embodiments.

[0027] FIG. 3 is a cross-sectional view illustrating a phase-change random access memory device in accordance with a first embodiment of the present invention, and FIG. 4 is a plan view showing the arrangement of diodes in the phase-change random access memory device in accordance with the first embodiment of the present invention.

[0028] Referring to FIG. 3, in a phase-change random access memory device 300 in accordance with a first embodiment of the present invention, a first interlayer dielectric layer 320 is formed on a semiconductor substrate 310, and metal contacts 330 are formed in portions of the first interlayer dielectric layer 320 using a metallic substance. The first interlayer dielectric layer 320 may include an oxide layer.

[0029] A second interlayer dielectric layer 340 is deposited on the first interlayer dielectric layer 320 and the metal contacts 330, and an ohmic contact layer 350 is formed in portions of the second interlayer dielectric layer 340, which correspond to the metal contacts 330, to have recesses defined therein. The reason why the recesses are defined in the ohmic contact layer 350 is to increase force for supporting diodes 360, which are to be formed in a subsequent process and prevent diode patterns from inclining. The second interlayer dielectric layer 340 may include an oxide layer.

[0030] The diodes 360 are formed on the ohmic contact layer 350 using polysilicon.

[0031] The diodes 360 of the phase-change random access memory device 300 in accordance with the first embodiment of the present invention, formed in this way, may be disposed in a honeycomb shape as shown in FIG. 4. That is to say, diodes B, C, D, E, F, and G which surround a diode A are disposed at the same distance from the diode A. Therefore, the phase-change random access memory device 300 in accordance with the first embodiment of the present invention is formed such that a distance between is adjoining diodes 360, that is, a CD (critical dimension), is the same. By having the CD to be the same for adjoining diodes 360 in the phase-change random access memory device 300 in accordance with the first embodiment of the present invention, a distance between adjoining memory cells is increased, so that the adjoining memory cells are not adversely influenced by one another when performing etching and the diodes 360 may be prevented from inclining during etching.

[0032] Hereafter, a method for forming diodes of the phase-change random access memory device in accordance with the first embodiment of the present invention will be described in detail with reference to FIGS. 5a to 5e.

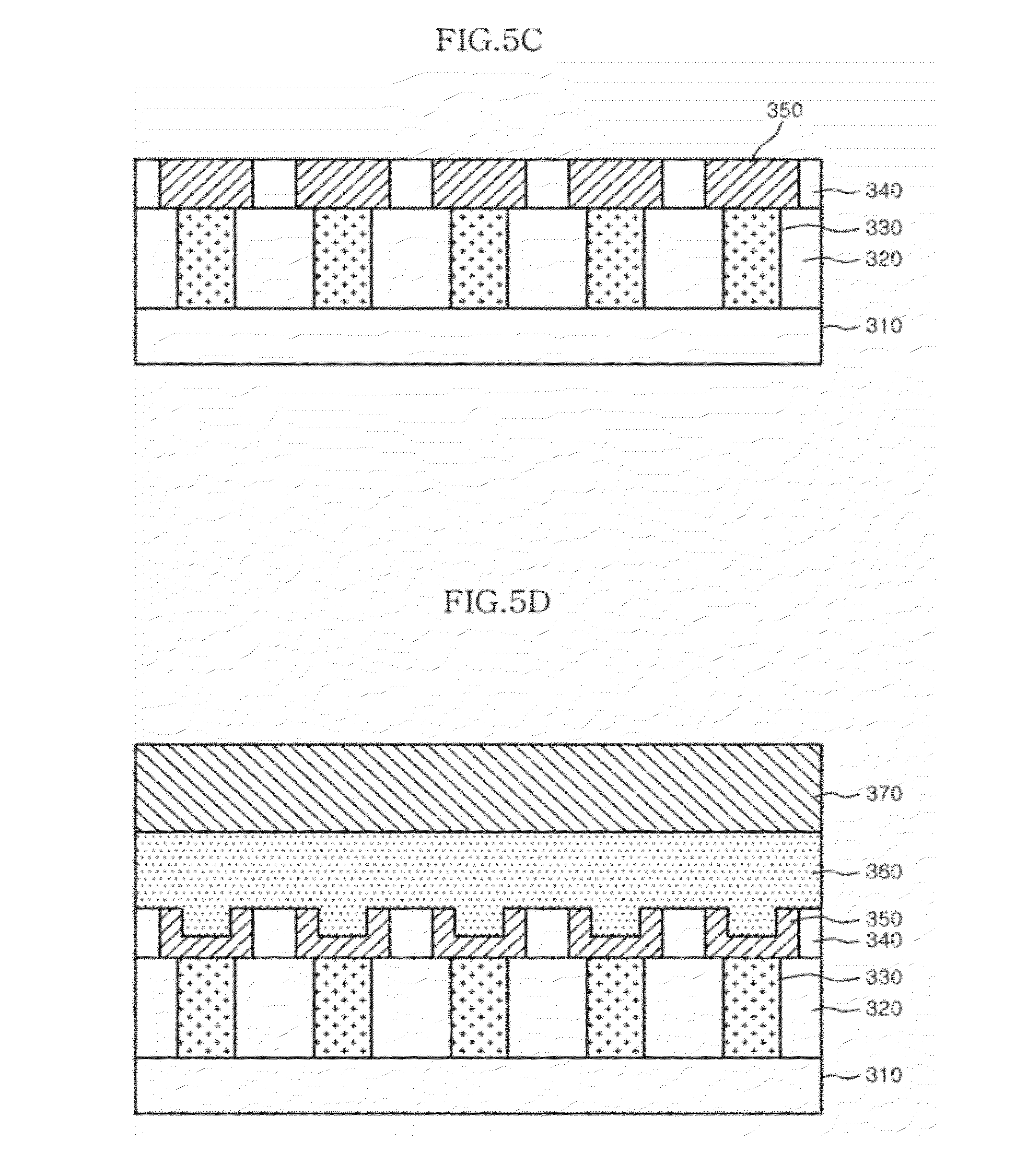

[0033] FIGS. 5A to 5E are cross-sectional views sequentially showing the processes of a method for forming diodes of the phase-change random access memory device in accordance with the first embodiment of the present invention.

[0034] Referring to FIG. 5A, a semiconductor substrate 310 is provided, and a first interlayer dielectric layer 320 is deposited on the semiconductor substrate 310 through HDP CVD (high density plasma chemical vapor deposition) to a desired height. The first interlayer dielectric layer 320 may include an oxide layer.

[0035] After creating holes by dry etching the first interlayer dielectric layer 320, metal contacts 330 are formed by filling a metallic substance, in particular, tungsten (W), in the holes.

[0036] Referring to FIG. 5B, after depositing a second interlayer dielectric layer 340 on the first interlayer dielectric layer 320 and the metal contacts 330 through HDP CVD to a desired height, portions of the second interlayer dielectric layer 340, which correspond to the metal contacts 330, are etched through dry etching to expose the metal contacts 330, by which contact holes 350a are defined. The second interlayer dielectric layer 340 may include an oxide layer, and the overall deposition height of the second interlayer dielectric layer 340 may be lower than that of the first interlayer dielectric layer 320. The second interlayer dielectric layer 340 may be deposited to equal the height of an ohmic contact layer which is to be formed through a subsequent process to improve the adhesion force between the metal contacts 330 and diodes to be subsequently formed using polysilicon.

[0037] Referring to FIG. 5C, by filling titanium (TiN) in the contact holes 350a, an ohmic contact layer 350 is formed.

[0038] Referring to FIG. 5D, a mask pattern (not shown) is formed on a resultant structure with the ohmic contact layer 350 through well-known photolithography methods. By etching portions of the ohmic contact layer 350 which are exposed through the mask pattern, recesses are defined in the ohmic contact layer 350.

[0039] After a polysilicon layer 360 for forming diodes is deposited on the ohmic contact layer 350 defined with the recesses and on the second interlayer dielectric layer 340, a dielectric layer 370 for forming patterns of diodes is deposited on the polysilicon layer 360. The polysilicon layer 360 may be filled in the recesses of the ohmic contact layer 350, and the dielectric layer 370 may include a nitride layer.

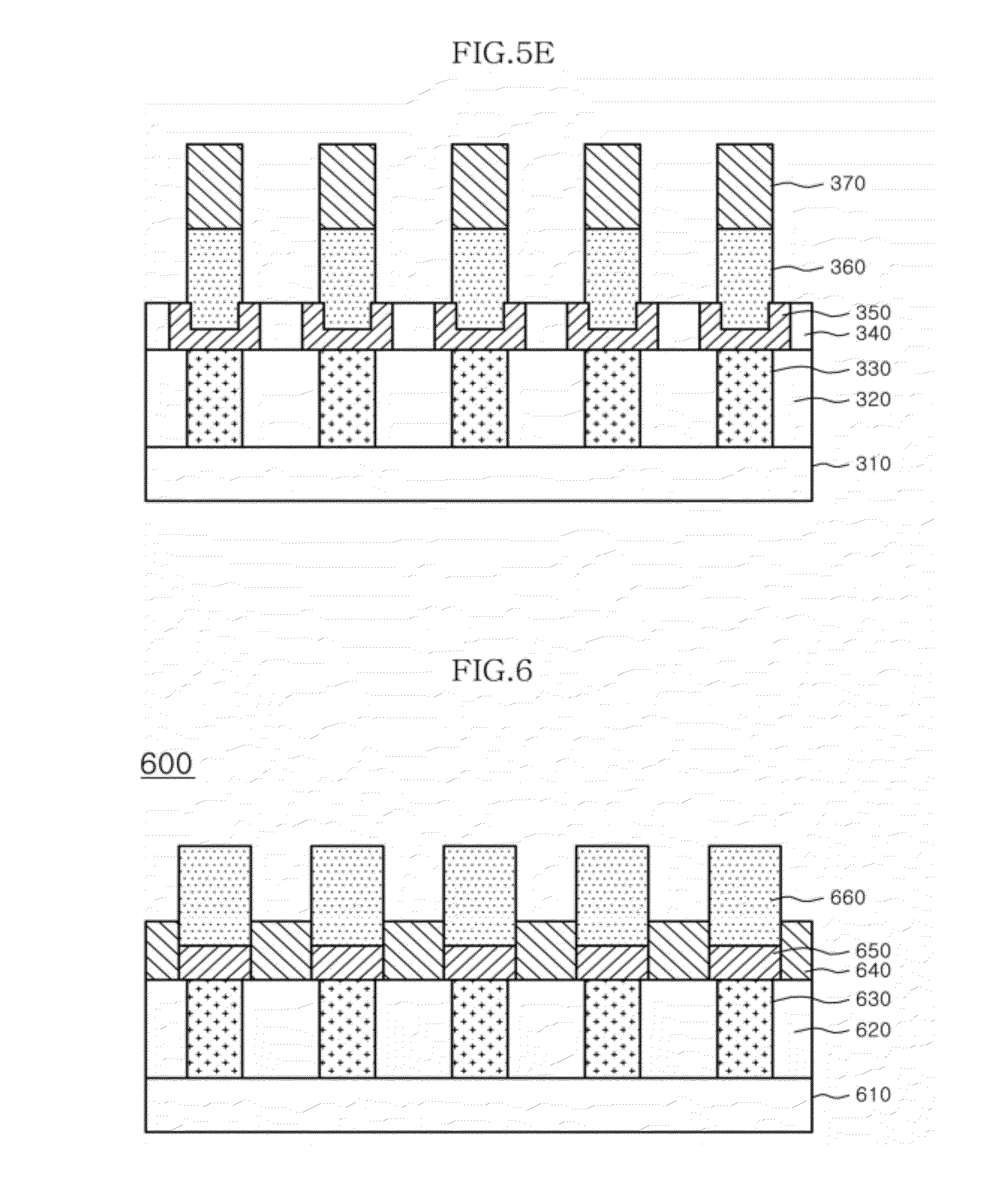

[0040] Referring to FIG. 5E, a mask pattern (not shown) is formed on the dielectric layer 370 by using well-known photolithography to expose diode forming regions. By simultaneously etching portions of the dielectric layer 370 which are exposed through the mask pattern and corresponding portions of the polysilicon layer 360, diodes 360 are formed. The dielectric layer 370 is removed in a subsequent process for further forming the phase-change random access memory device 300 in accordance with the first embodiment of the present invention.

[0041] In the phase-change random access memory device 300 in accordance with the first embodiment of the present invention and the method for manufacturing the same, the diodes 360 are formed by defining the recesses in the ohmic contact layer 350 to improve the adhesion force between the metal contacts 330 and the diodes 360. Thus, diode patterns may be prevented from inclining and adequate reliability of the phase-change random access memory device 300 may be obtained.

[0042] Also, in the phase-change random access memory device 300 in accordance with the first embodiment of the present invention and the method for manufacturing the same, the diodes 360 are disposed at the same distance from one another to thus prevent diode patterns from inclining and achieve adequate reliability of the phase-change random access memory device 300.

[0043] Hereafter, a phase-change random access memory device for preventing inclining of diode patterns in accordance with a second embodiment of the present invention and a method for manufacturing the same will be described.

[0044] FIG. 6 is a cross-sectional view illustrating a phase-change random access memory device in accordance with a second embodiment of the present invention.

[0045] Referring to FIG. 6, in a phase-change random access memory device 600 in accordance with a second embodiment of the present invention, a first interlayer dielectric layer 620 is formed on a semiconductor substrate 610, and metal contacts 630 are formed in portions of the first interlayer dielectric layer 620 using a metallic substance. The first interlayer dielectric layer 620 may include an oxide layer.

[0046] A second interlayer dielectric layer 640 is formed on the first interlayer dielectric layer 620 and the metal contacts 630 to a desired height. An ohmic contact layer 650 made of titanium (TiN) and diodes 660 made of polysilicon are sequentially formed in portions of the second interlayer dielectric layer 640, which correspond to the metal contacts 630. The second interlayer dielectric layer 640 may include a nitride layer and may be deposited to a height reaching 1/3 of the height of the diodes 660. The reason why the deposition height of the second interlayer dielectric layer 640 is controlled in this way is to increase supporting force for the diodes 660 in a subsequent process and prevent diode patterns from inclining.

[0047] The diodes 660 made of polysilicon are formed on the ohmic contact layer 650.

[0048] In the phase-change random access memory device 600 in accordance with the second embodiment of the present invention, as can be seen from FIG. 4, memory cells may be disposed in a honeycomb shape so that they are positioned at the same distance from one another.

[0049] Hereafter, a method for forming diodes of the phase-change random access memory device 600 in accordance with the second embodiment of the present invention will be described with reference to FIGS. 7A to 7D.

[0050] FIGS. 7A to 7D are cross-sectional views sequentially showing the processes of a method for forming diodes of the phase-change random access memory device in accordance with the second embodiment of the present invention.

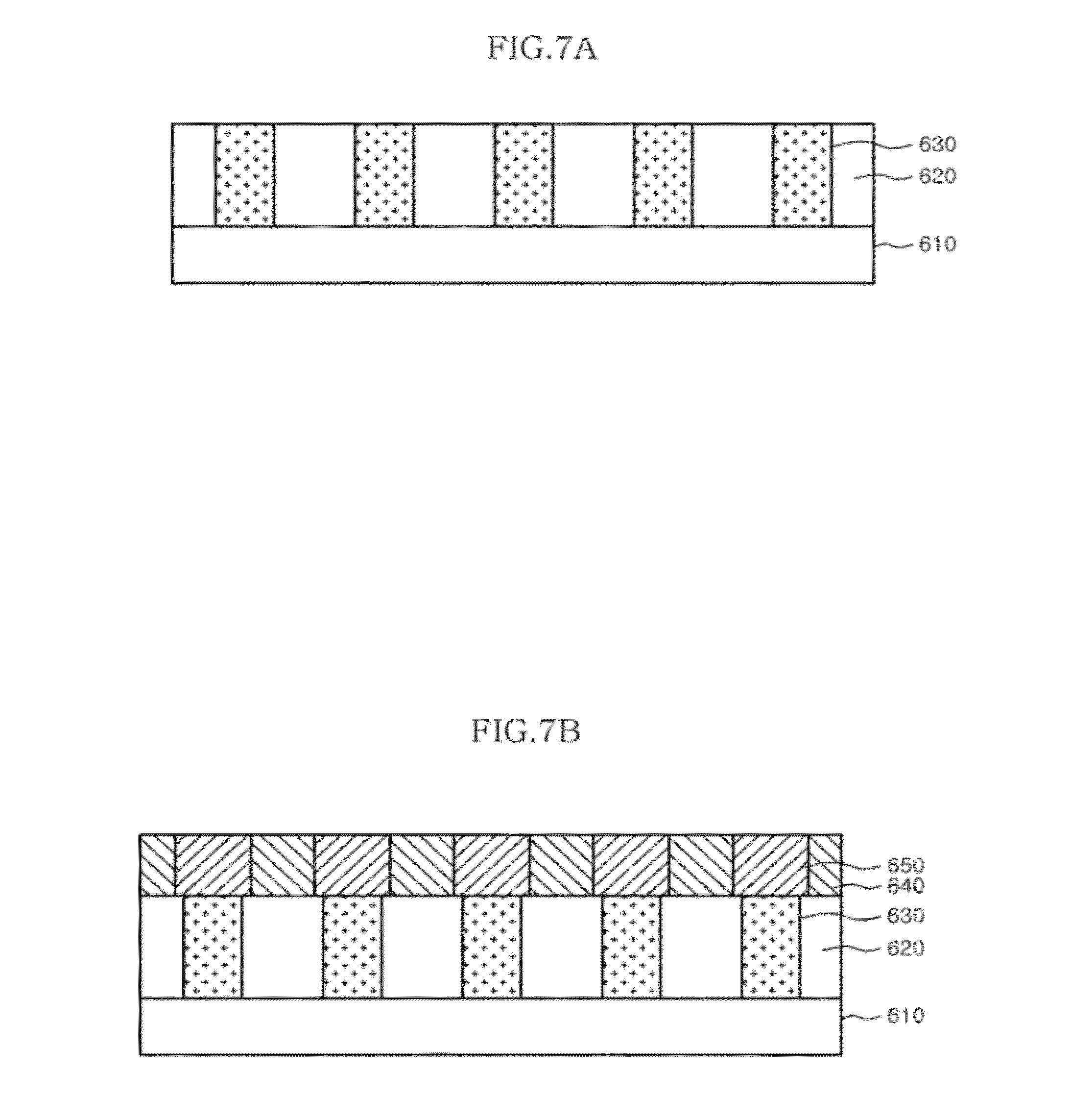

[0051] Referring to FIG. 7A, a semiconductor substrate 610 is provided, and a first interlayer dielectric layer 620 is deposited on the semiconductor substrate 610 through HDP CVD to a desired height. The first interlayer dielectric layer 620 may include an oxide layer. After defining holes through dry etching of the first interlayer dielectric layer 620, metal contacts 630 are formed by filling a metallic substance, in particular, tungsten (W), in the holes.

[0052] Referring to FIG. 7B, after depositing a second interlayer dielectric layer 640 on the first interlayer dielectric layer 620 and the metal contacts 630 to a desired height, portions of the second interlayer dielectric layer 640, which correspond to the metal contacts 630, are etched through dry etching to expose the metal contacts 630, by which contact holes are defined. The second interlayer dielectric layer 640 may include a nitride layer and may be deposited to a height reaching to 1/3 of the height of diodes which are to be formed in a subsequent process. By filling titanium nitride (TiN) in the contact holes defined in this way, an ohmic contact layer 650 is formed.

[0053] Referring to FIG. 7C, a mask pattern (not shown) is formed on the ohmic contact layer 650 by using well-known photolithography methods. By etching portions of the ohmic contact layer 650 which are exposed through the mask pattern, the ohmic contact layer 650 remains, for example, only on the bottoms of the contact holes.

[0054] After depositing a polysilicon layer 660 for forming diodes on the ohmic contact layer 650 and on the second interlayer dielectric layer 640, a dielectric layer 670 for forming patterns of diodes is deposited on the polysilicon layer 660. The dielectric layer 670 may include a nitride layer.

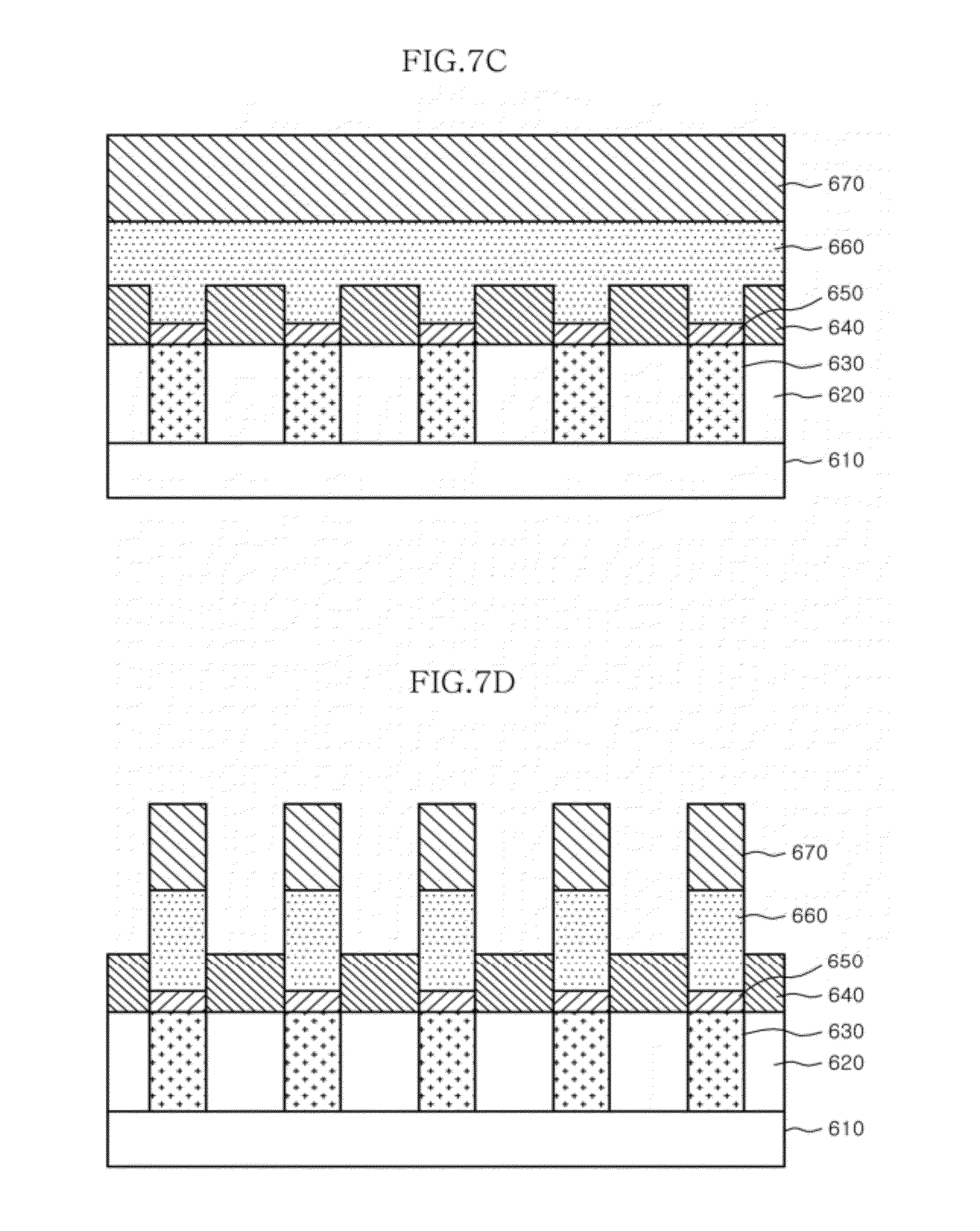

[0055] Referring to FIG. 7D, a mask pattern (not shown) is formed on the dielectric layer 670 by using well-known photolithography methods to expose diode forming regions. By simultaneously etching portions of the dielectric layer 670 which are exposed through the mask pattern and corresponding portions of the polysilicon layer 660, diodes 660 are formed. The dielectric layer 670 is removed in a subsequent process for further forming the phase-change random access memory device 600 in accordance with the second embodiment of the present invention.

[0056] In the phase-change random access memory device 600 in accordance with the second embodiment of the present invention and the method for manufacturing the same, the ohmic contact layer 650 and the second interlayer dielectric layer 640 are formed in such a way as to support portions of the diodes 660. By supporting portions of the diodes 660, diode patterns may be prevented from inclining and adequate reliability of the phase-change random access memory device 600 may be obtained.

[0057] Hereafter, a phase-change random access memory device for preventing inclining of diode patterns in accordance with a third embodiment of the present invention and a method for manufacturing the same will be described.

[0058] FIG. 8 is a cross-sectional view illustrating a phase-change random access memory device in accordance with a third embodiment of the present invention.

[0059] Referring to FIG. 8, in a phase-change random access memory device 800 in accordance with a third embodiment of the present invention, an interlayer dielectric layer 820 is formed on a semiconductor substrate 810, and metal contacts 830 are formed in to portions of the interlayer dielectric layer 820 using a metallic substance. The metal contacts 830 are not formed at the same height as the interlayer dielectric layer 820, but are formed at a height lower than the interlayer dielectric layer 820 due to the fact that the metallic substance for the metal contacts 830 is etched to some extent. The metallic substance is etched so as not to exert an influence on the performance of the metal contacts 830. The interlayer dielectric layer 820 may include an oxide layer.

[0060] An ohmic contact layer 840 is formed in a substantial sectional shape of U on the metal contacts 830 and on the sidewalls of the holes defined in the interlayer dielectric layer 820 due to etching of the metallic substance and on portions of the interlayer dielectric layer 820 around the holes. Diodes 850 made of polysilicon are formed on the ohmic contact layer 840.

[0061] In the phase-change random access memory device 800 in accordance with the third embodiment of the present invention, as can be readily seen from FIG. 4, memory cells may be disposed in a honeycomb shape so that they are positioned at the same distance from one another.

[0062] In the phase-change random access memory device 800 in accordance with the third embodiment of the present invention, the upper portions of the metal contacts 830 are etched, the ohmic contact layer 840 is formed in the etched portions, and the diodes 850 are formed on the ohmic contact layer 840, where diode patterns may be prevented from inclining.

[0063] Hereafter, a method for forming diodes of the phase-change random access memory device 800 in accordance with the third embodiment of the present invention will be described with reference to FIGS. 9A to 9D.

[0064] FIGS. 9A to 9D are cross-sectional views sequentially showing the processes of a method for forming diodes of the phase-change random access memory device in accordance with the third embodiment of the present invention.

[0065] Referring to FIG. 9A, a semiconductor substrate 810 is provided, and an interlayer dielectric layer 820 is deposited on the semiconductor substrate 810 through HDP CVD (high density plasma chemical vapor deposition) to a desired height. After defining holes through dry etching of the interlayer dielectric layer 820, metal contacts 830 are formed by filling a metallic substance, in particular, tungsten (W), in the holes. The interlayer dielectric layer 820 may include an oxide layer.

[0066] Referring to FIG. 9B, the upper portions of the metal contacts 830 are etched through an etch-back process so that the metal contacts 830 have a height lower than the interlayer dielectric layer 820. Titanium (TiN) for forming an ohmic contact layer is deposited on the metal contacts 830 etched in this way and on the interlayer dielectric layer 820.

[0067] Referring to FIG. 9C, by etching the deposited titanium (TiN) to have a I sectional shape of U substantially on the metal contacts 830, on the sidewalls of the holes defined in the interlayer dielectric layer 820 due to etching of the metal contacts 830 and on portions of the interlayer dielectric layer 820 around the holes, an ohmic contact layer 840 is formed.

[0068] After depositing a polysilicon layer 850 for forming diodes on the ohmic contact layer 840 and on the interlayer dielectric layer 820, a dielectric layer 860 for forming patterns of diodes is formed on the polysilicon layer 850. The dielectric layer 860 may include a nitride layer.

[0069] Referring to FIG. 9D, a mask pattern (not shown) is formed on the dielectric layer 860 through well-known photolithography methods to expose diode forming regions. By simultaneously etching portions of the dielectric layer 860 which are exposed through the mask pattern and corresponding portions of the polysilicon layer 850, diodes 850 are formed. The dielectric layer 860 is removed in a subsequent process for further forming the phase-change random access memory device 800 in accordance with the third embodiment of the present invention.

[0070] In the phase-change random access memory device 800 in accordance with the third embodiment of the present invention and the method for manufacturing the same, the upper portions of the metal contacts 830 are etched to allow the ohmic contact layer 840 to have a section shape of U substantially and the diodes 850 are formed on the ohmic contact layer 840. Thus, diode patterns may be prevented from inclining and adequate reliability of the phase-change random access memory device 800 may be obtained.

[0071] While certain embodiments have been described above, it will be understood to those skilled in the art that the embodiments described are by way of example only. Accordingly, the phase-change random access memory device and the method for manufacturing the same described herein should not be limited to the described embodiments. Rather, the phase-change random access memory device and the method for manufacturing the same described herein is to include all embodiments that is consistent with the above-described features of the exemplary embodiments.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.