Passivated Upstanding Nanostructures And Methods Of Making The Same

Yu; Young-June ; et al.

U.S. patent application number 13/106851 was filed with the patent office on 2011-12-29 for passivated upstanding nanostructures and methods of making the same. This patent application is currently assigned to ZENA TECHNOLOGIES, INC.. Invention is credited to Munib Wober, Young-June Yu.

| Application Number | 20110315988 13/106851 |

| Document ID | / |

| Family ID | 45351678 |

| Filed Date | 2011-12-29 |

View All Diagrams

| United States Patent Application | 20110315988 |

| Kind Code | A1 |

| Yu; Young-June ; et al. | December 29, 2011 |

PASSIVATED UPSTANDING NANOSTRUCTURES AND METHODS OF MAKING THE SAME

Abstract

Described herein is a device comprising: a substrate; one or more of a nanostructure extending essentially perpendicularly from the substrate; wherein the nanostructure comprises a core of a doped semiconductor, an first layer disposed on the core, and a second layer of an opposite type from the core and disposed on the first layer.

| Inventors: | Yu; Young-June; (Cranbury, NJ) ; Wober; Munib; (Topsfield, MA) |

| Assignee: | ZENA TECHNOLOGIES, INC. Cambridge MA |

| Family ID: | 45351678 |

| Appl. No.: | 13/106851 |

| Filed: | May 12, 2011 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 12573582 | Oct 5, 2009 | |||

| 13106851 | ||||

| 12575221 | Oct 7, 2009 | |||

| 12573582 | ||||

| 12633323 | Dec 8, 2009 | |||

| 12575221 | ||||

| 12633318 | Dec 8, 2009 | |||

| 12633323 | ||||

| 12633313 | Dec 8, 2009 | |||

| 12633318 | ||||

| 12633305 | Dec 8, 2009 | |||

| 12633313 | ||||

| 12982269 | Dec 30, 2010 | |||

| 12633305 | ||||

| 12966573 | Dec 13, 2010 | |||

| 12982269 | ||||

| 12967880 | Dec 14, 2010 | |||

| 12966573 | ||||

| 12974499 | Dec 21, 2010 | |||

| 12967880 | ||||

| 12945492 | Nov 12, 2010 | |||

| 12974499 | ||||

| 13047392 | Mar 14, 2011 | |||

| 12945492 | ||||

| 13048635 | Mar 15, 2011 | |||

| 13047392 | ||||

| Current U.S. Class: | 257/52 ; 257/458; 257/E21.09; 257/E29.003; 257/E31.061; 438/478; 977/762; 977/954 |

| Current CPC Class: | H01L 31/145 20130101; H01L 31/107 20130101; H01L 33/06 20130101; H01L 27/156 20130101; H01L 31/1055 20130101; H01L 31/035227 20130101; Y02E 10/547 20130101; H01L 27/14 20130101; H01L 31/105 20130101; H01L 27/1446 20130101; H01L 27/14643 20130101; H01L 31/02168 20130101; H01L 31/02161 20130101; H01L 27/1462 20130101; H01L 31/02322 20130101; H01L 31/028 20130101; H01L 31/022408 20130101 |

| Class at Publication: | 257/52 ; 438/478; 257/458; 257/E29.003; 257/E21.09; 257/E31.061; 977/762; 977/954 |

| International Class: | H01L 29/04 20060101 H01L029/04; H01L 21/20 20060101 H01L021/20; H01L 31/105 20060101 H01L031/105 |

Claims

1. A device comprising: a substrate; one or more of a nanostructure extending essentially perpendicularly from the substrate; wherein the nanostructure comprises a core of a doped semiconductor of a first type, a first layer comprising a lightly doped amorphous semiconductor or an intrinsic amorphous semiconductor, and a second layer comprising a heavily doped amorphous semiconductor layer of a second type opposite from the first type, wherein the first layer is disposed on the core and the second layer is disposed on the first layer.

2. The device of claim 1, wherein the first layer is configured to passivate at least a surface of the core.

3. The device of claim 1, wherein the first layer is disposed isotropically over at least an end portion of the core away from the substrate.

4. The device of claim 3, wherein the second layer is disposed isotropically over at least a portion of the first layer.

5. The device of claim 1, wherein the first layer is disposed on an end surface of the core away from the substrate.

6. The device of claim 5, wherein the second layer is disposed on the first layer.

7. The device of claim 6, wherein the first layer and the second layer are coextensive with the core in at least a direction parallel to the substrate.

8. The device of claim 5, wherein sidewalls of the core are at least partially covered by an electrically insulating layer.

9. The device of claim 8, wherein the first layer and the second layer are coextensive with the electrically insulating layer in at least a direction parallel to the substrate.

10. (canceled)

11. (canceled)

12. The device of claim 1, wherein the core comprises one or more doped semiconductor material selected from the group consisting of doped silicon, doped germanium, doped III-V group compound semiconductor, doped II-VI group compound semiconductor, and doped quaternary semiconductor; wherein the first layer comprises one or more intrinsic amorphous semiconductor material selected from the group consisting intrinsic amorphous silicon, intrinsic amorphous germanium, intrinsic amorphous III-V group compound semiconductor and intrinsic amorphous II-VI group compound semiconductor; and wherein the second layer comprises one or more heavily doped amorphous semiconductor material selected from the group consisting heavily doped amorphous silicon, heavily doped amorphous germanium, heavily doped amorphous III-V group compound semiconductor and heavily doped amorphous II-VI group compound semiconductor.

13. (canceled)

14. The device of claim 1, wherein the core is lightly doped.

15. (canceled)

16. (canceled)

17. The device of claim 1, wherein the first layer has a thickness of about 2 nm to about 100 nm.

18. (canceled)

19. The device of claim 1, wherein the second layer has a thickness of at least about 10 nm.

20. The device of claim 1, wherein the second layer, the first layer and the core form a p-i-n junction.

21. (canceled)

22. The device of claim 1, wherein the nanostructure is a nanowire or a nanoslab.

23. A method of manufacturing the device of claim 1, comprising depositing the first layer on the core by atomic layer deposition (ALD) or chemical vapor deposition (CVD); and depositing the second layer on the first layer by ALD or CVD.

24-176. (canceled)

177. A device comprising: a substrate; one or more of a nanostructure extending essentially perpendicularly from the substrate; wherein the nanostructure comprises a core and a passivation layer, the passivation layer configured to passivate at least a surface of the core and configured to form a p-i-n junction with the core.

178. The device of claim 177, wherein the passivation layer comprises an amorphous material.

179. A device comprising: a substrate; one or more of a nanostructure extending essentially perpendicularly from the substrate; wherein the nanostructure comprises a core and a passivation layer, the passivation layer configured to passivate at least a surface of the core; wherein the device is configured to convert light to electricity.

180. The device of claim 179, wherein the passivation layer is configured to form a p-i-n junction with the core and the p-i-n junction is functional to convert light to electricity.

181. (canceled)

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation-in-part of and claims the benefit of the earlier filing date of co-pending U.S. patent application Ser. Nos. 12/573,582, 12/575,221, 12/633,323, 12/633,318, 12/633,313, 12/633,305, 12/982,269, 12/966,573, 12/967,880, 12/974,499, 12/945,492, 13/047,392, and 13/048,635, the entire contents of each of which are incorporated herein by reference.

[0002] This application is related to U.S. patent application Ser. Nos. 61/266,064, 61/357,429, 61/360,421, 12/204,686 (granted as U.S. Pat. No. 7,646,943), 12/270,233, 12/472,264, 12/472,271, 12/478,598, 12/633,297, 12/621,497, 12/648,942, 12/910,664, 12/966,514, and 12/966,535, and the disclosures each of which are hereby incorporated by reference in their entirety.

BACKGROUND

[0003] Semiconductor surface is often a source of defects that adversely affect the electric, optical and chemical properties of the semiconductor. A suitable passivation technique eliminates the defects or prevent the adverse effects of the defects.

SUMMARY

[0004] Described herein is a device comprising: a substrate; one or more of a nanostructure extending essentially perpendicularly from the substrate; wherein the nanostructure comprises a core of a doped semiconductor, an intrinsic amorphous semiconductor layer disposed on the core, and a heavily doped amorphous semiconductor layer of an opposite type from the core and disposed on the intrinsic amorphous semiconductor layer.

[0005] Also described herein is a device comprising: a substrate; one or more of a nanostructure extending essentially perpendicularly from the substrate; wherein the nanostructure comprises a core and a passivation layer, the passivation layer comprising an amorphous material, configured to passivate at least a surface of the core and configured to form a p-i-n junction with the core.

BRIEF DESCRIPTION OF THE FIGURES

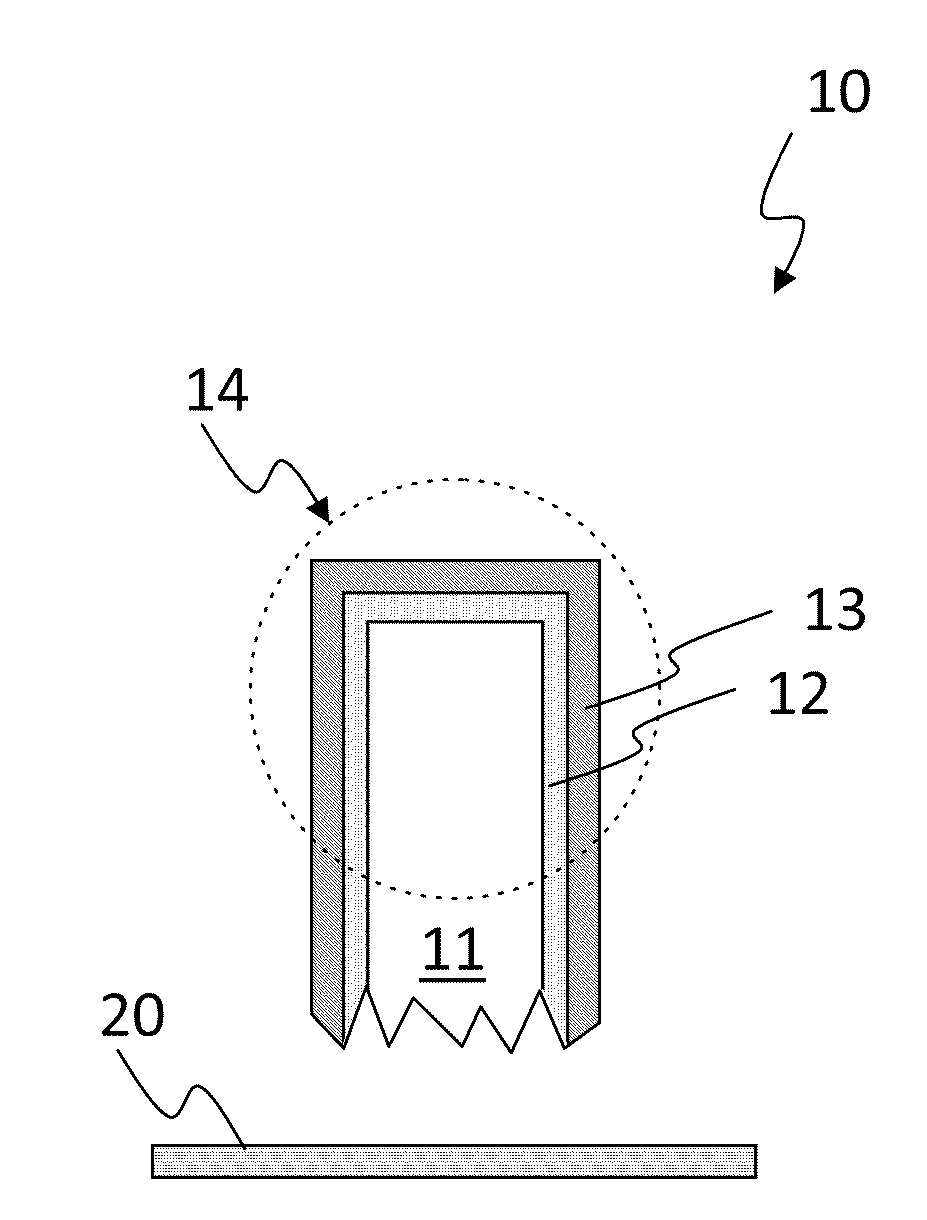

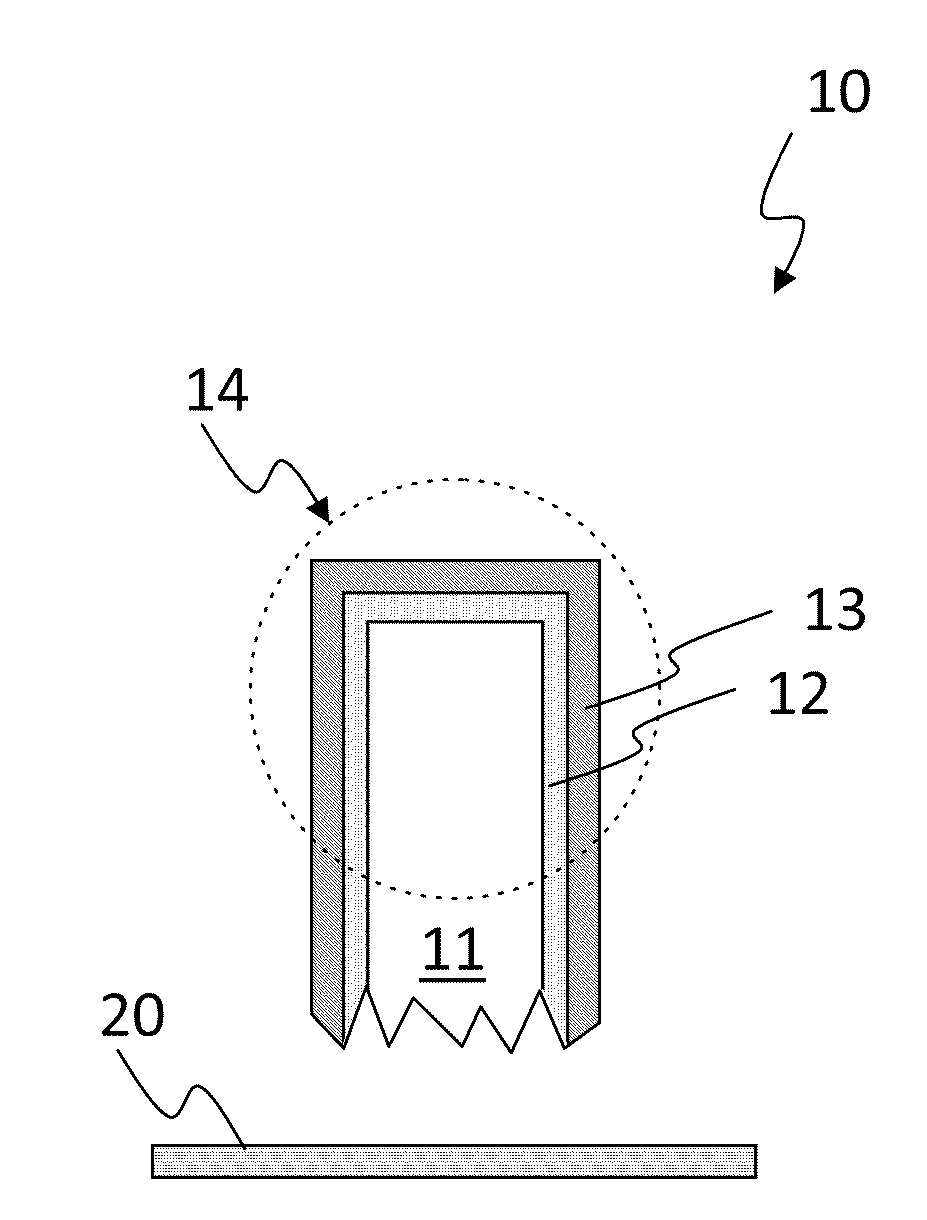

[0006] FIGS. 1A-1C each show a partial cross-sectional view of a nanostructure.

[0007] FIG. S1A shows a nanostructure on a substrate.

[0008] FIG. S1B shows simulated absorptance of the nanostructure of FIG. S1A.

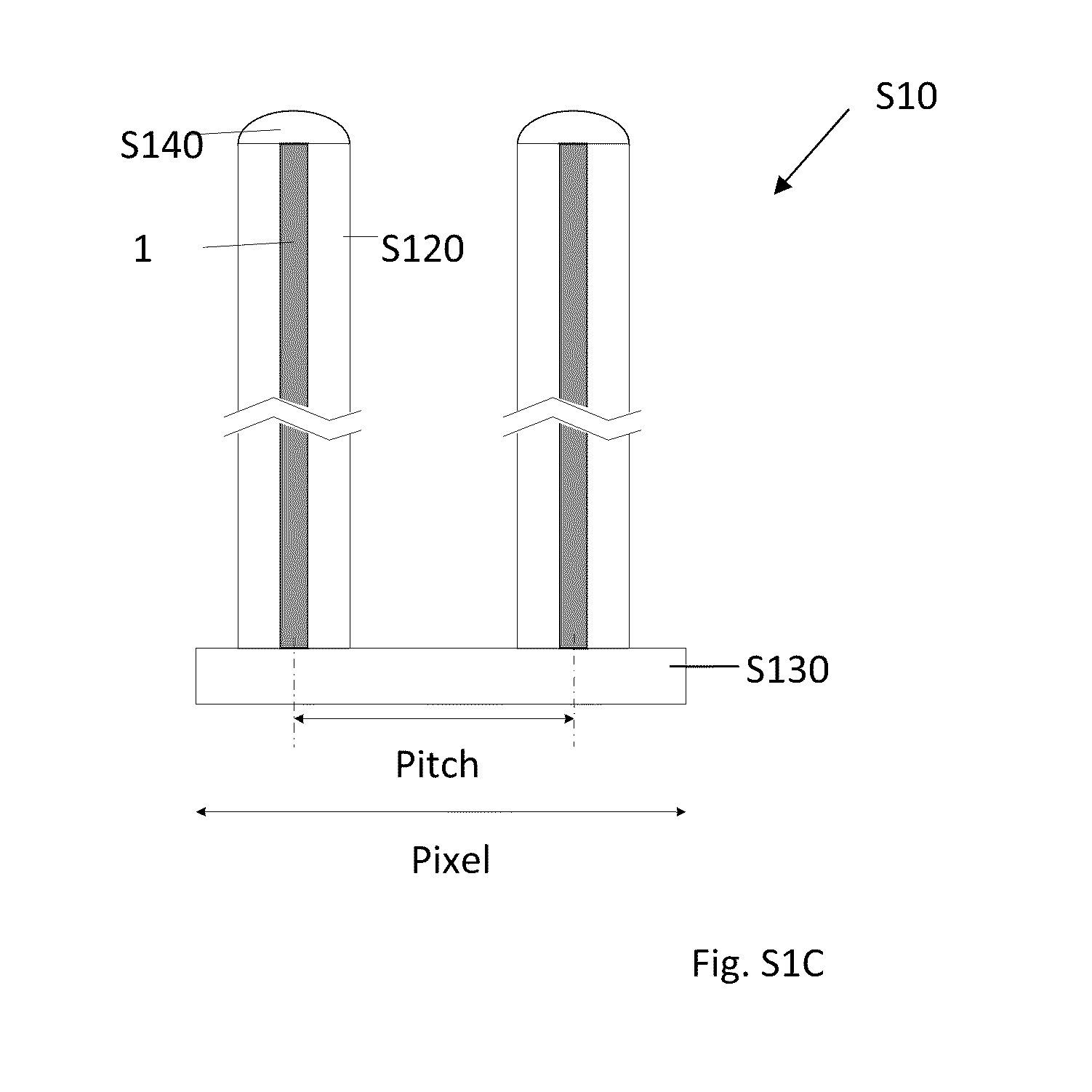

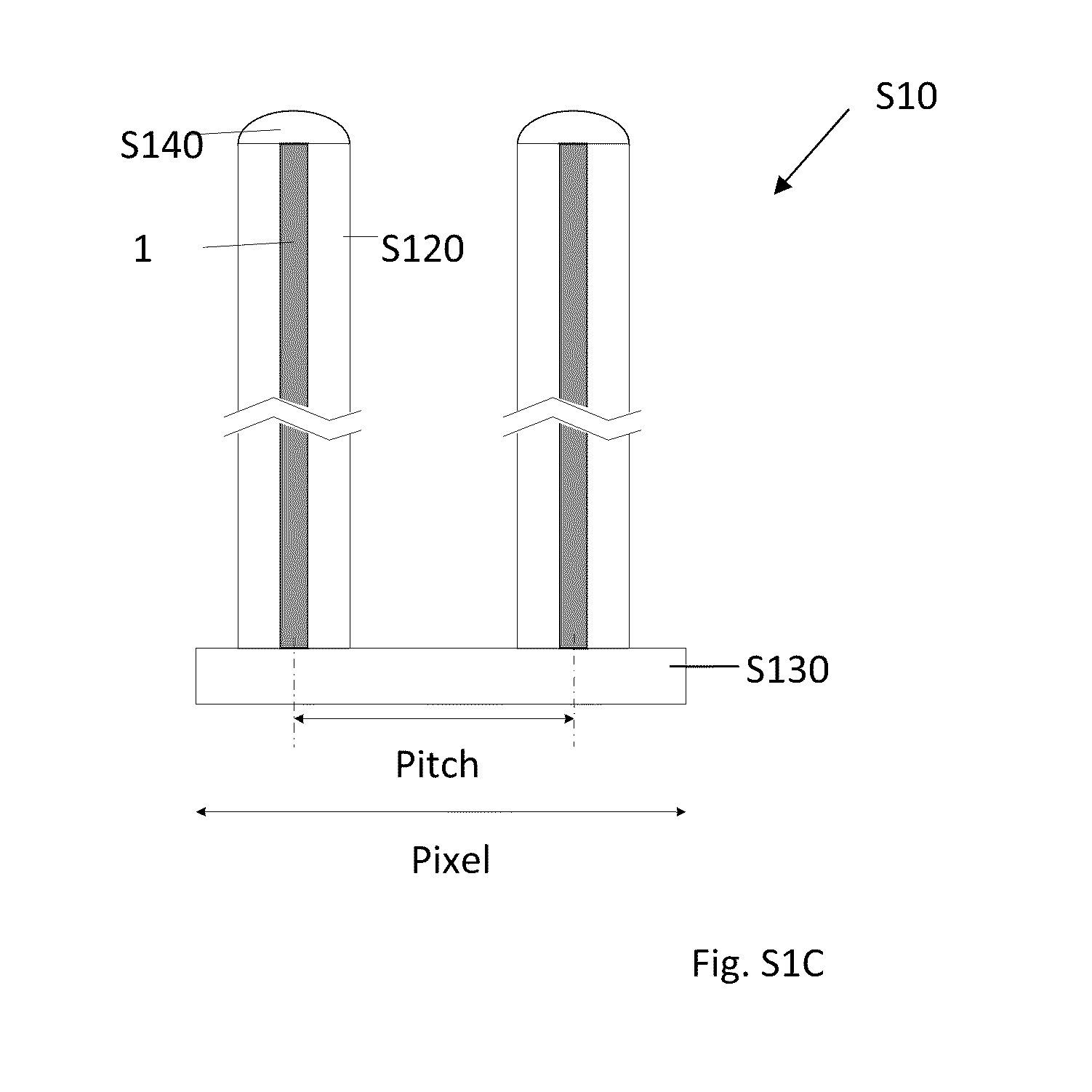

[0009] FIG. S1C shows optional couplers on the nanostructure.

[0010] FIGS. S2A and S2B show a perspective view and a top view of an image sensor according an embodiment.

[0011] FIG. S9 shows a block diagram of a solar-blind image sensor.

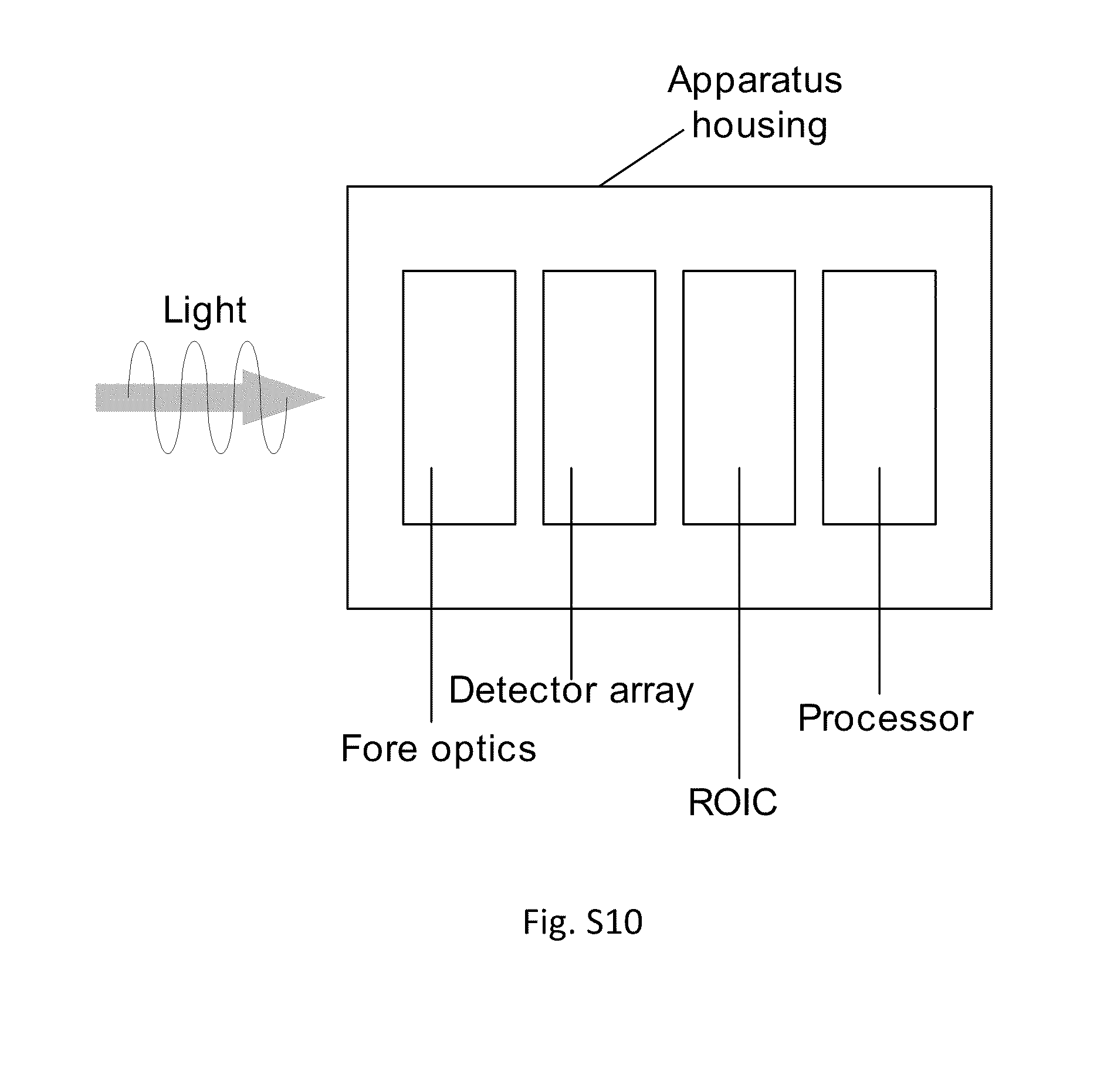

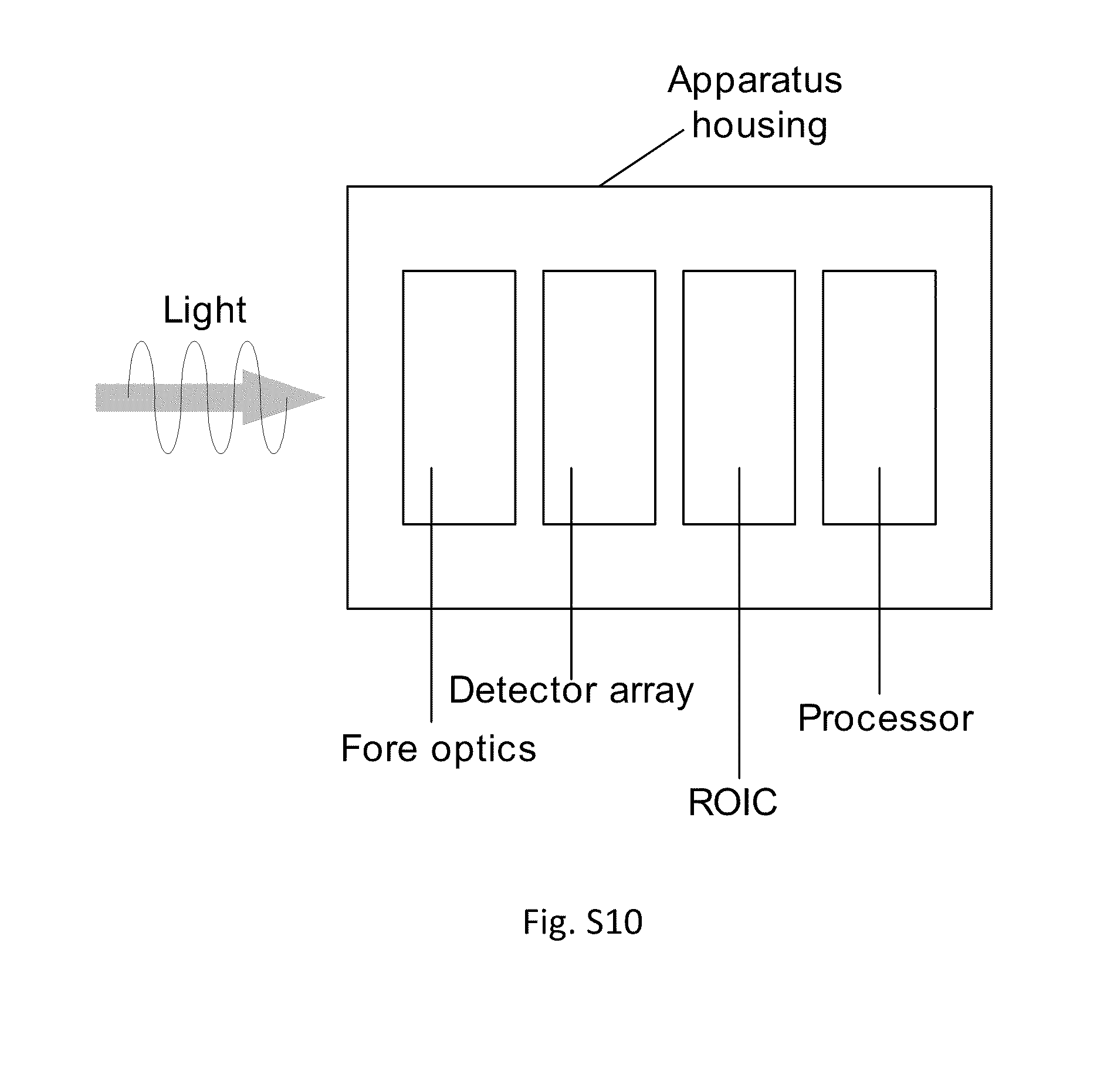

[0012] FIG. S10 shows a schematic of the SBUV detector being used as fore optics.

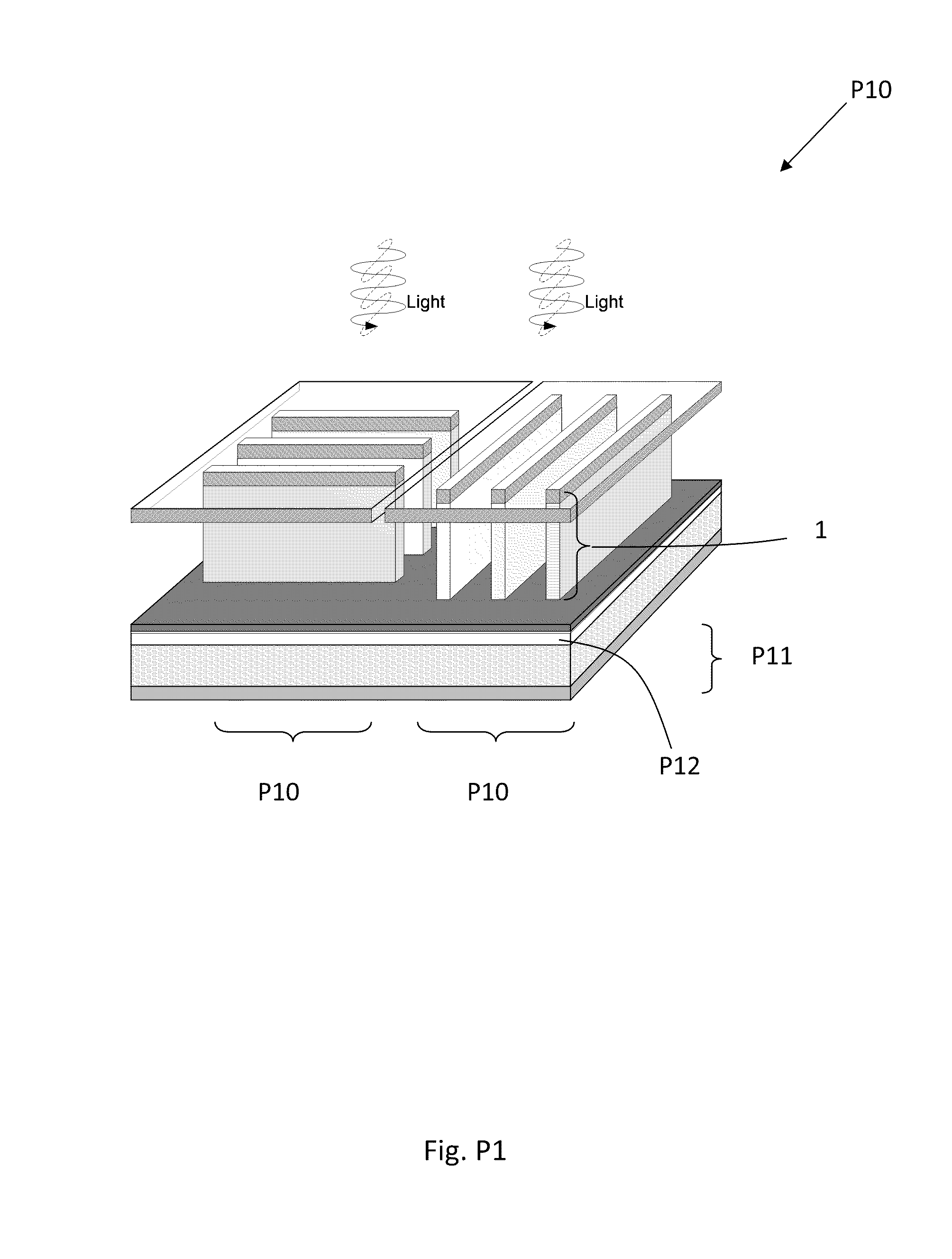

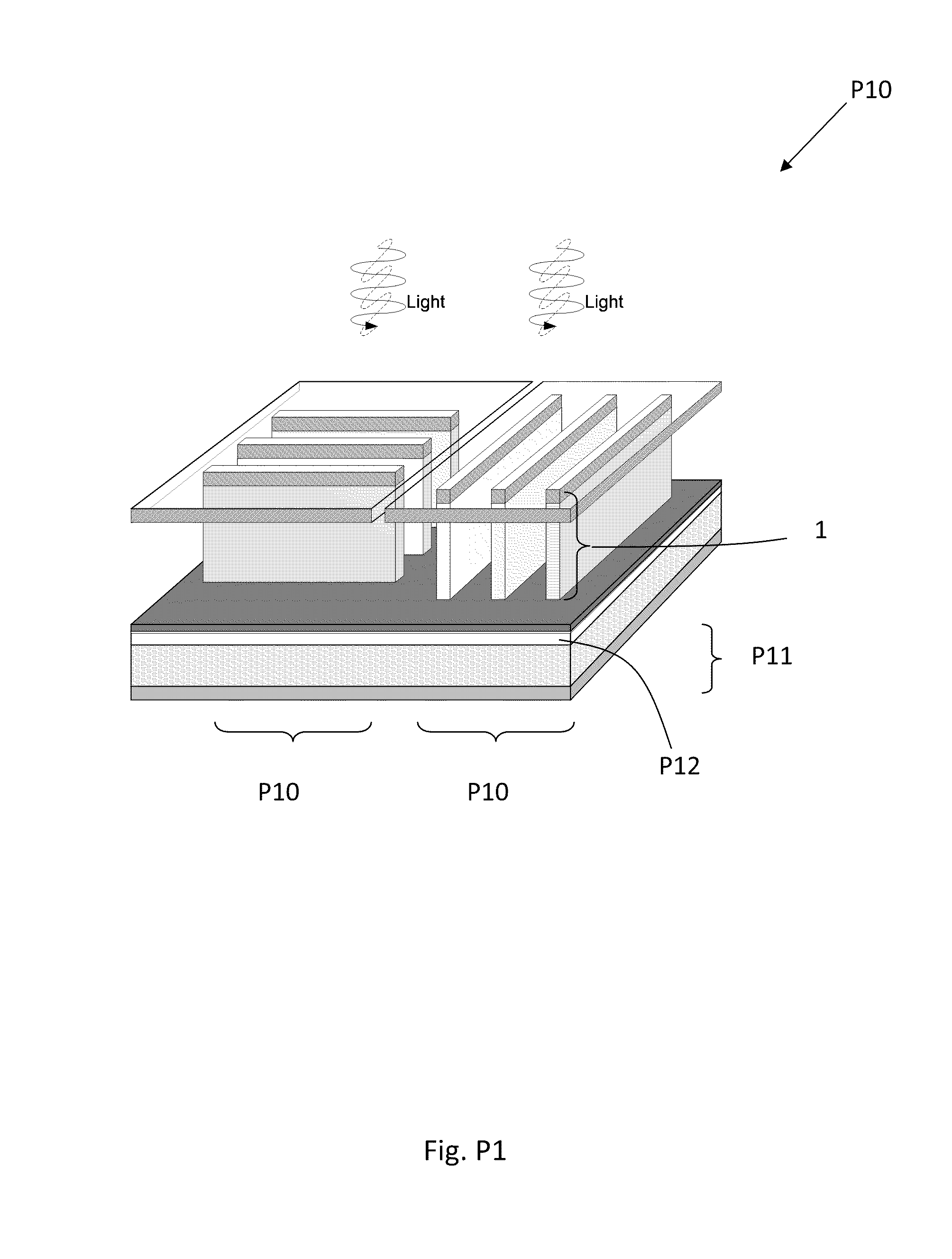

[0013] FIG. P1 is a perspective view of the device according one embodiment.

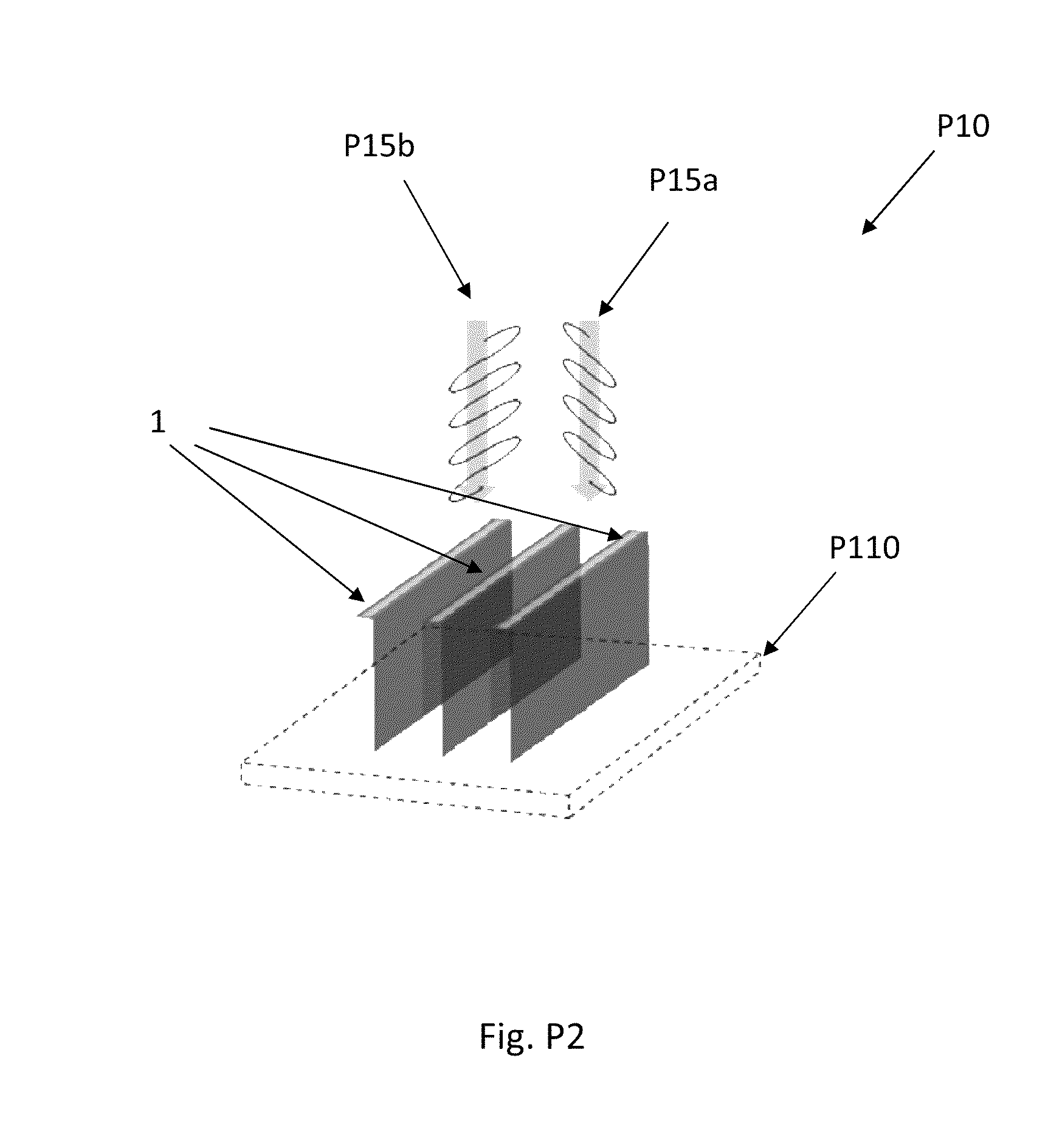

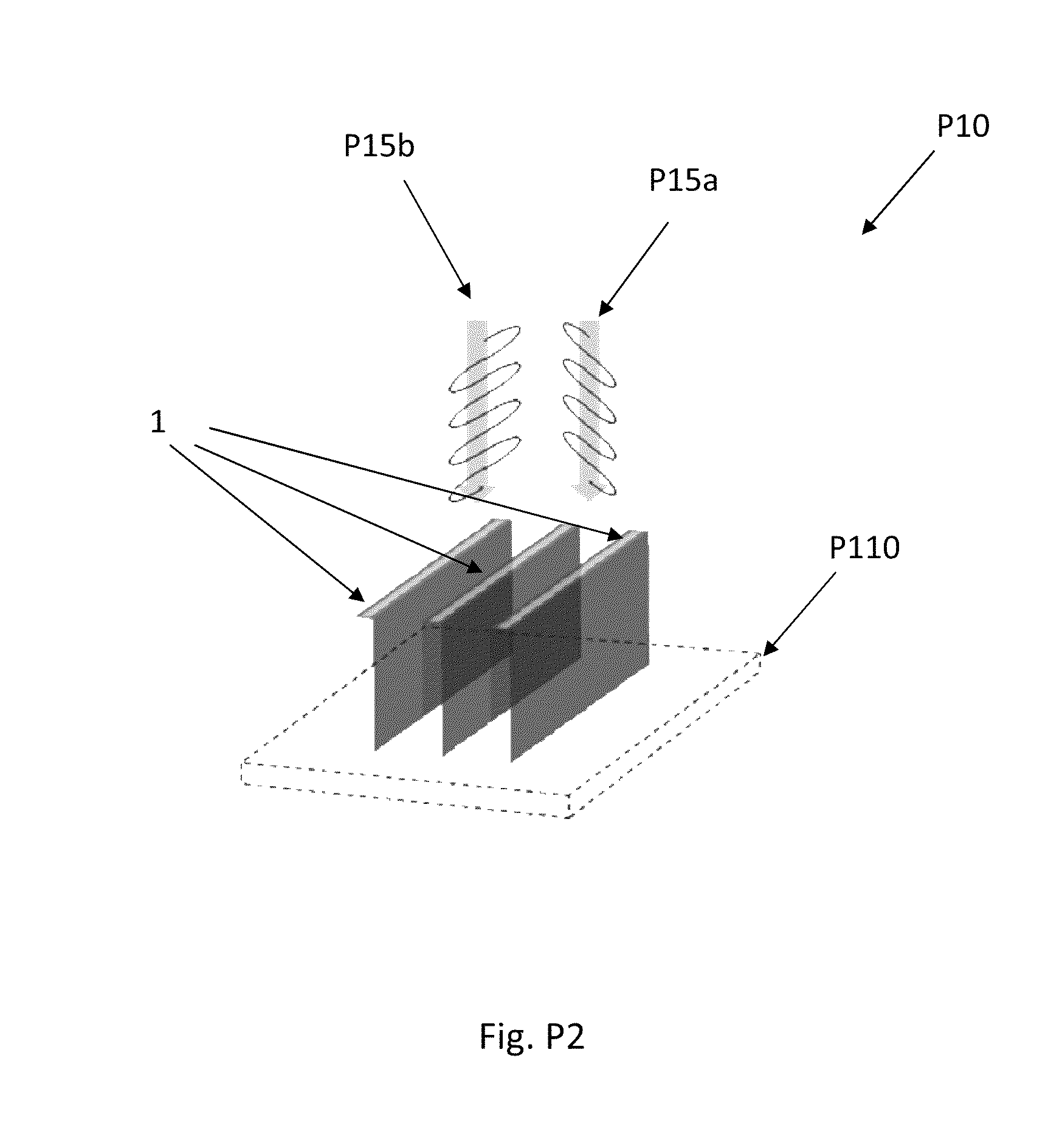

[0014] FIG. P2 shows a schematic of nanostructures in one subpixel when light with different polarization impinges thereon.

[0015] FIG. P12 shows a top view and a perspective view of a nanostructure in the device of FIG. P1, wherein the feature has metal layers on its sidewalls.

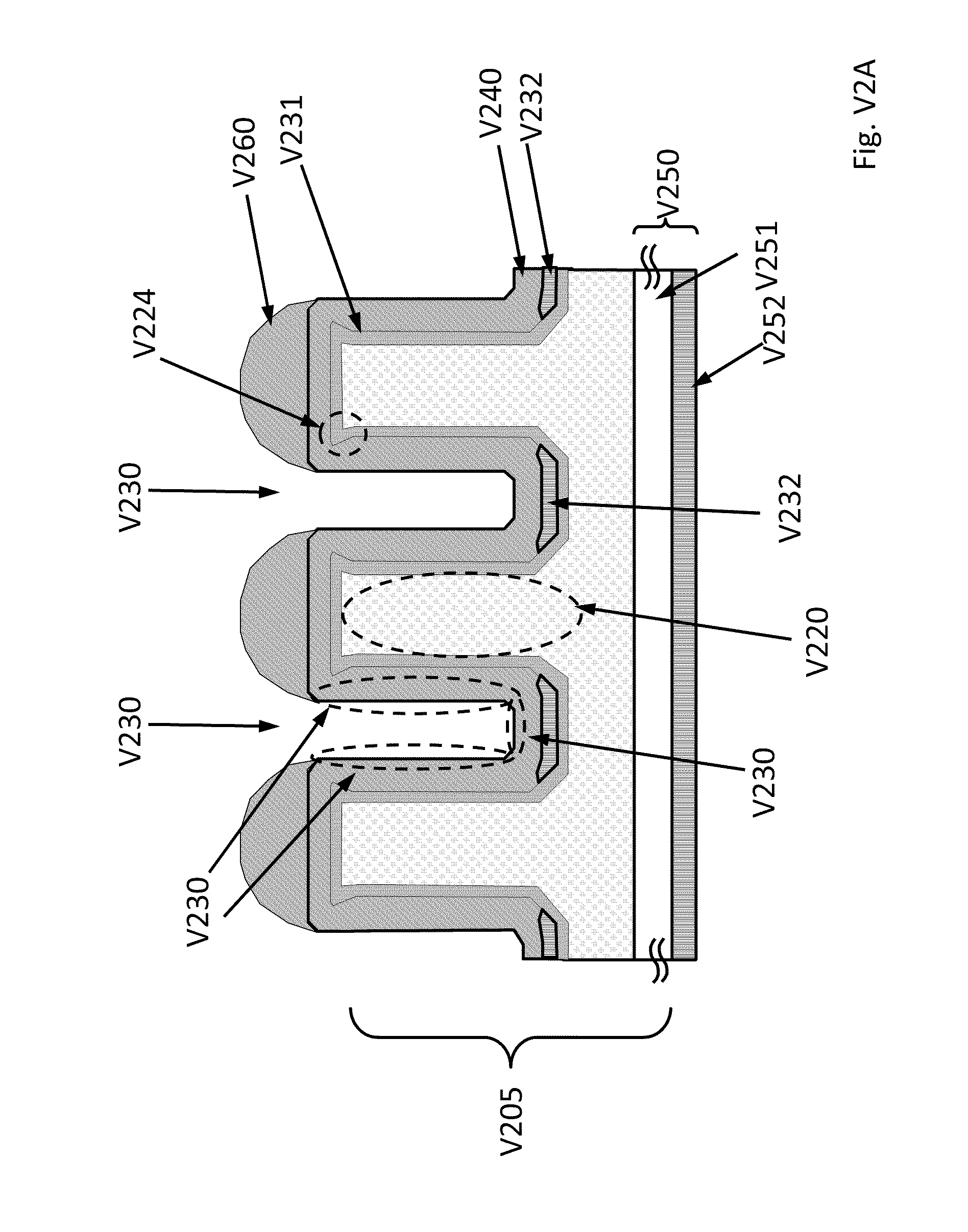

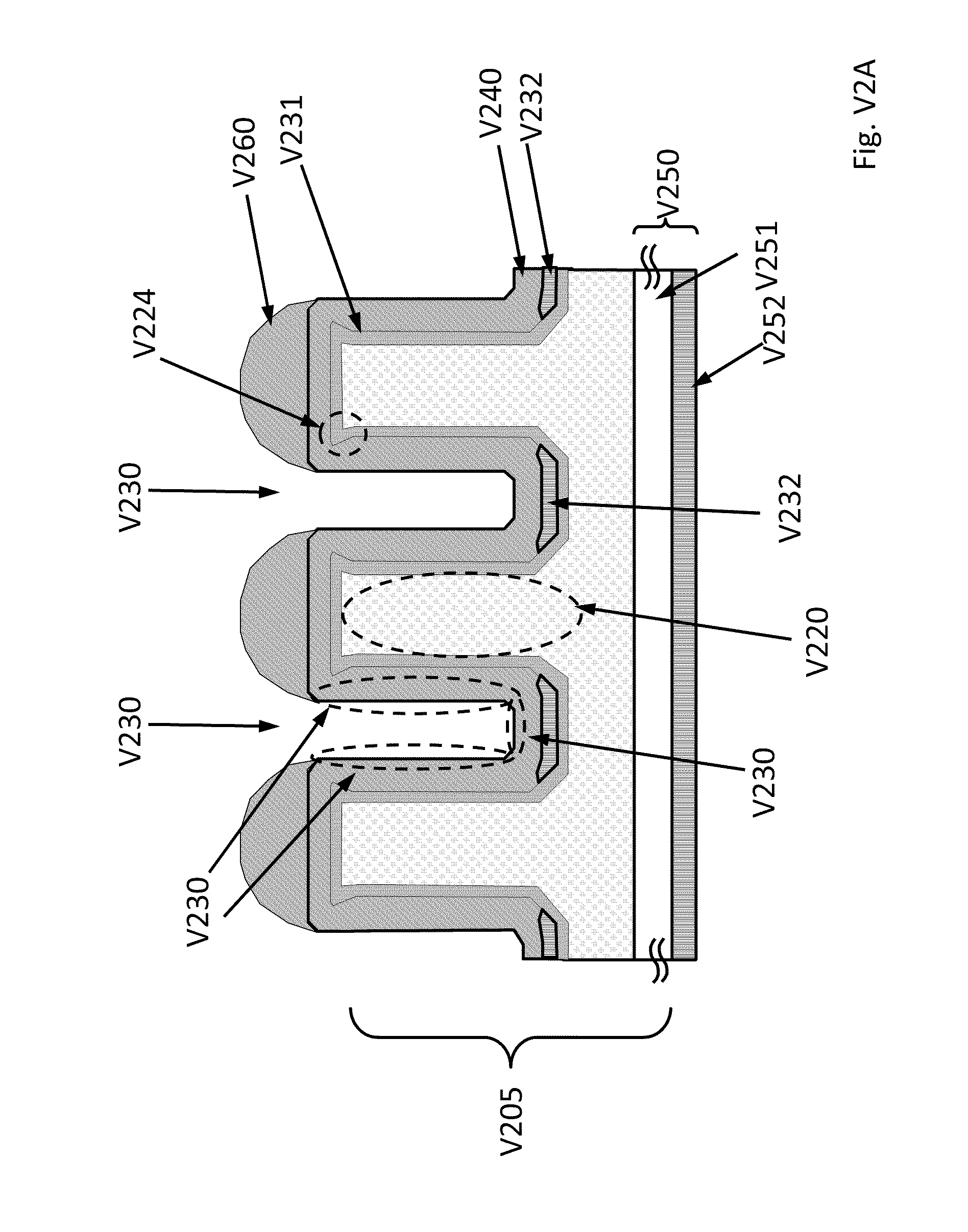

[0016] FIG. V2A is a schematic cross sectional view of a photovoltaic device according to an embodiment.

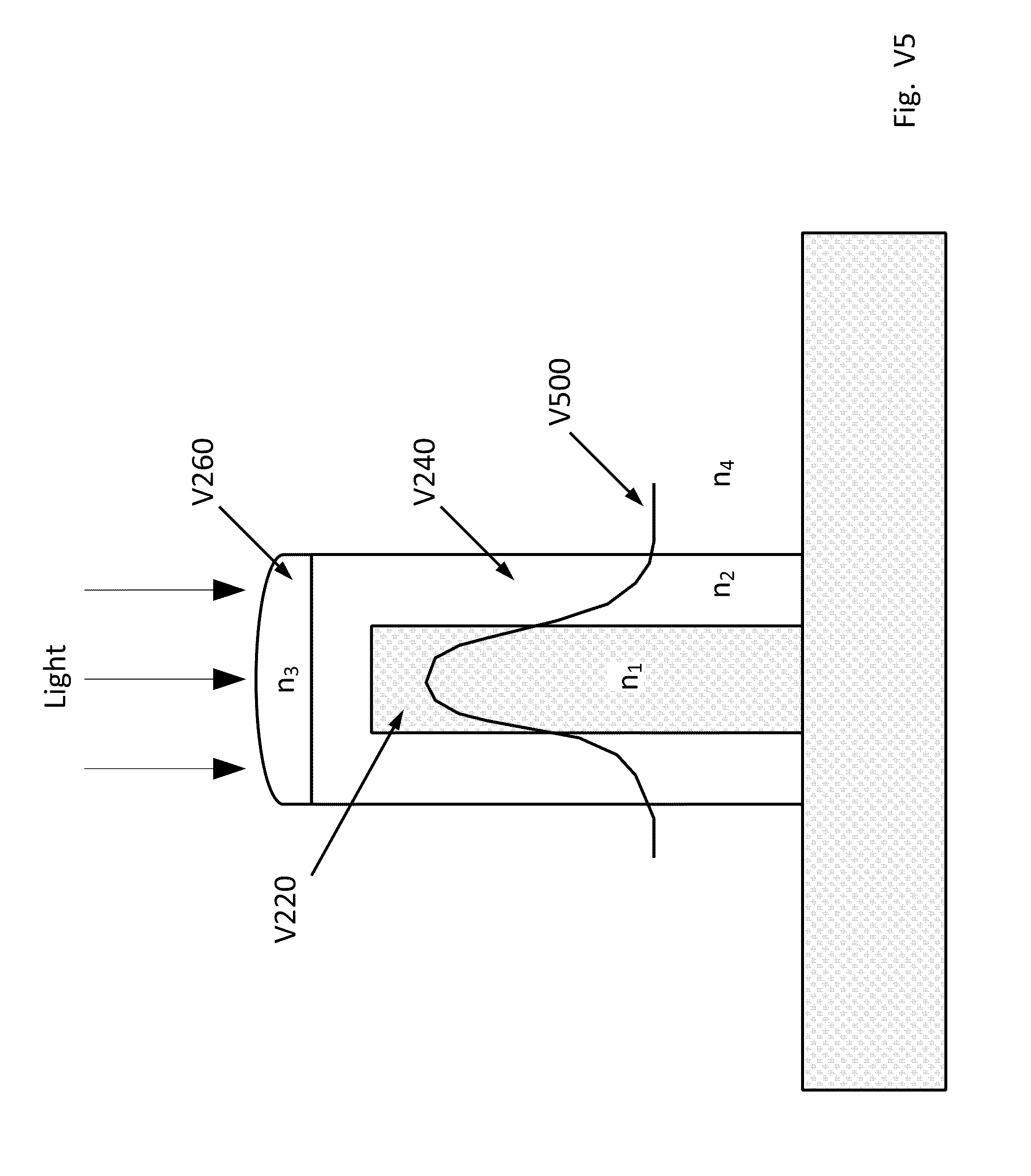

[0017] FIG. V5 shows a schematic of light concentration in the structures of the photovoltaic device.

[0018] FIG. V6 shows an exemplary top cross sectional view of the photovoltaic device.

[0019] FIG. V7 shows an exemplary perspective view of the photovoltaic device.

[0020] FIG. V8B shows schematics of drawing electrical current from the photovoltaic device of FIG. V2A.

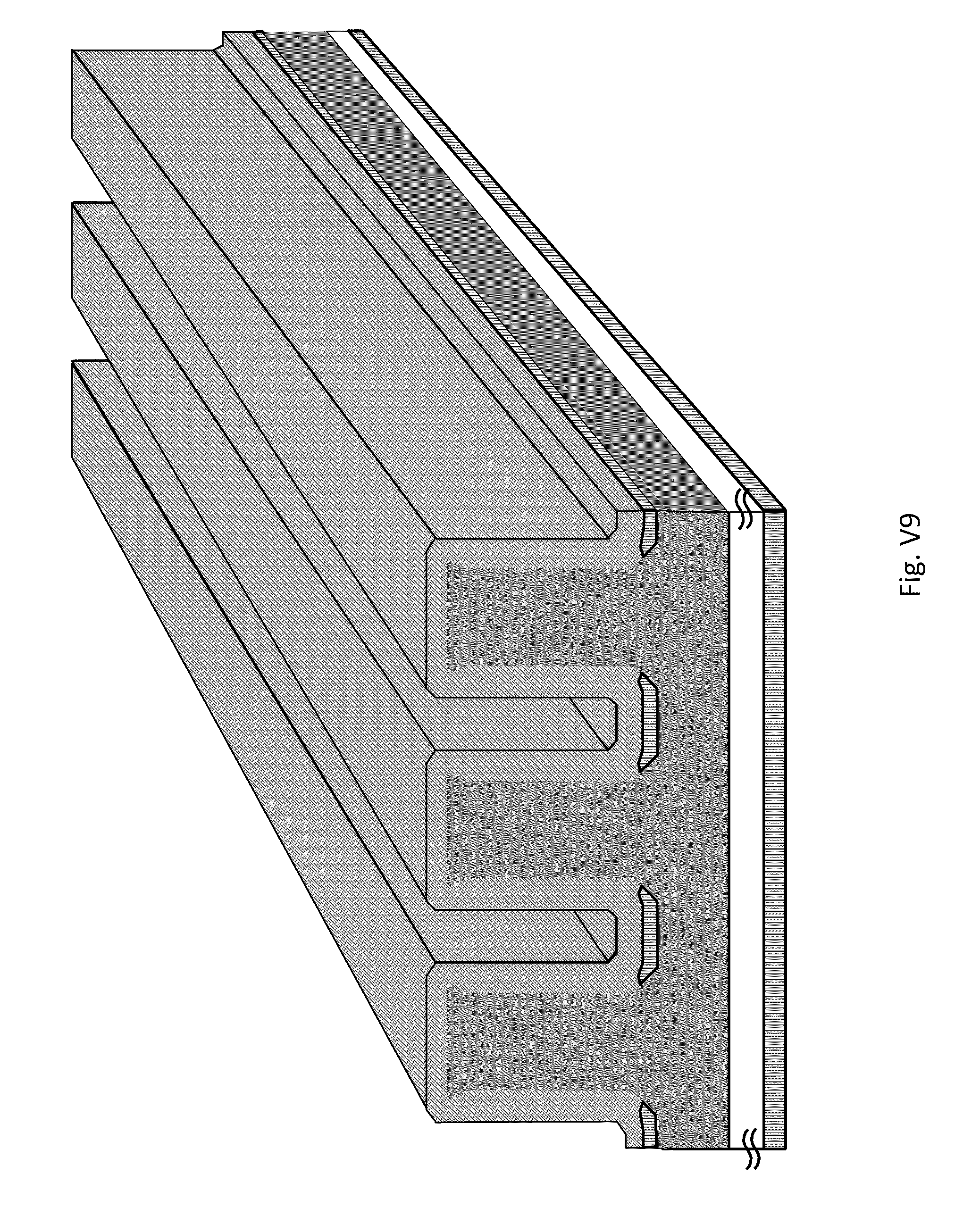

[0021] FIG. V9 shows an alternative stripe-shaped structures of the photovoltaic device.

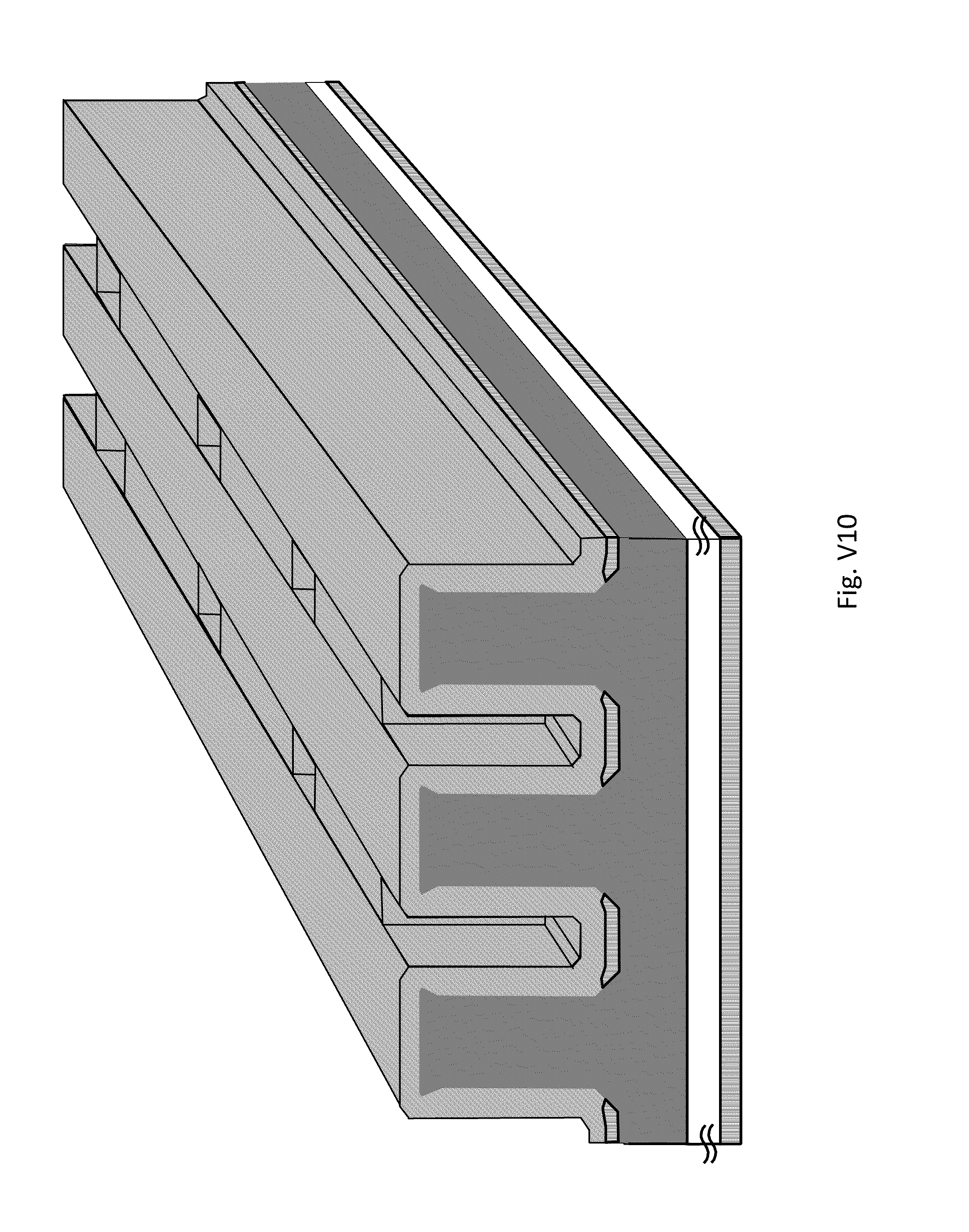

[0022] FIG. V10 shows an alternative mesh-shaped structures of the photovoltaic device.

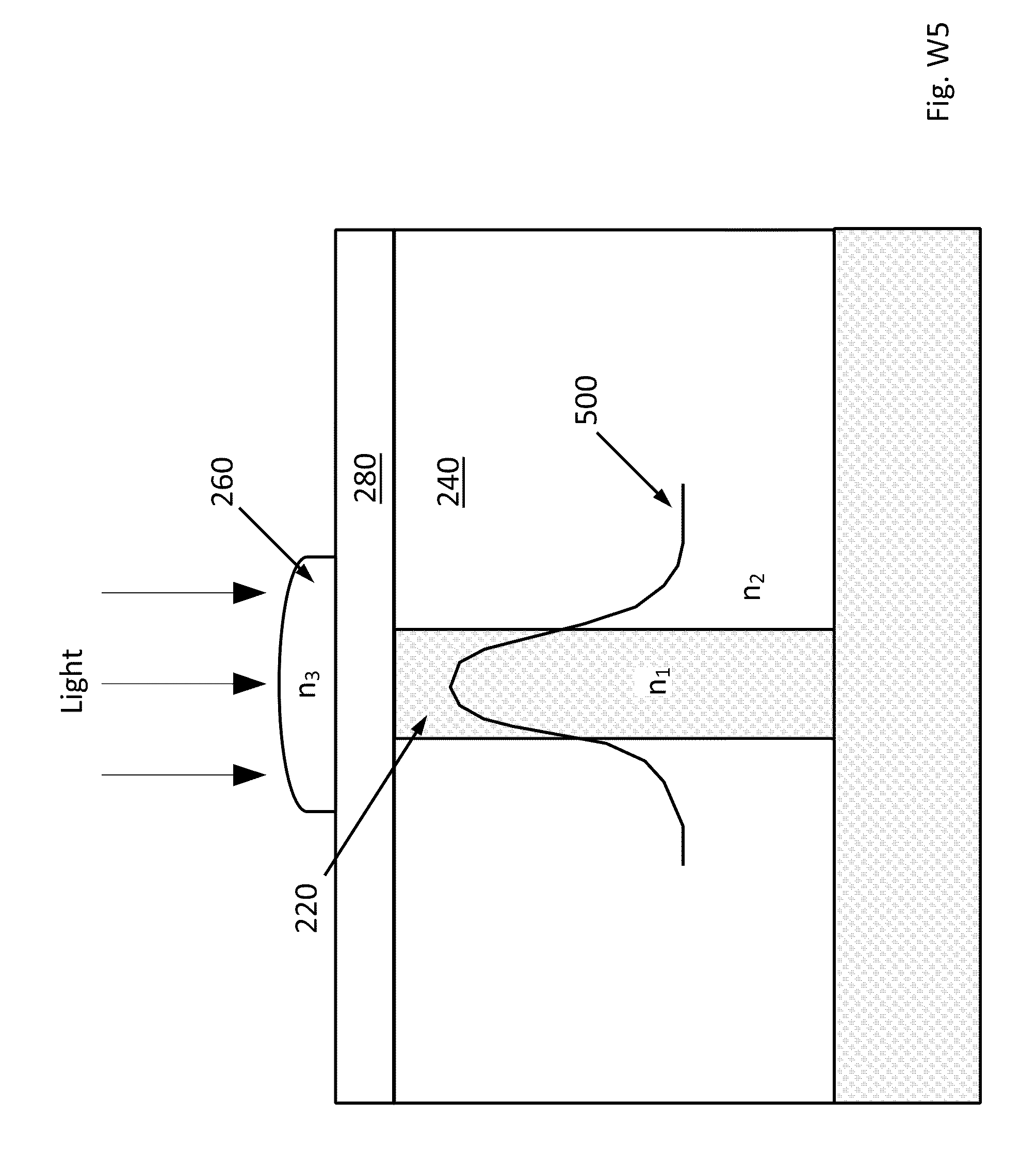

[0023] FIG. W2A is a schematic cross sectional view of a photovoltaic device according to an embodiment.

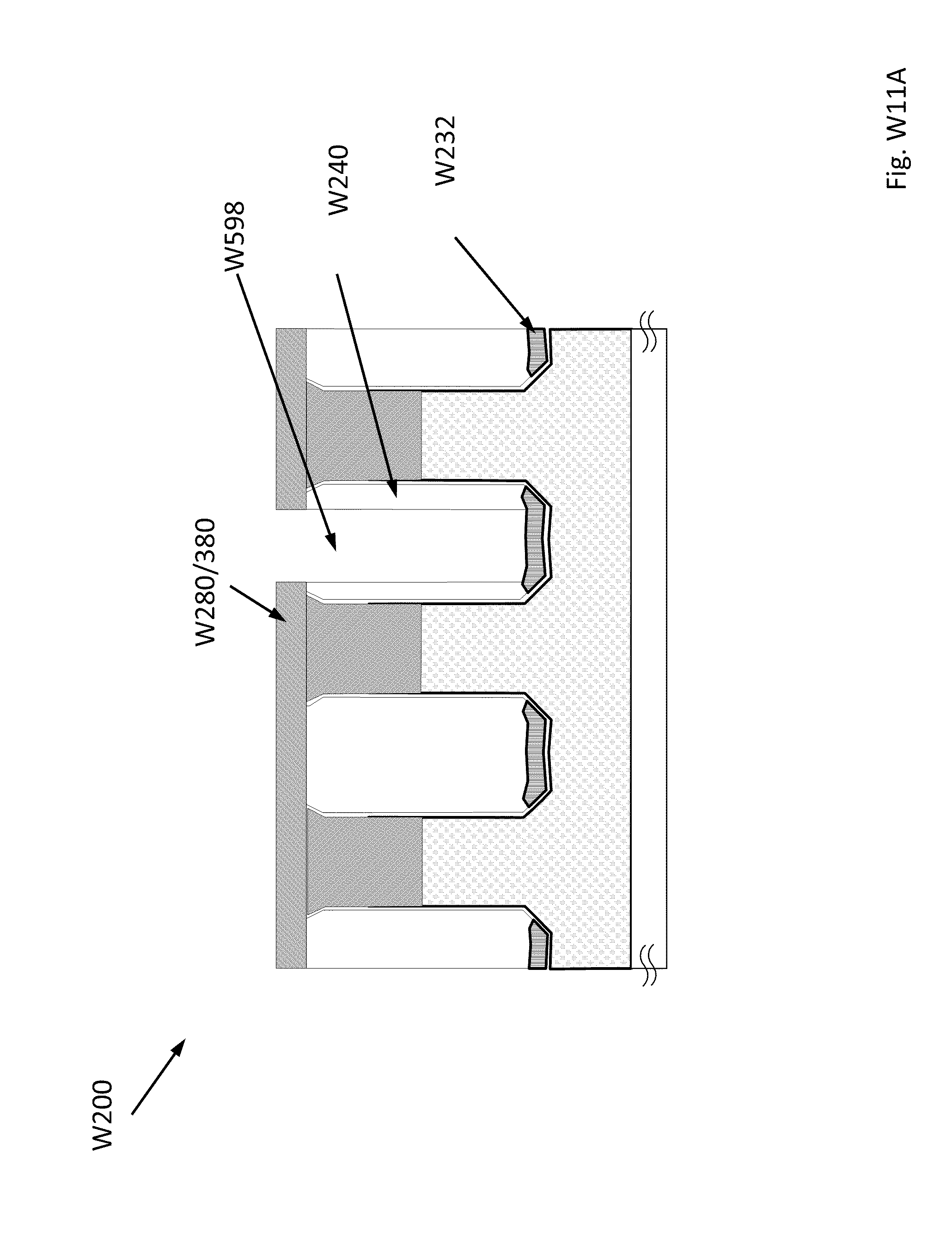

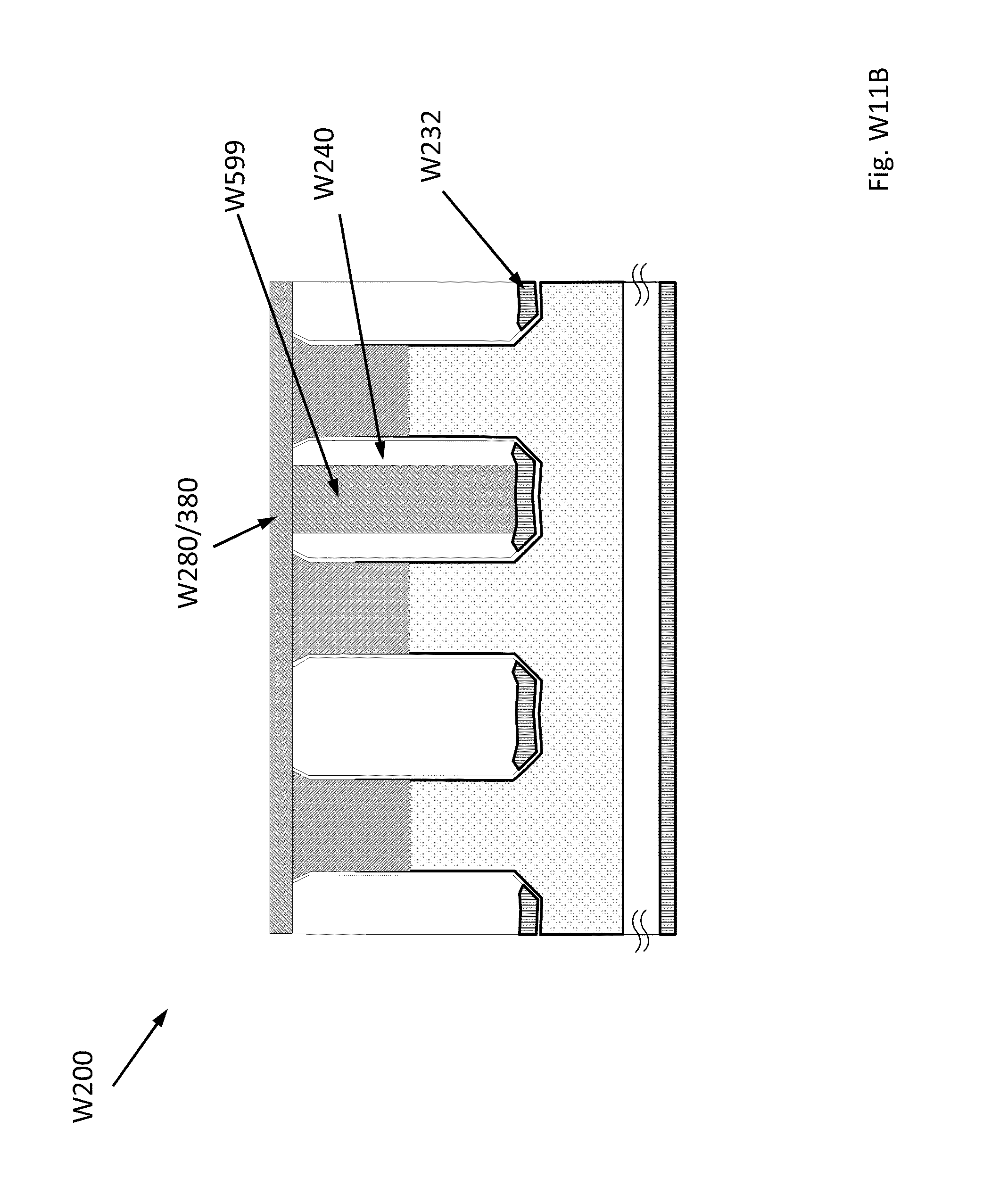

[0024] FIGS. W11A and WFIG. 11B show a process of making vias.

[0025] FIG. W12A and FIG. W12B show top views of exemplary vias.

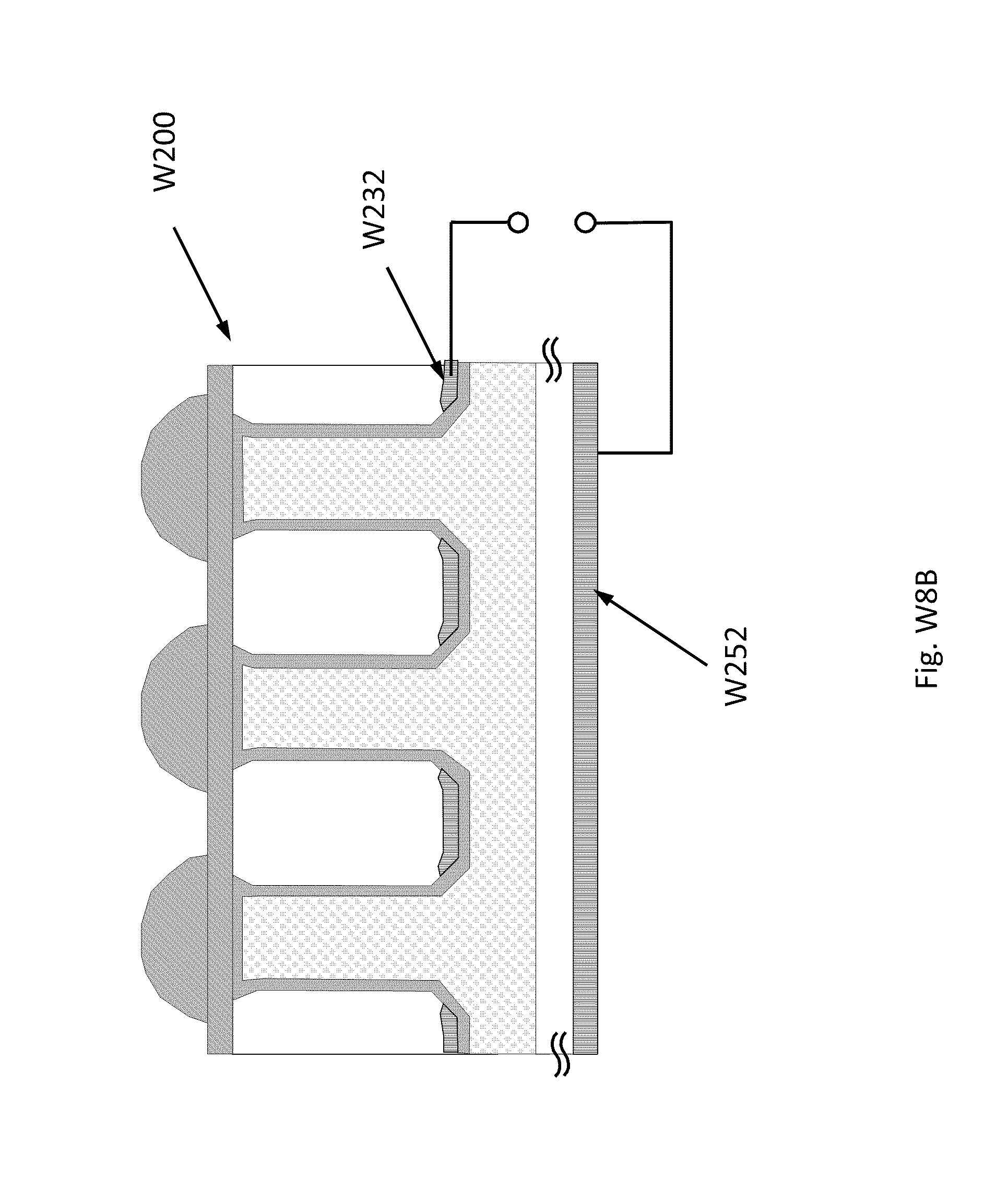

[0026] FIG. W8B shows schematics of drawing electrical current from the photovoltaic device of FIG. W2A.

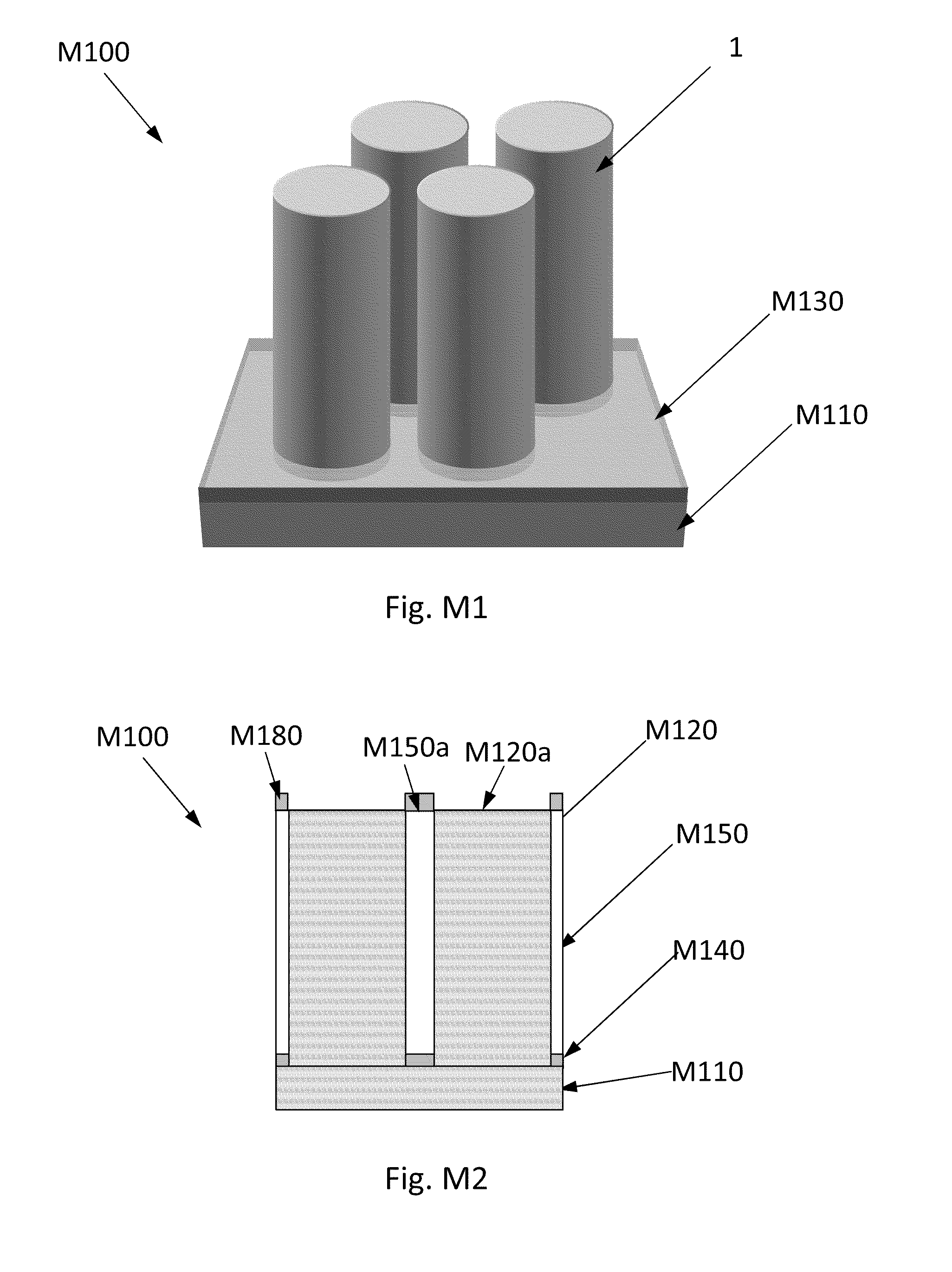

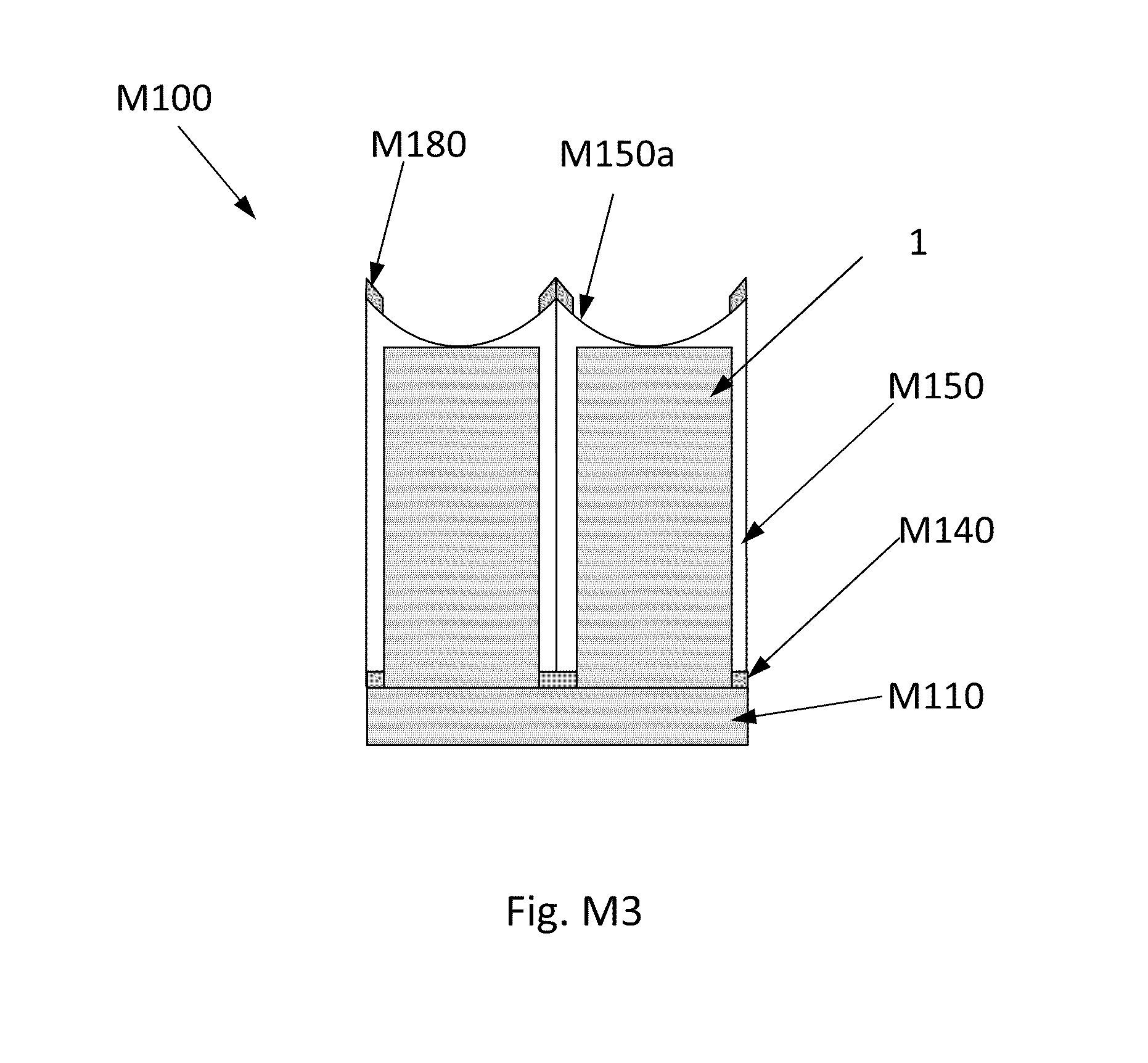

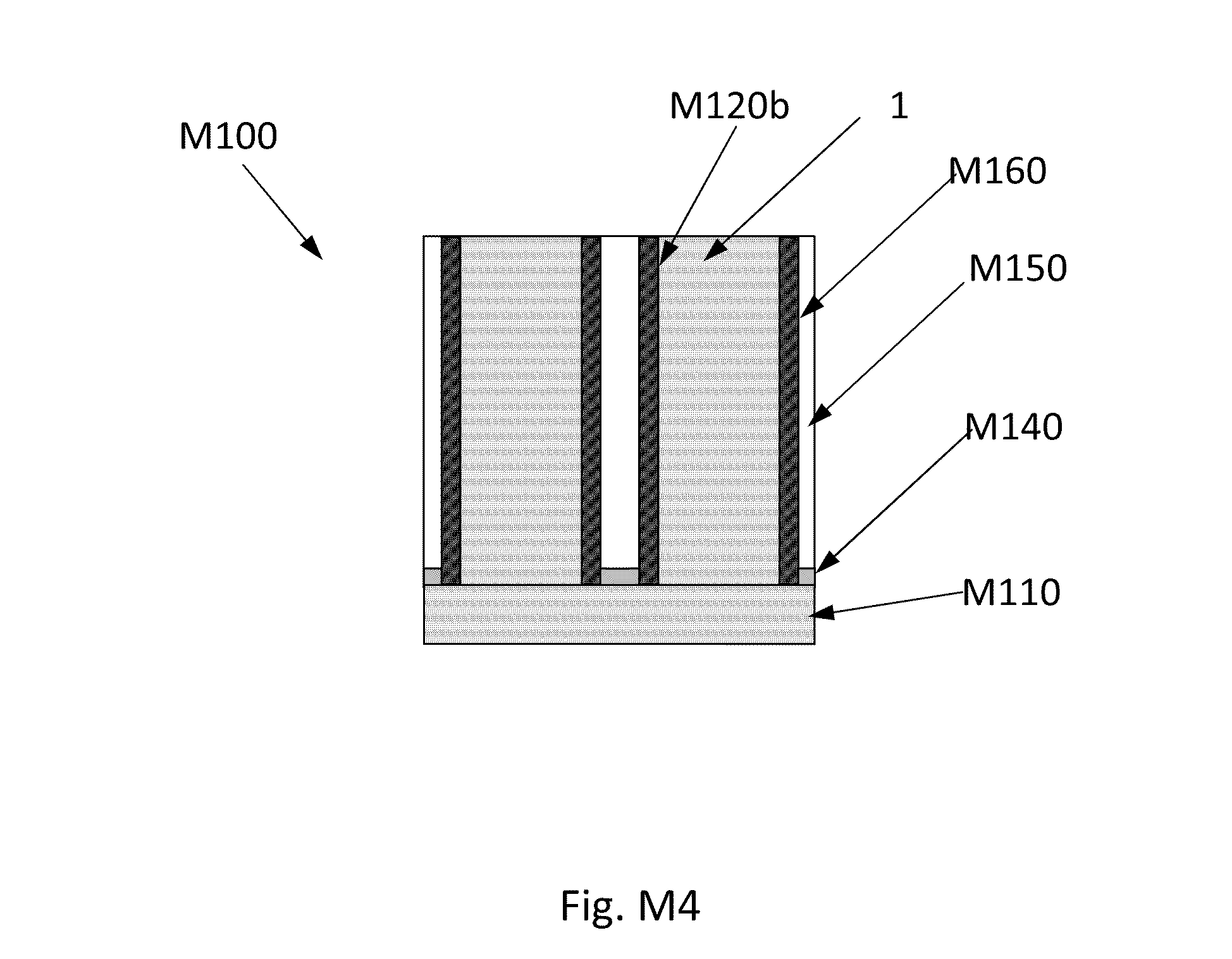

[0027] FIG. M1 shows a schematic perspective view of an array of nanostructures, according to an embodiment.

[0028] FIG. M2 shows a schematic cross-sectional view of the array of nanostructures of FIG. M1, according to an embodiment.

[0029] FIG. M3 shows an alternative schematic cross-sectional view of the array of nanostructures of FIG. M1, according to an embodiment.

[0030] FIG. M4 shows yet another schematic cross-sectional view of the array of nanostructures of FIG. M1, according to an embodiment.

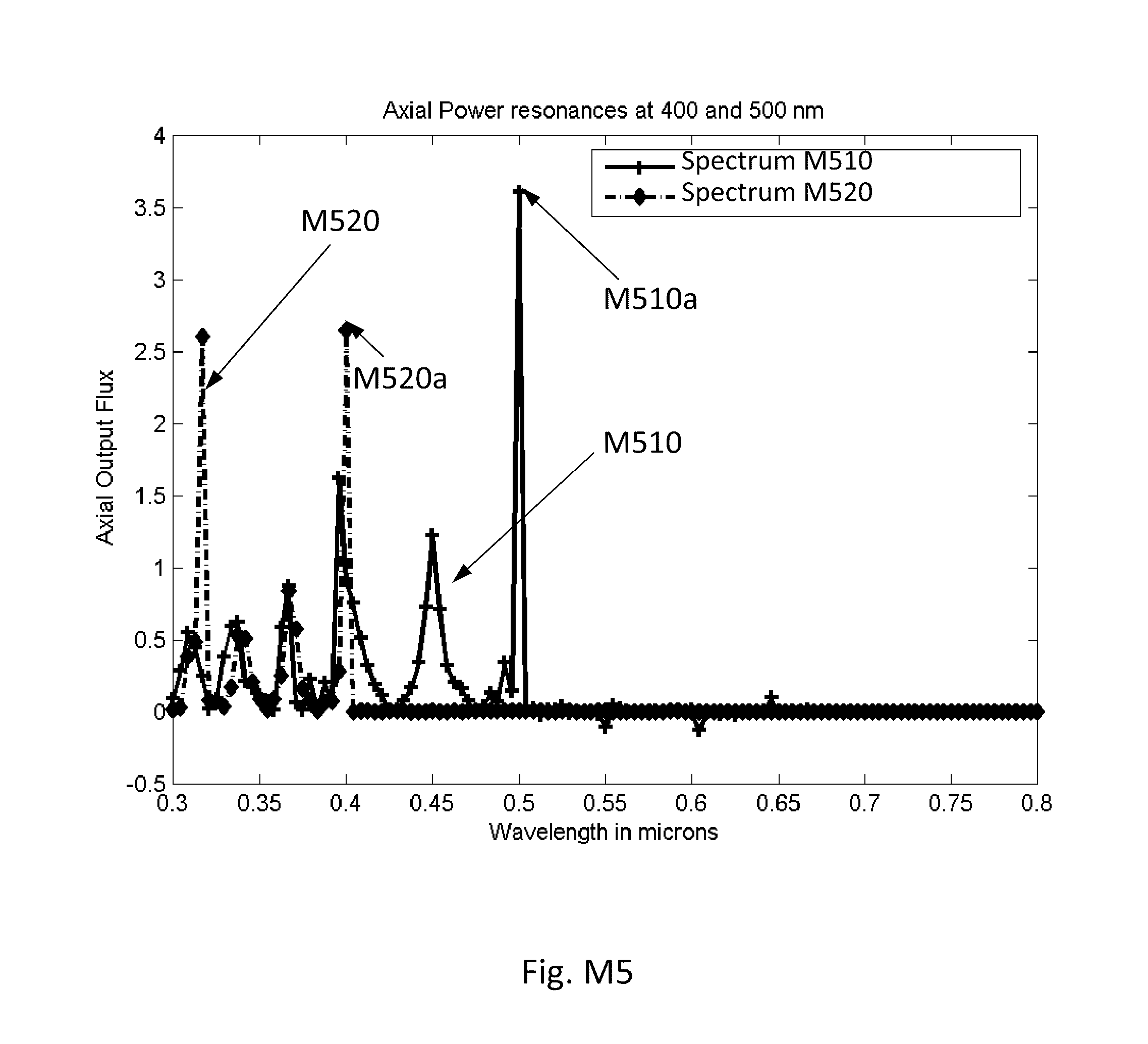

[0031] FIG. M5 shows simulated fluorescence spectra of two exemplary arrays of nanostructures in axial directions thereof.

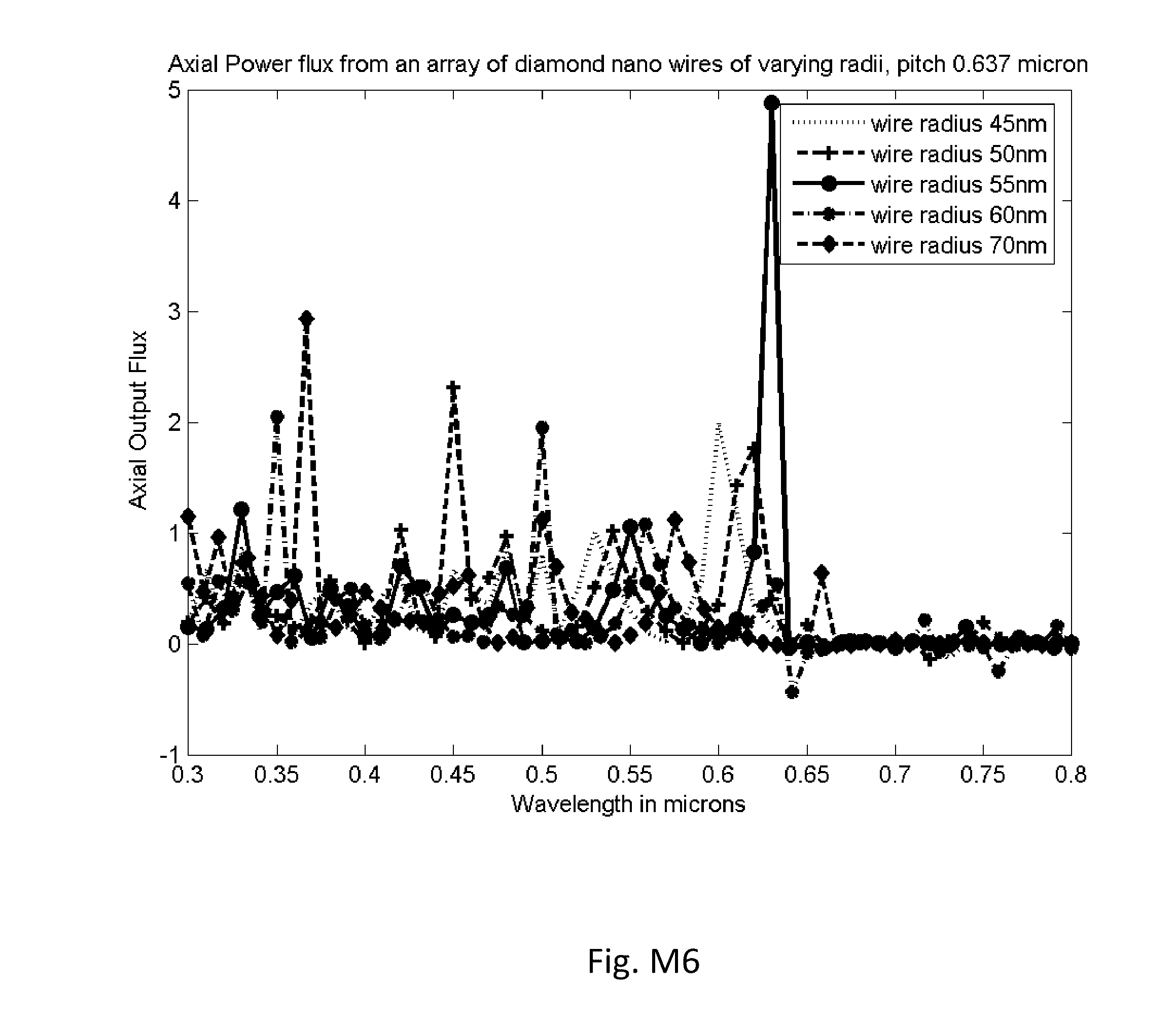

[0032] FIG. M6 shows simulated fluorescence spectra of several exemplary arrays of nanostructures in axial directions thereof, all of which have a same pitch of 637 nm and different radii.

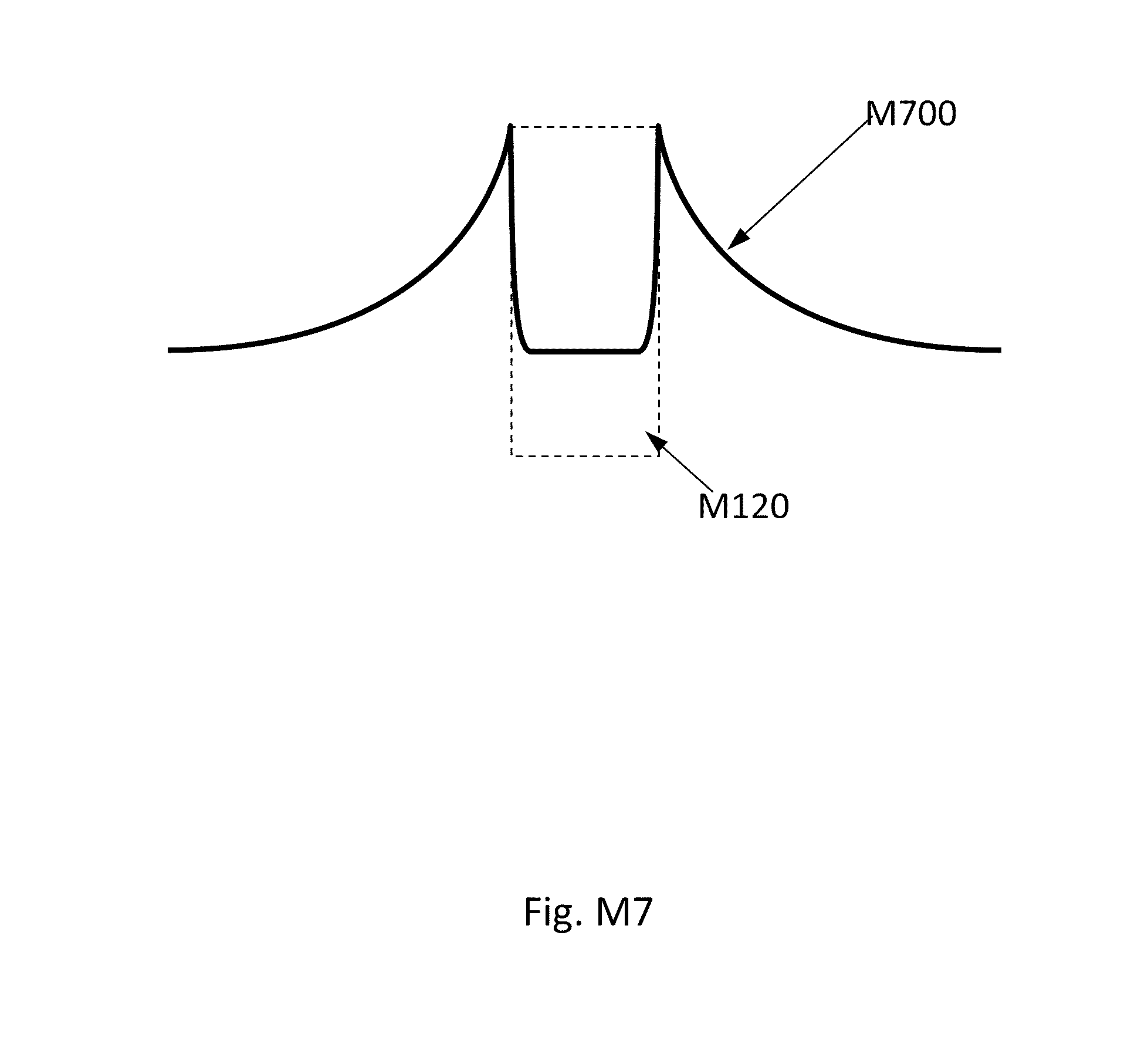

[0033] FIG. M7 shows a schematic light distribution of an air mode of the array of nanostructures.

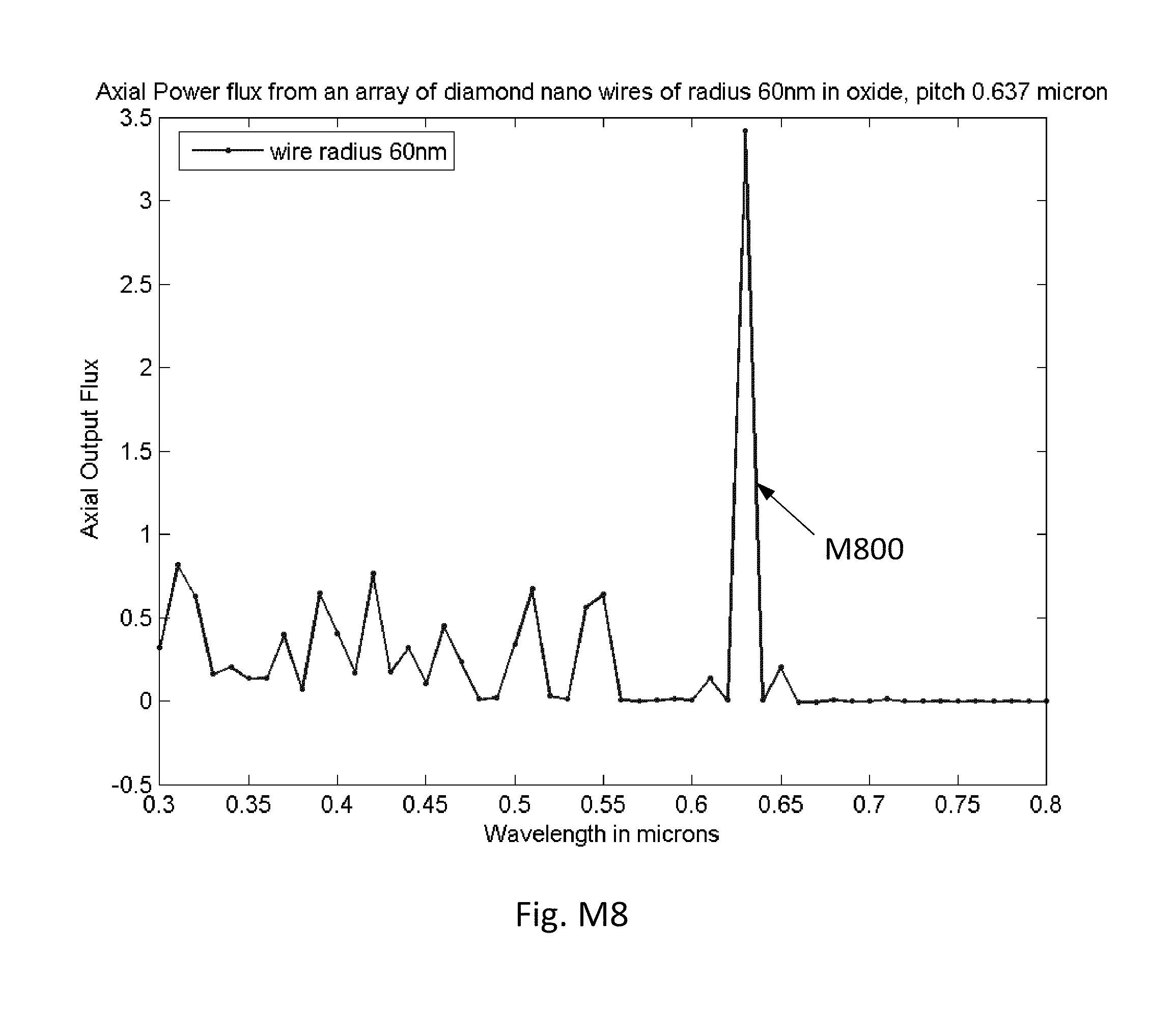

[0034] FIG. M8 shows a simulated fluorescence spectrum of an exemplary array of nanostructures in axial directions thereof, wherein the fluorescent nanostructures are embedded in oxide.

[0035] FIG. M9 shows a simulated fluorescence spectrum of an exemplary array of nanostructures in axial directions thereof, wherein the fluorescent nanostructures have a cladding layer.

[0036] FIG. M10 shows a simulated fluorescence spectrum of an exemplary array of nanostructures in axial directions thereof, wherein the fluorescent nanostructures have a cladding layer and wherein the array of nanostructures of FIG. M10 has dimensions to scale with the array of nanostructures of FIG. M9 and a peak position at 637 nm.

[0037] FIGS. S4 and S5 show an apparatus comprising the image sensor, according to an embodiment.

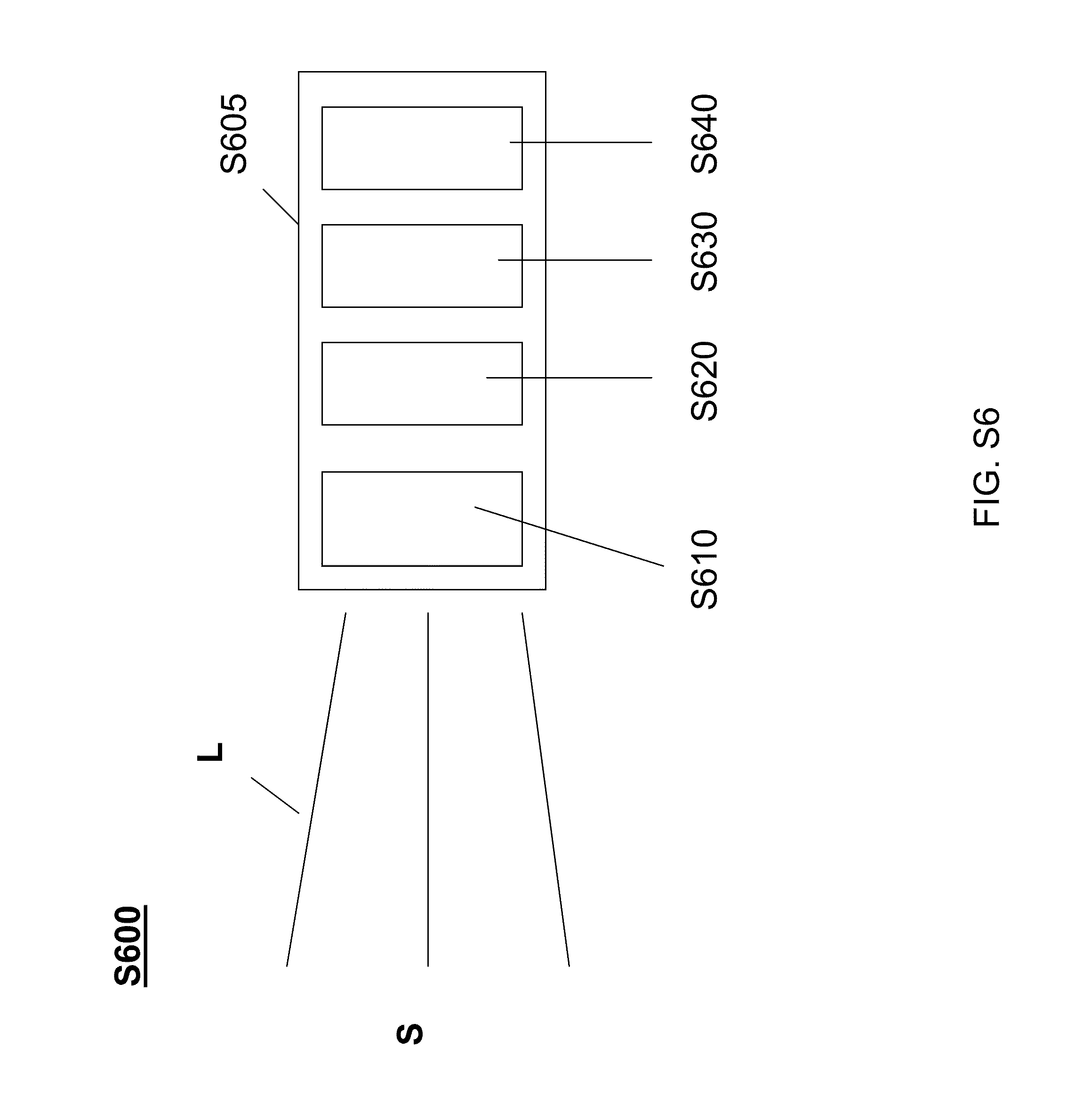

[0038] FIG. S6 shows another apparatus comprising the image sensor, according to an embodiment.

[0039] FIGS. S7A and S7B show schematics of a pixel of the image sensor, the pixel having more than one nanopillar sized to absorb and/or detect light of different wavelength or color, according to embodiments.

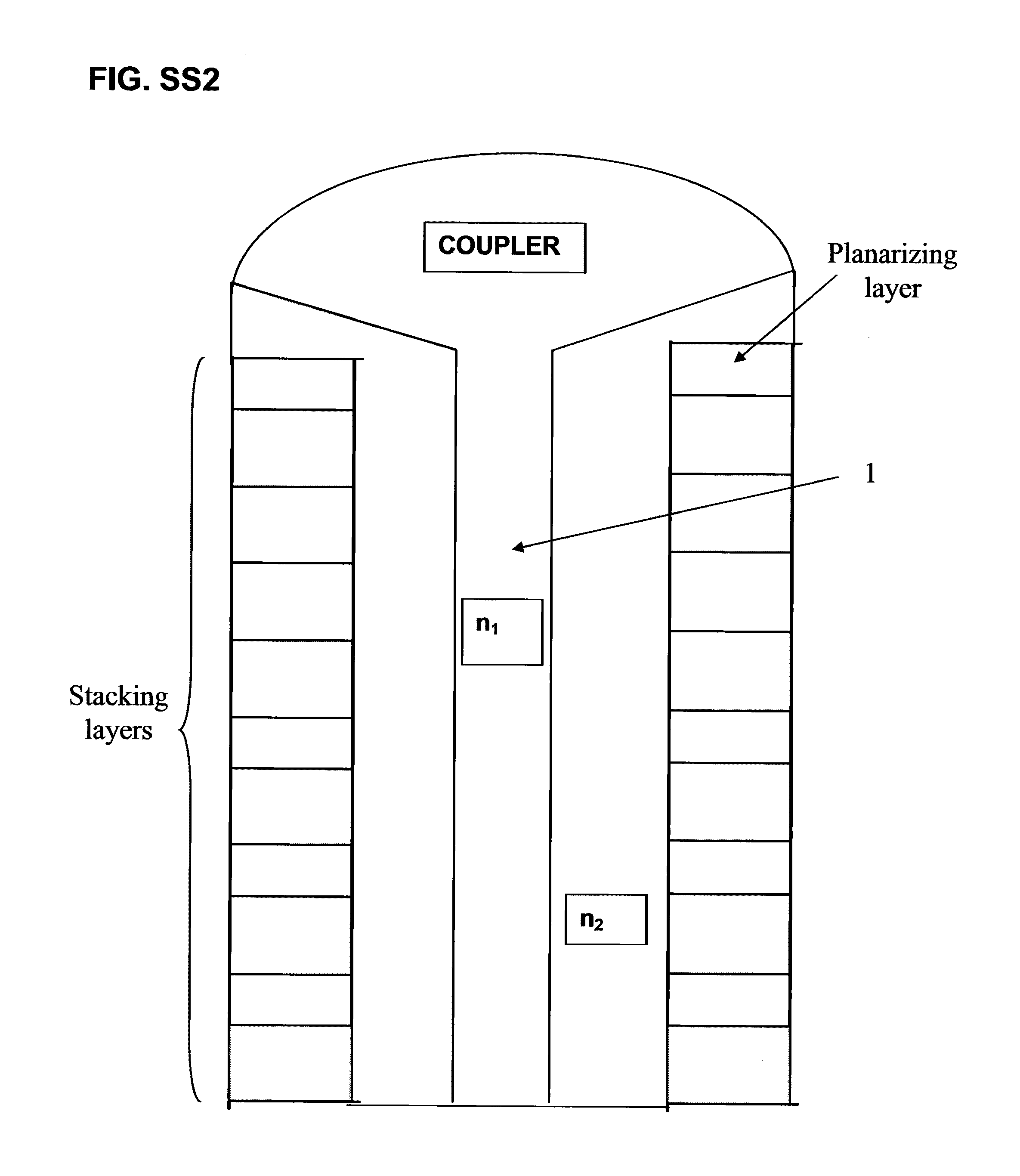

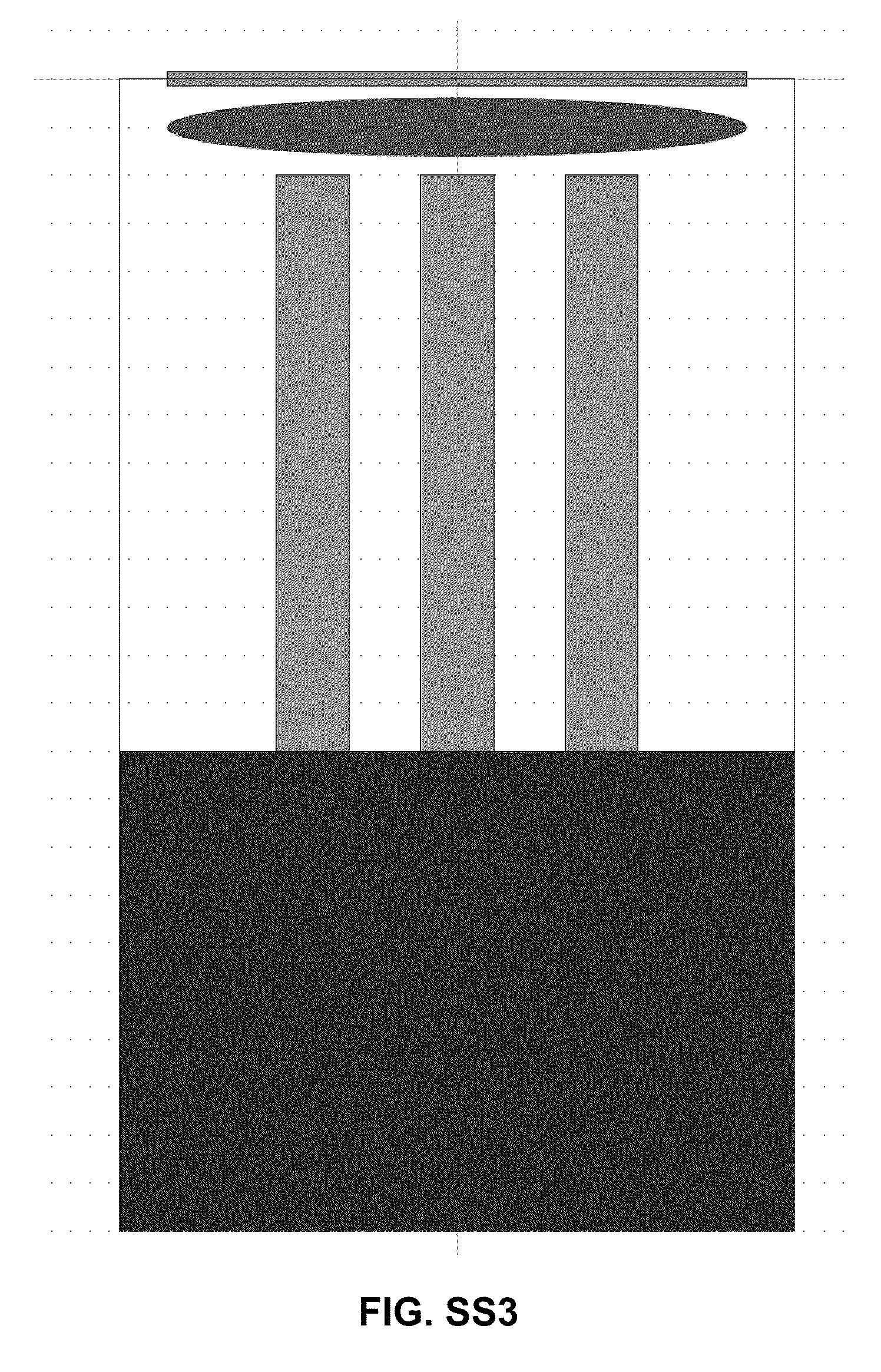

[0040] FIG. SS2 shows a cross sectional view of an embodiment of an image sensor having a microlens.

[0041] FIG. SS3 shows an embodiment of an array of nanowires within a single cavity of the image sensor of an embodiment.

[0042] FIG. SS4 shows a schematic of a top view of a device containing image sensors of the embodiments disclosed herein, each image sensor having two outputs representing the complementary colors.

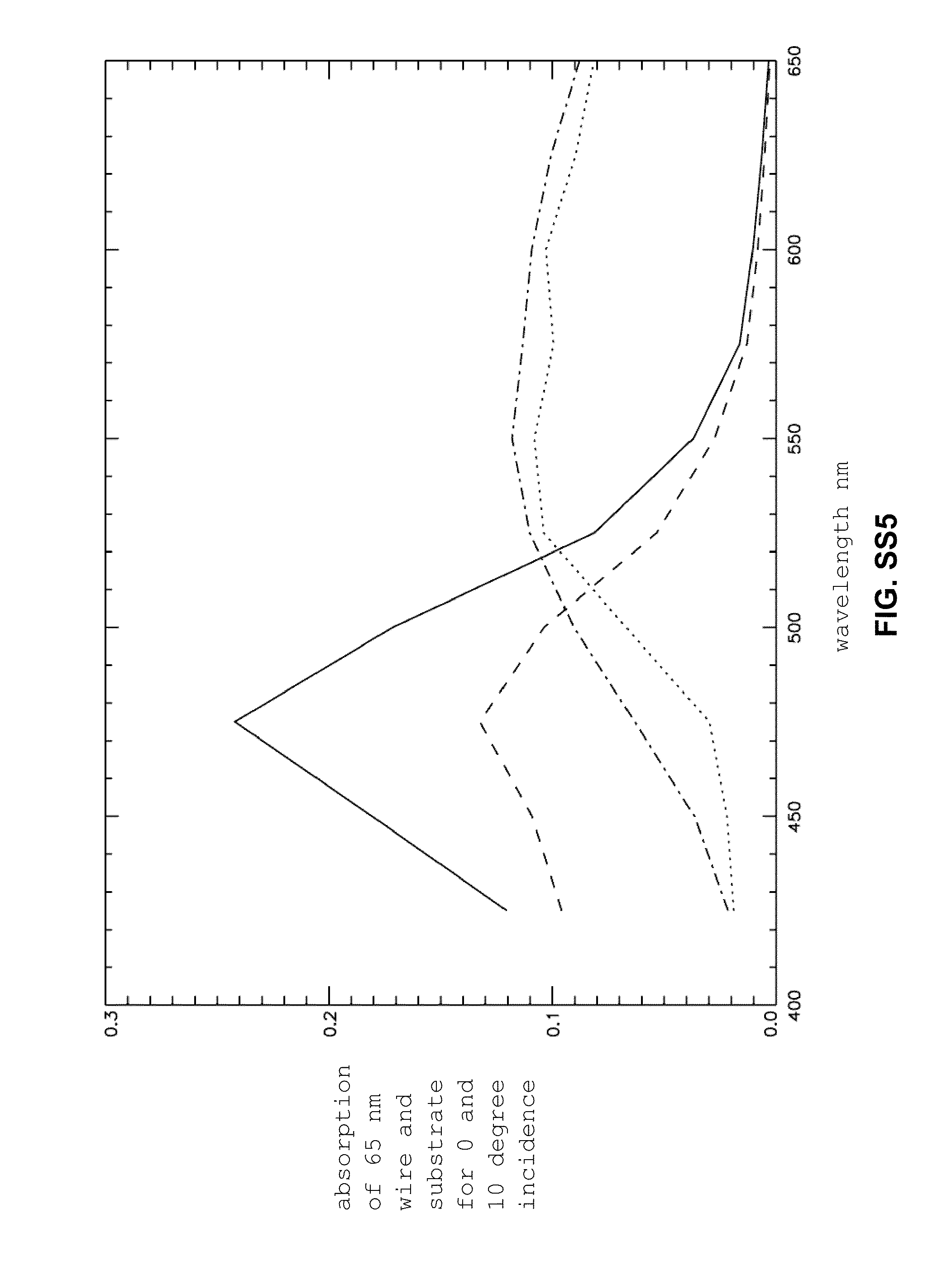

[0043] FIG. SS5 shows a response of the single wire of diameter 65 nm in a 1200 nm cavity as a function of wavelength with illumination incident at 0 and 10 degrees from the vertical.

[0044] FIG. SS6 shows a response of an array of 5 wires of diameter 60 nm in a 1200 nm cavity as a function of wavelength with illumination incident at 0 and 10 degrees from the vertical.

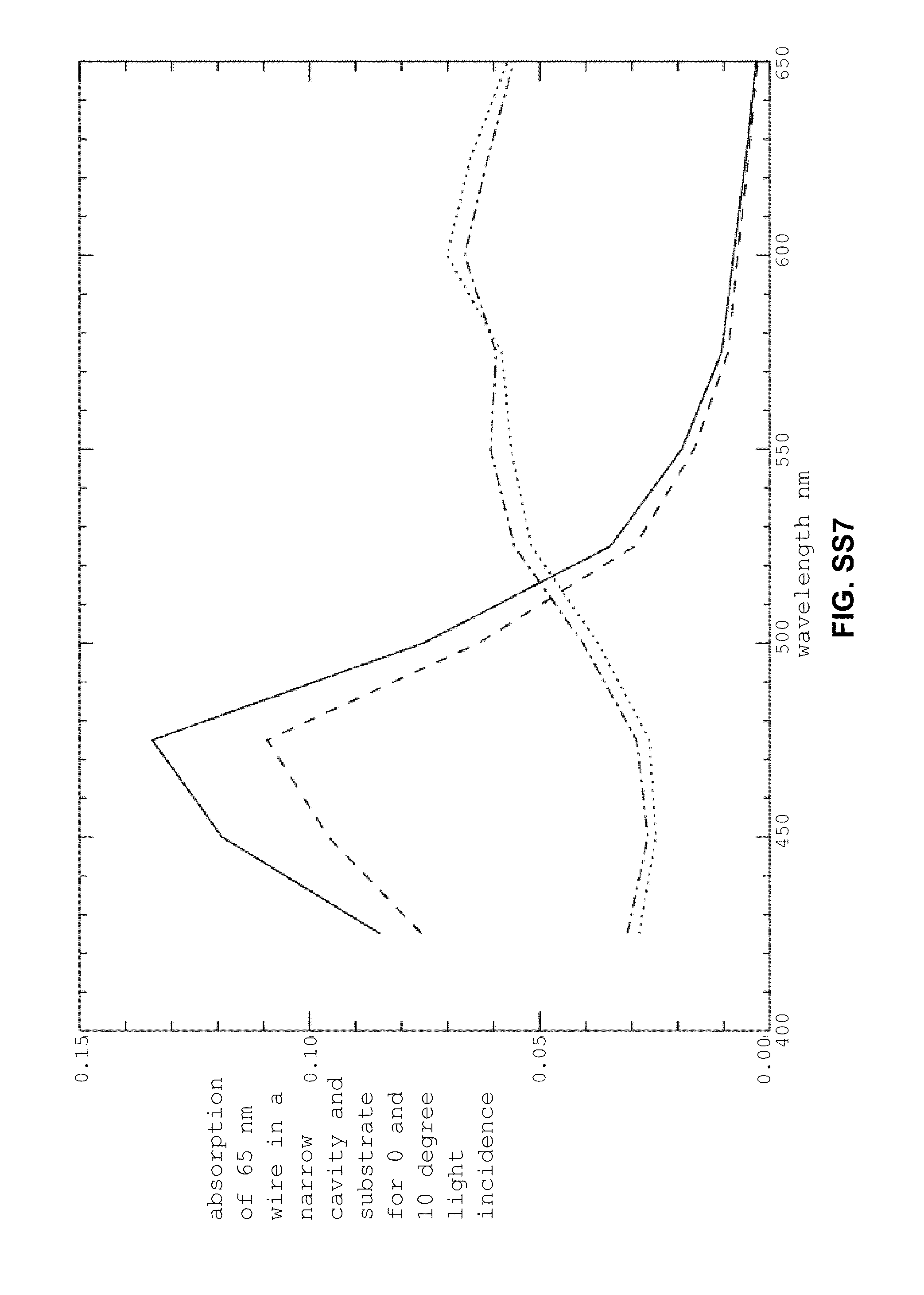

[0045] FIG. SS7 shows a response of the single wire of diameter 65 nm in a 600 nm cavity as a function of wavelength with illumination incident at 0 and 10 degrees from the vertical.

[0046] FIG. F1A shows a schematic cross-sectional view of an image sensor according to an embodiment.

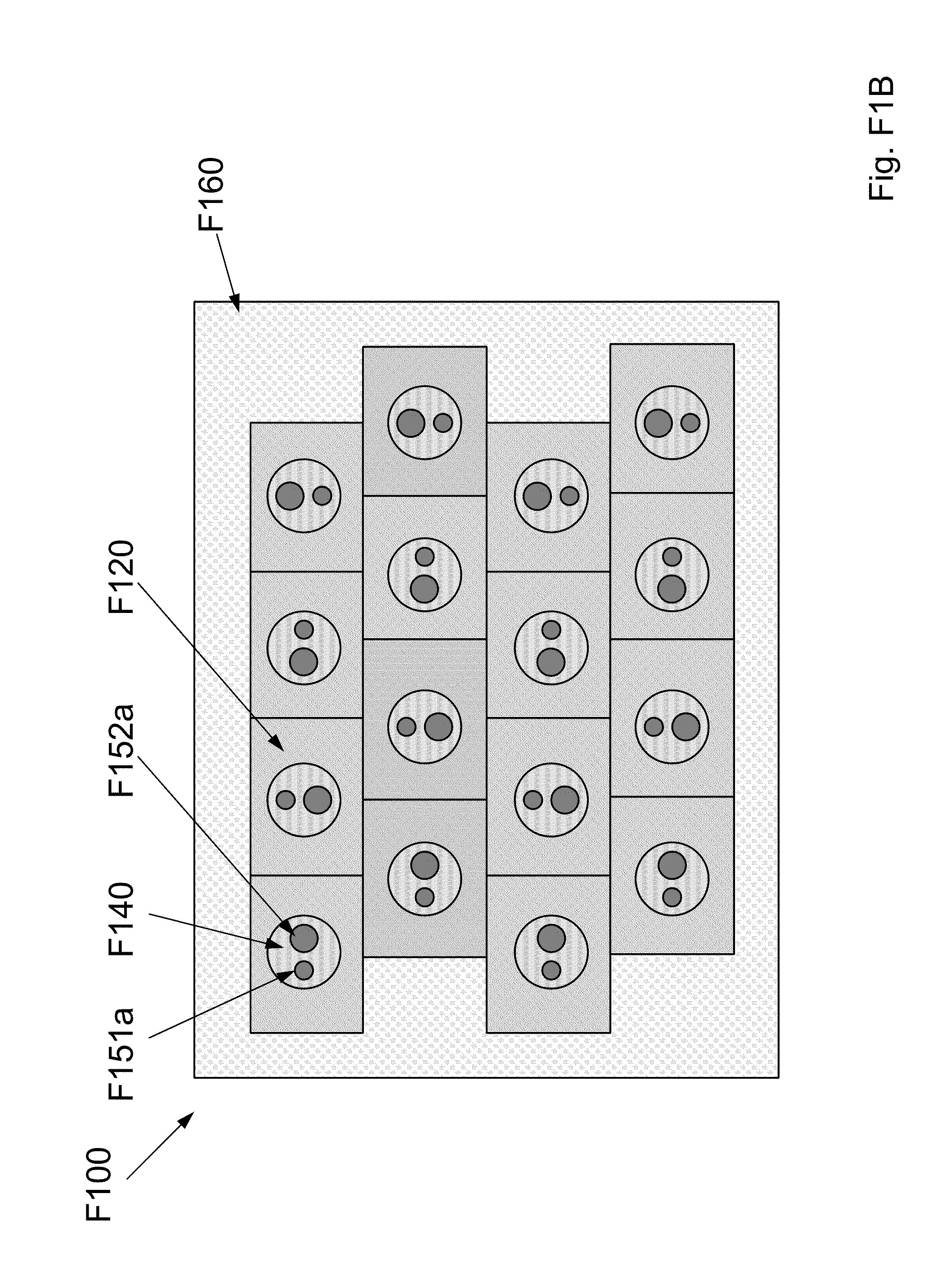

[0047] FIG. F1B shows a schematic top view of the image sensor of FIG. F1A.

[0048] FIG. F1C shows exemplary absorption spectra of two nanowires in two subpixels in a pixel of the image sensor of FIG. F1A and a photodiode on the substrate of the image sensor of FIG. F1A.

[0049] FIG. F2A shows a schematic cross-sectional view of an image sensor according to an embodiment.

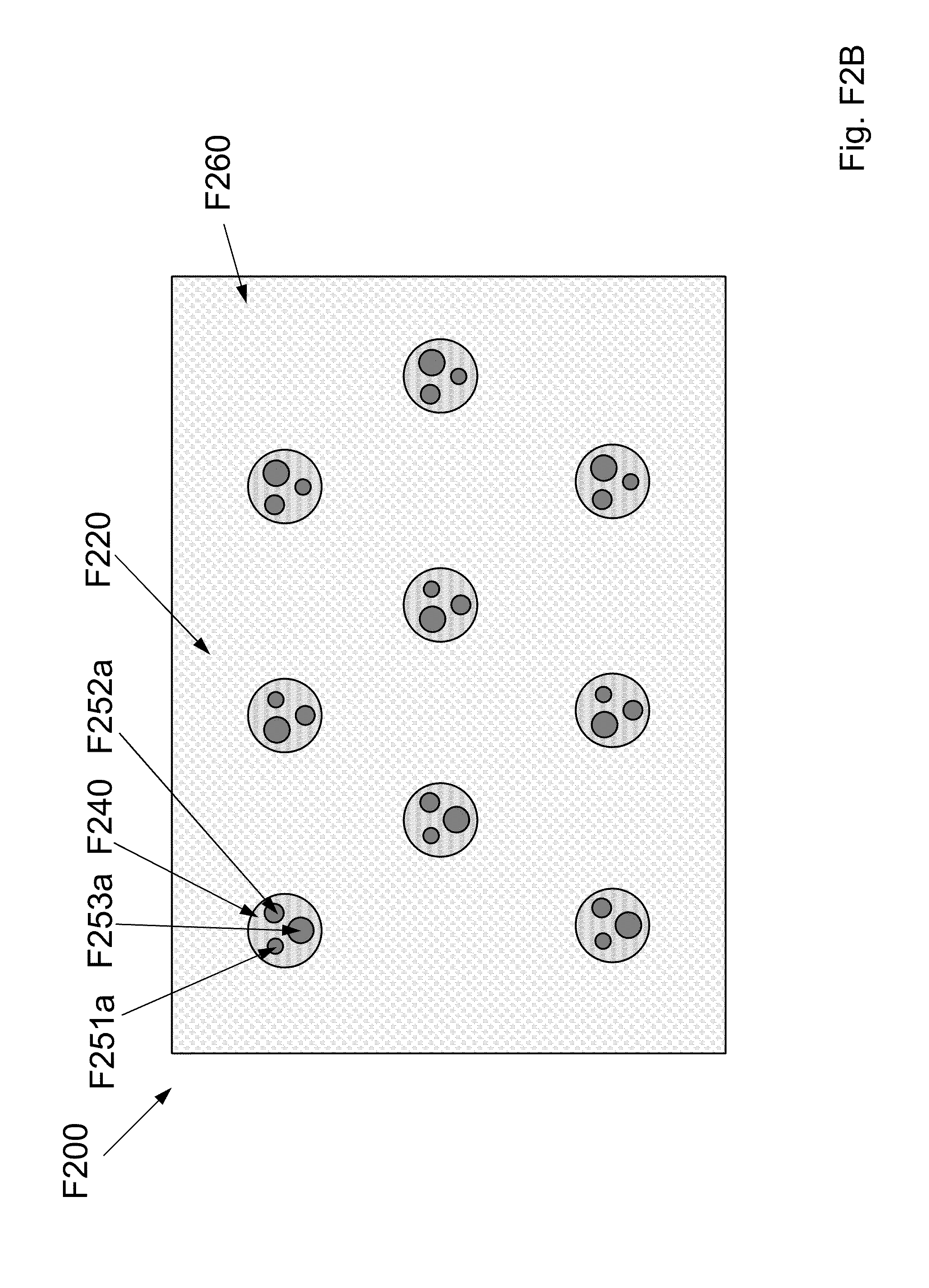

[0050] FIG. F2B shows a schematic top view of the image sensor of FIG. F2A.

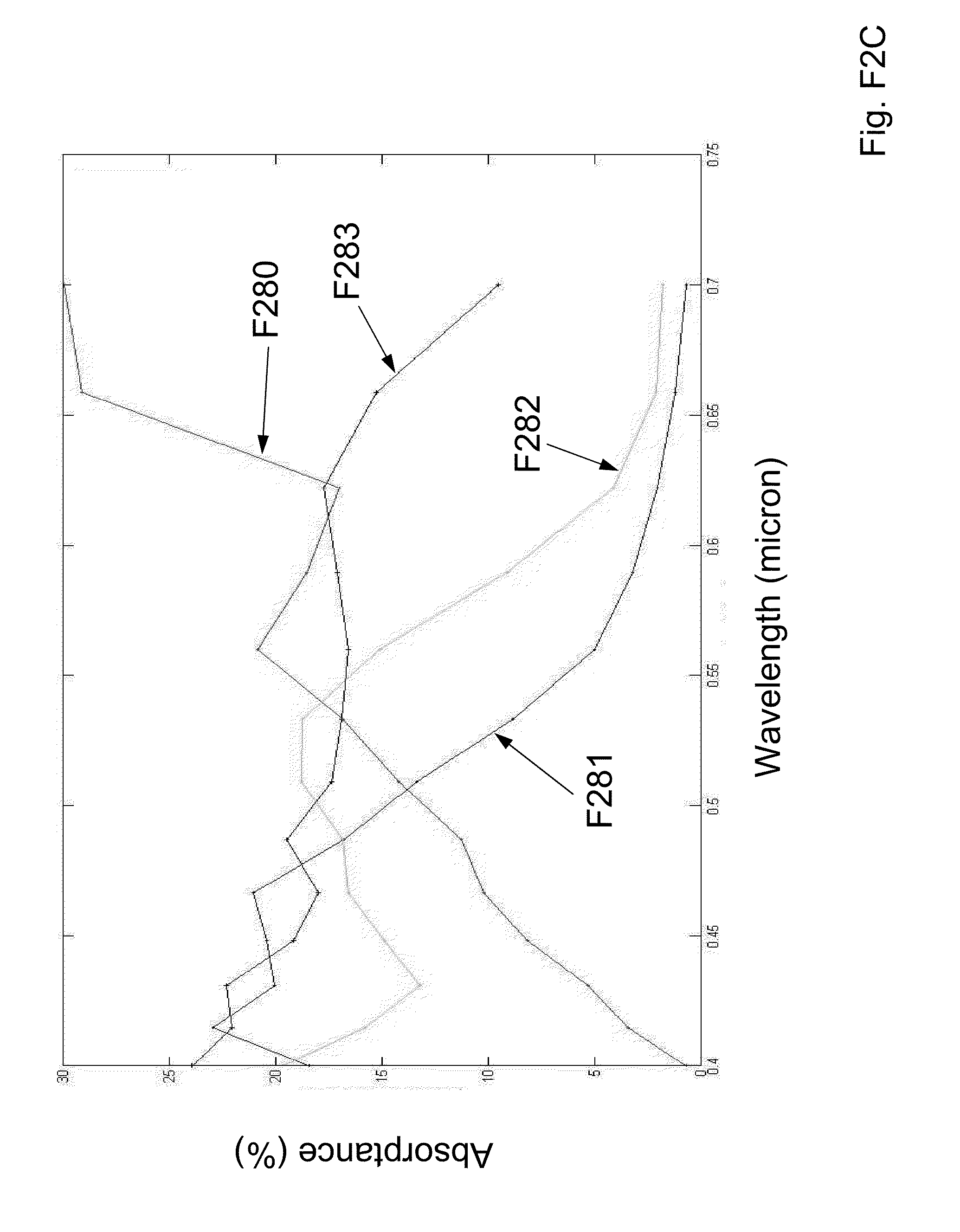

[0051] FIG. F2C shows exemplary absorption spectra of three nanowires in three subpixels in a pixel of the image sensor of FIG. F2A and the substrate of the image sensor of FIG. F2A.

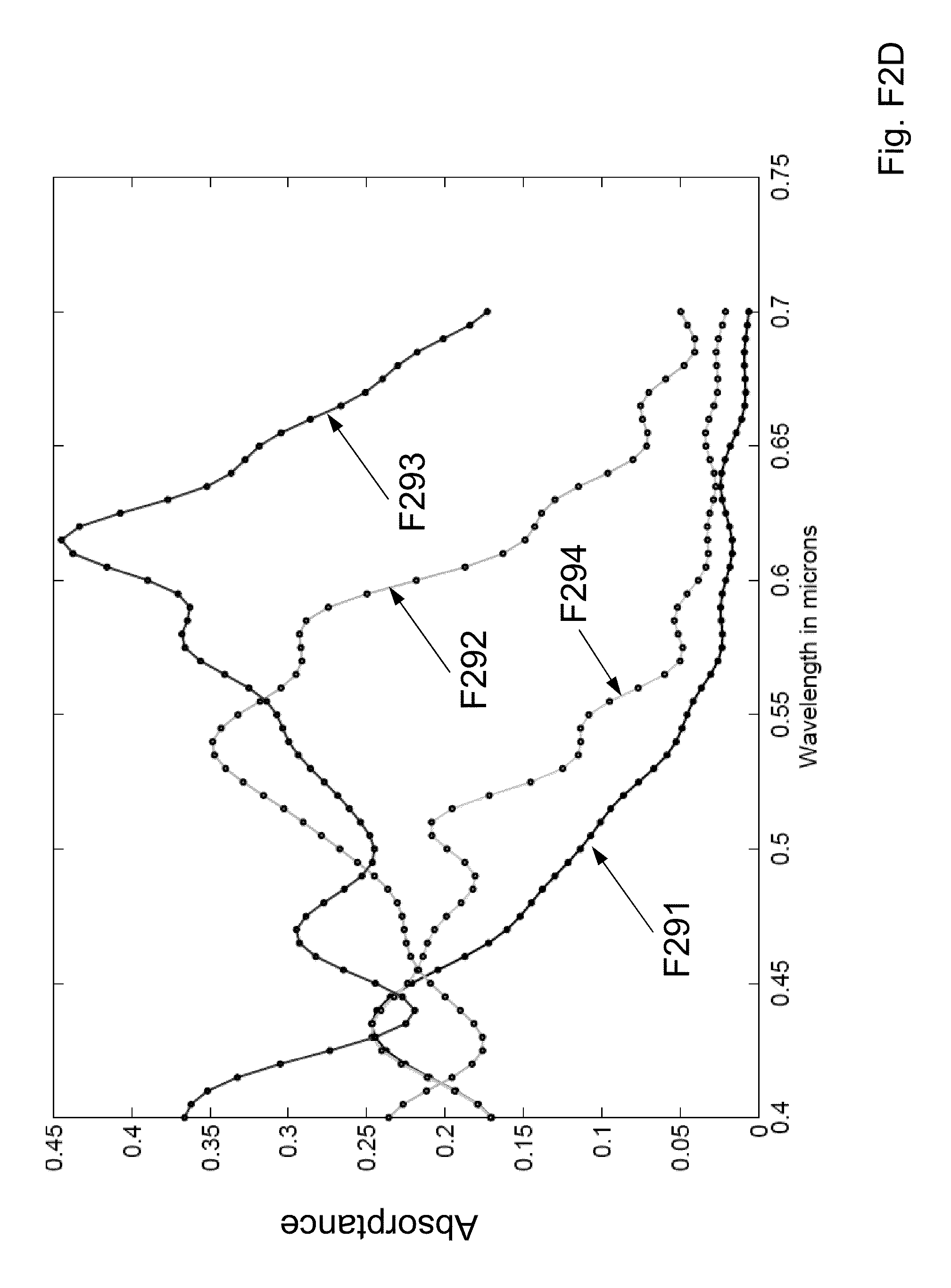

[0052] FIG. F2D shows exemplary absorption spectra of four nanowires in four subpixels in a pixel of the image sensor of FIG. F2A and the substrate of the image sensor of FIG. F2A.

[0053] FIG. F3 shows a schematic of couplers and an infrared filter.

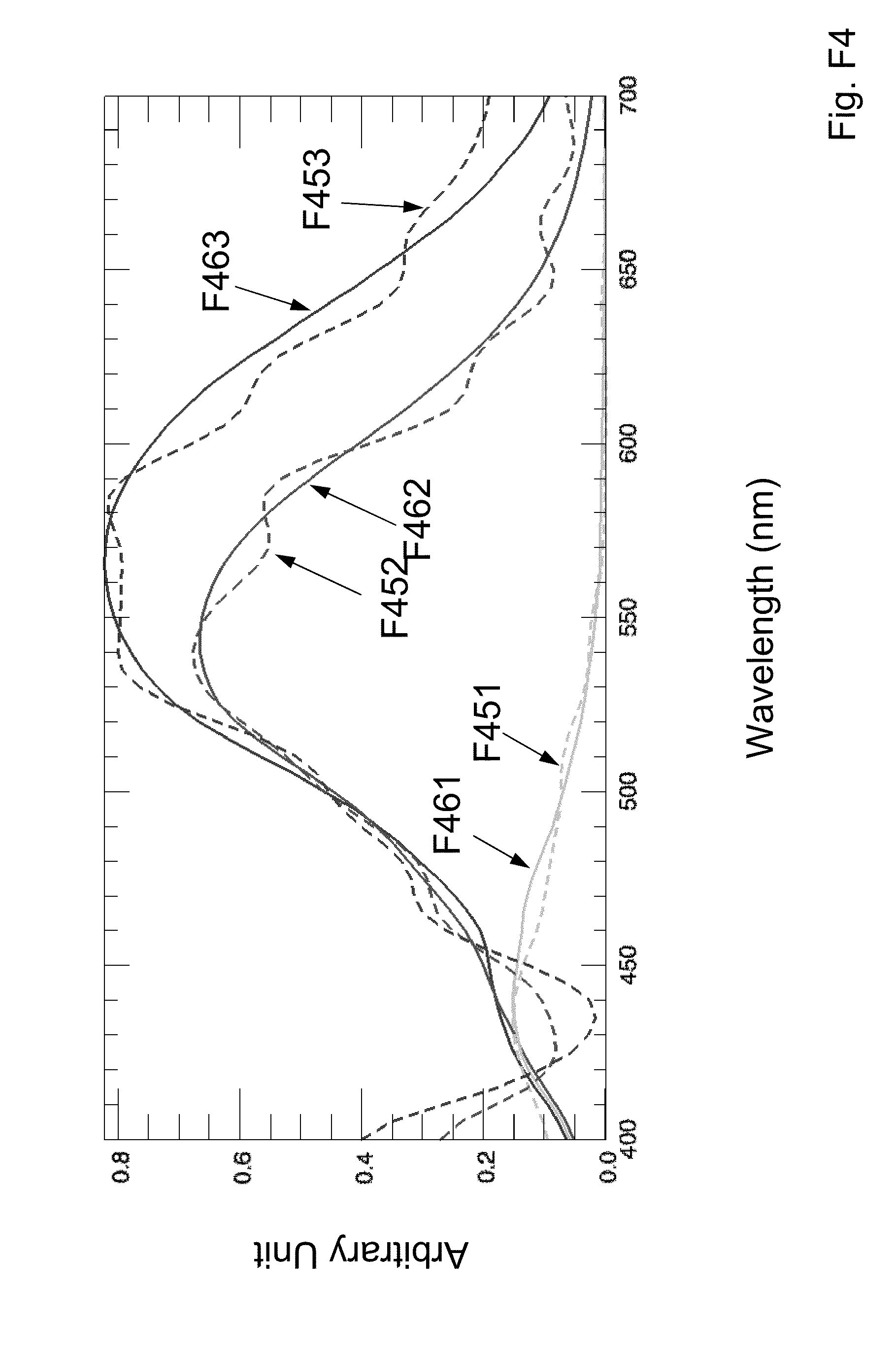

[0054] FIG. F4 shows exemplary color-matching functions of three subpixels in the image sensor, and color-matching functions the CIE standard observer.

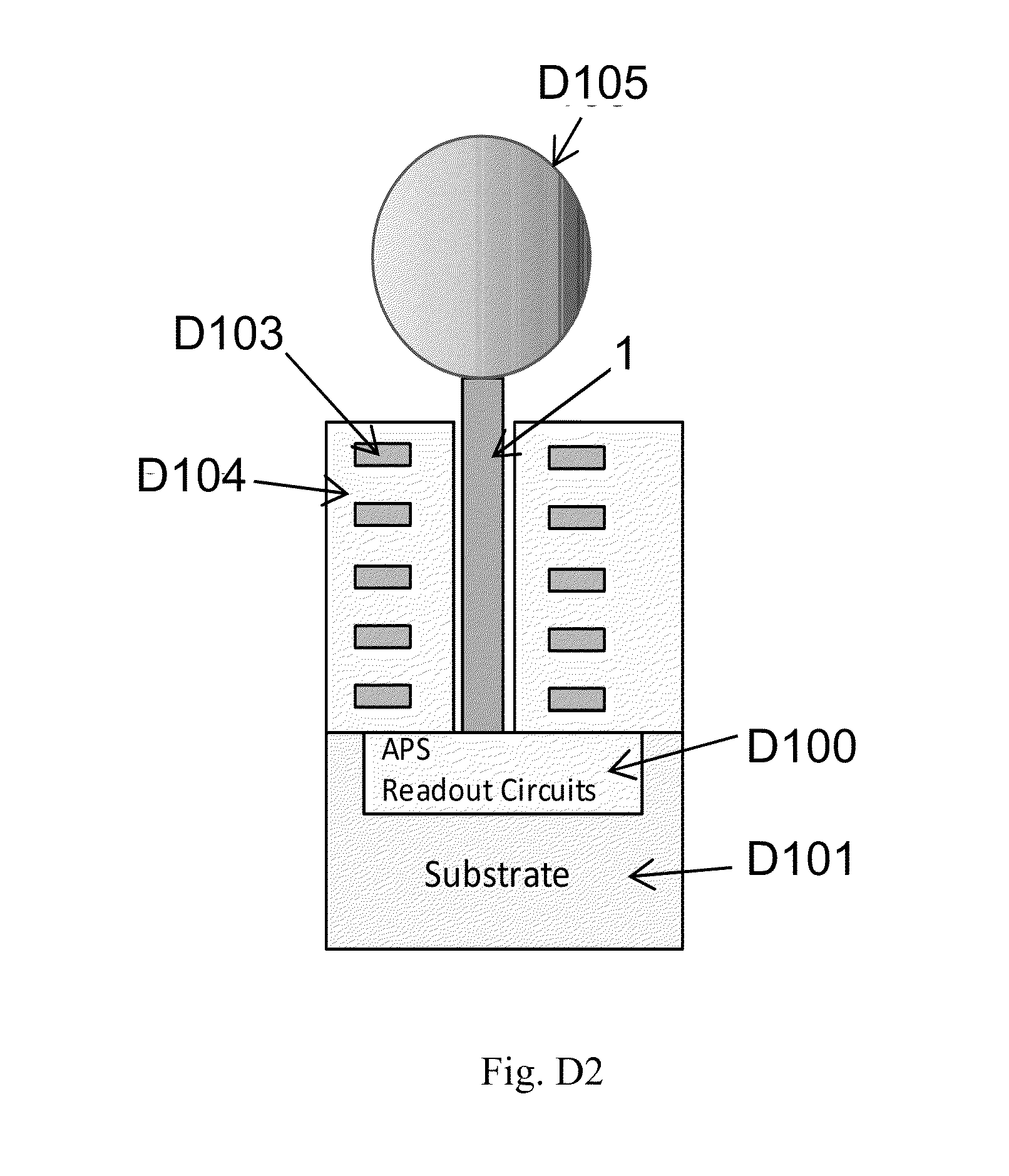

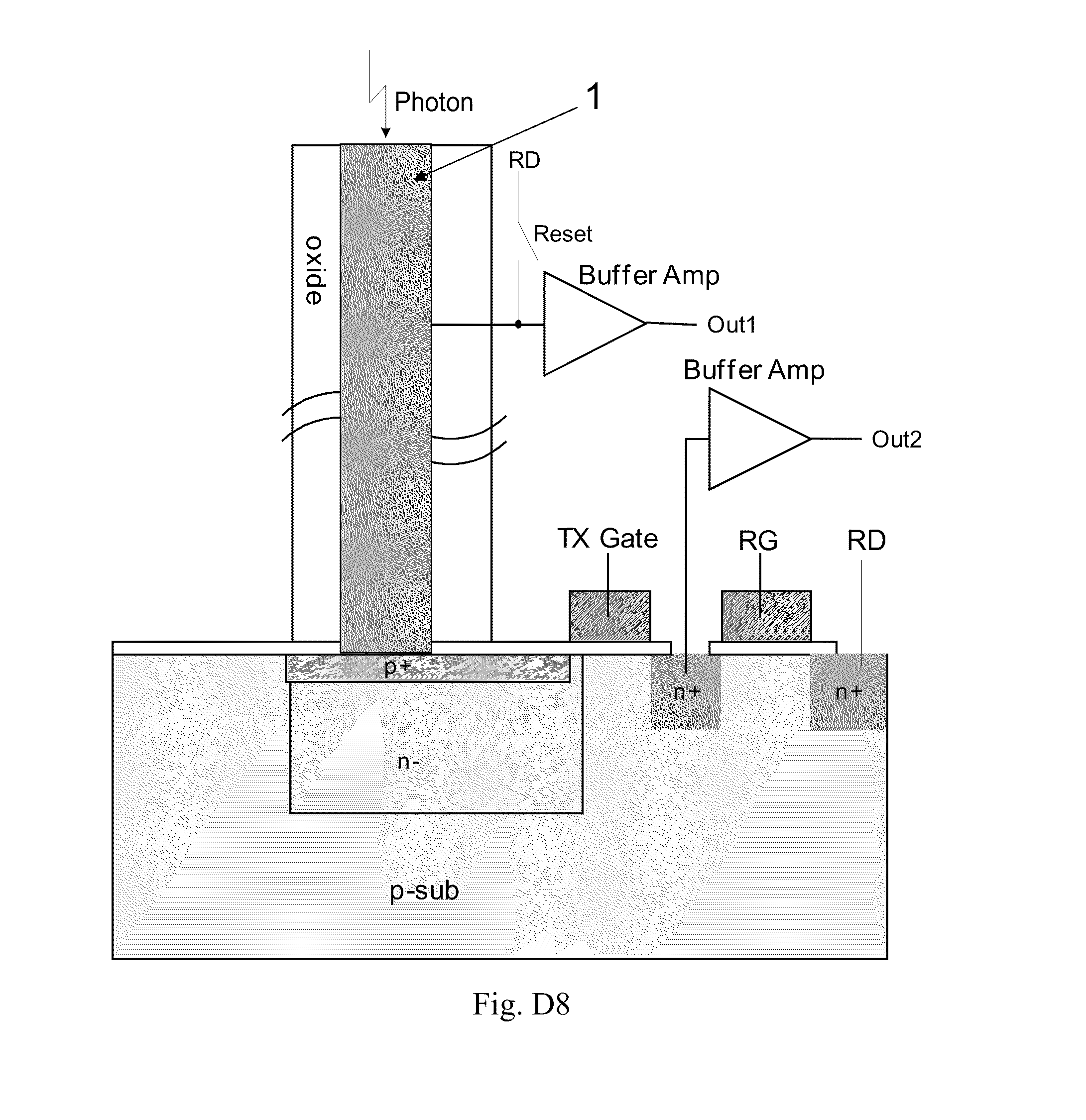

[0055] FIG. D2 illustrates a simplified cross sectional view of an embodiment of a pixel with a nanowire structured photodetector with front side illumination.

[0056] FIG. D2b illustrates an aspect of the embodiment illustrated in FIG. D2 with a binary microlens on the NW structured photodetector.

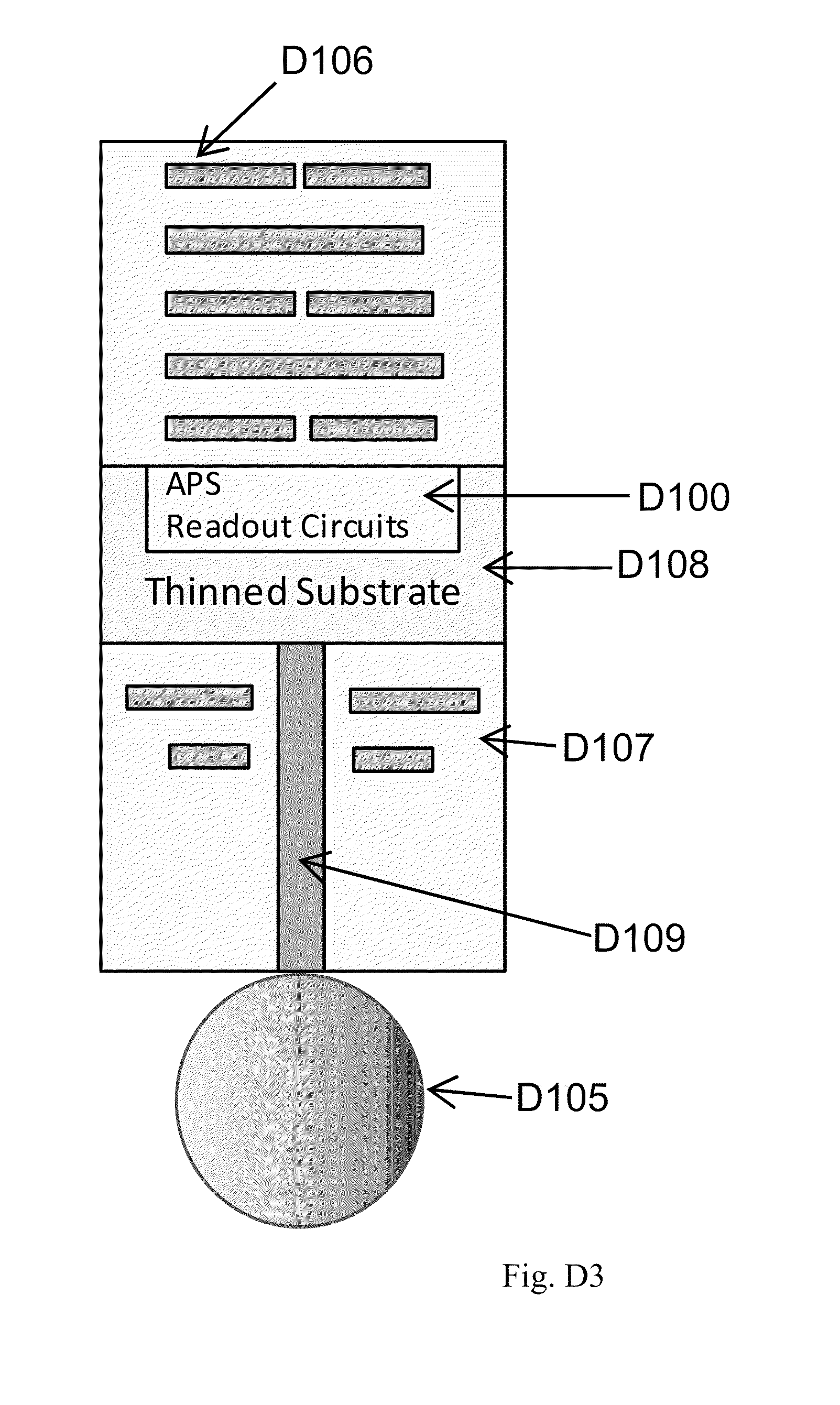

[0057] FIG. D3 illustrates simplified cross section view of an embodiment of a pixel with a nanowire structured photodetector with backside illumination.

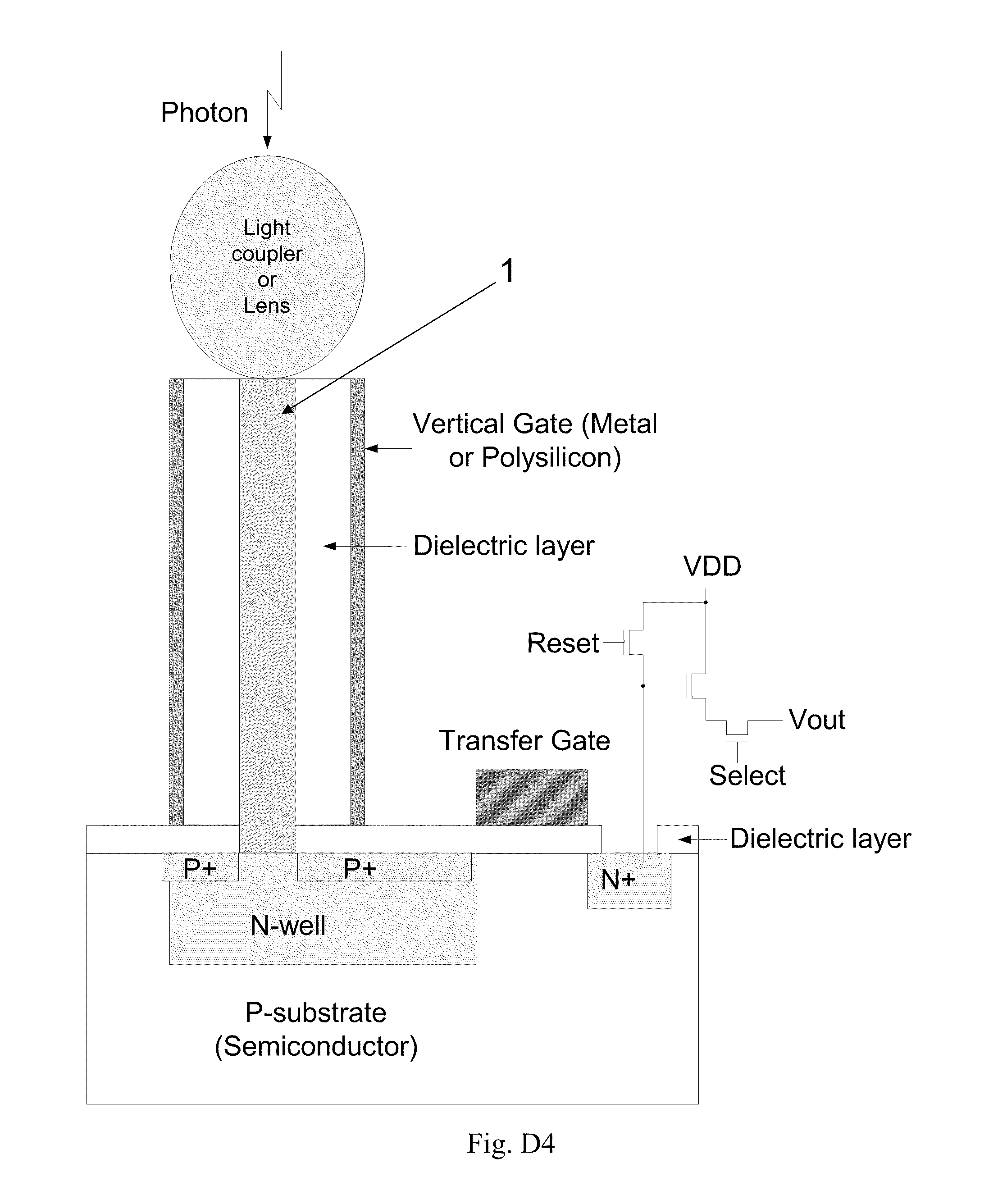

[0058] FIG. D4 illustrates an embodiment having a CMOS pixel with a nanowire and a vertical photogate (VPG).

[0059] FIG. D5b, illustrates a potential profile of an embodiment.

[0060] FIG. D8 illustrates a cross section view of an embodiment with a dual photodiode structure in which the p doped NW is coated with an n+ epitaxial layer to form a p-n junction.

[0061] FIG. D9 illustrates an embodiment of a CMOS pixel with a nanowire structured photogate detector.

[0062] FIG. D10 illustrates an embodiment of a CMOS active pixel with nanowire structured p-i-n photodiodes and vertical photogates around the NR.

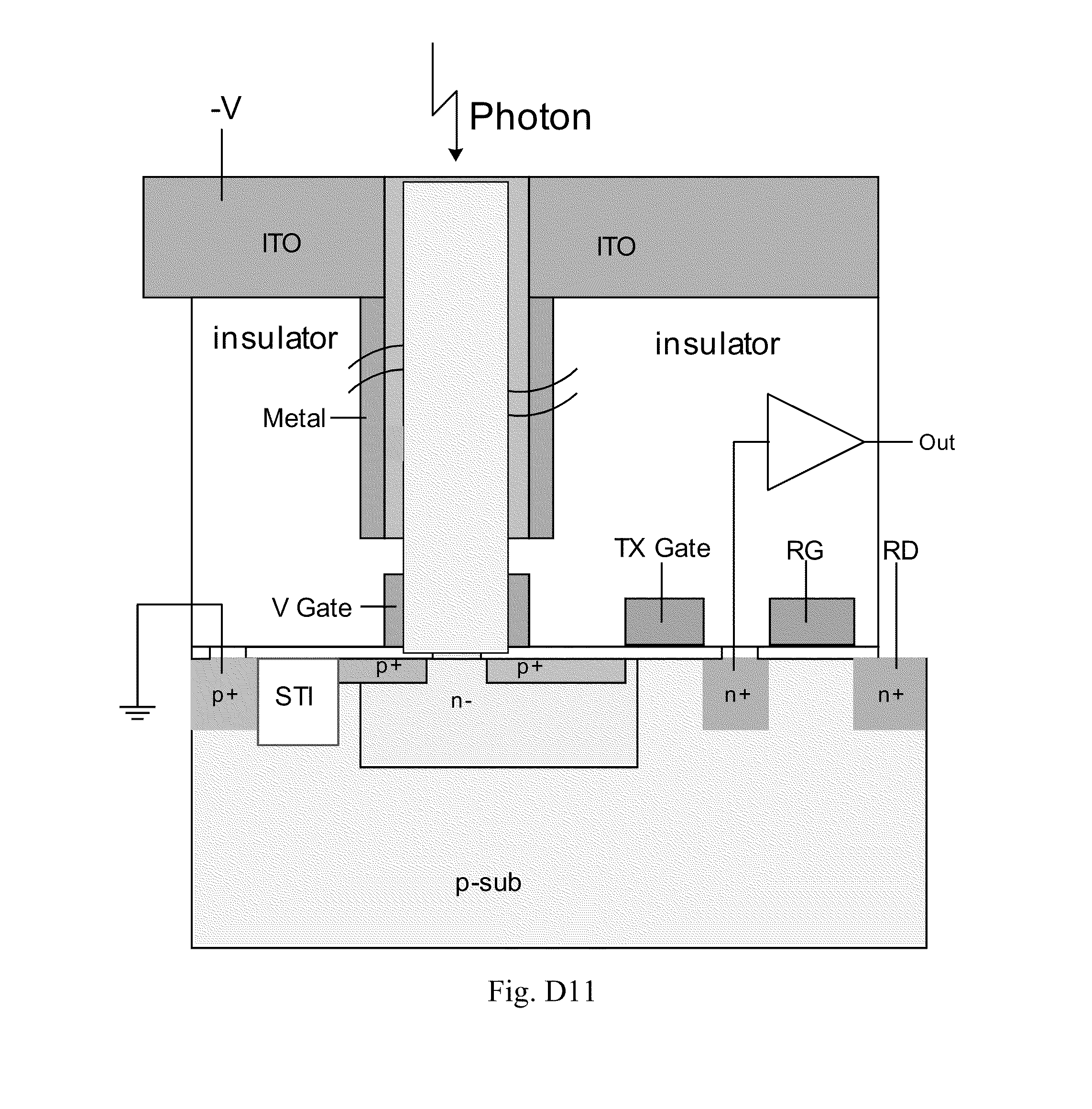

[0063] FIG. D11 illustrates another embodiment of a CMOS active pixel with nanowire structured p-i-n photodiodes and vertical photogates around the NR.

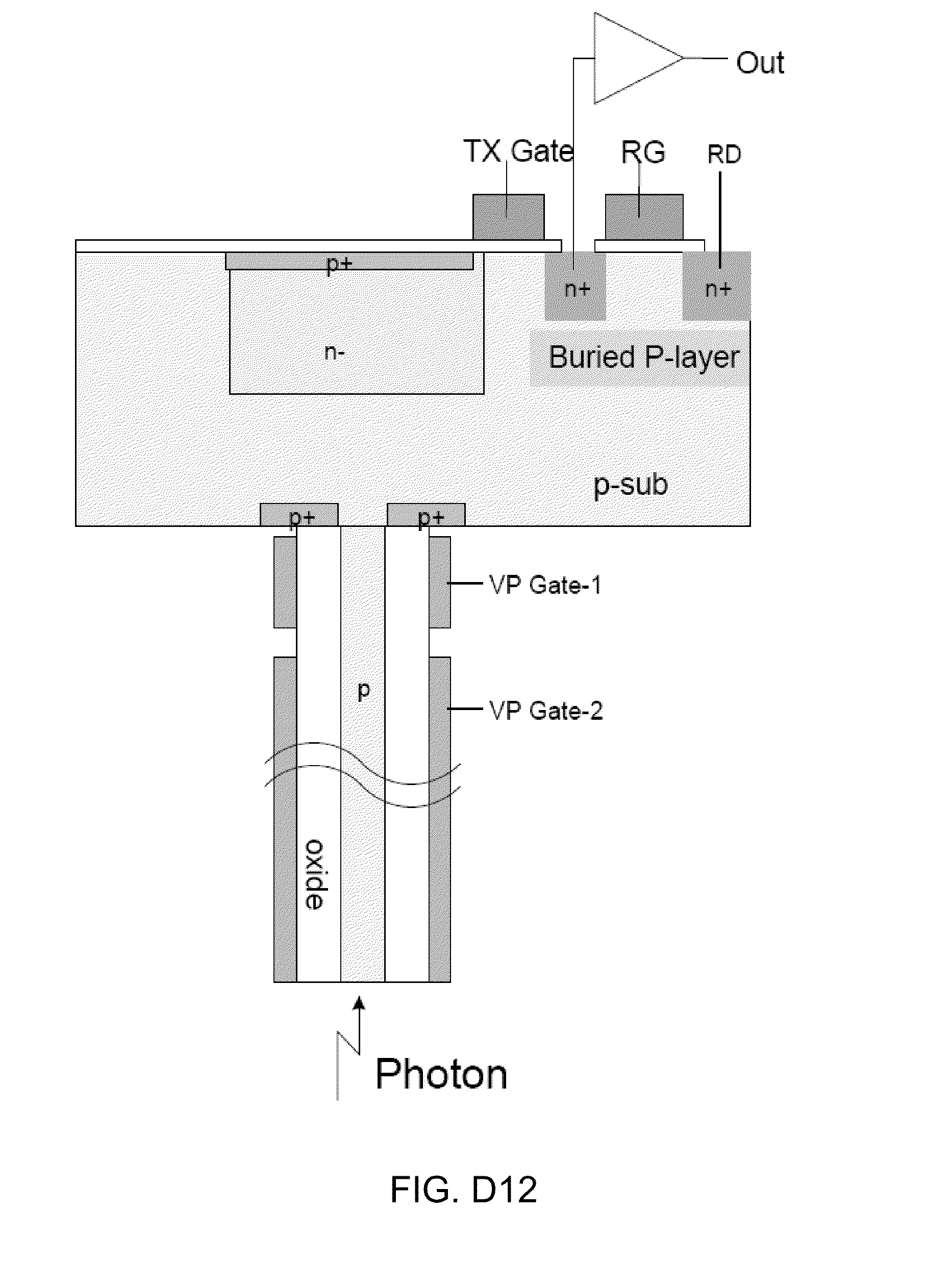

[0064] FIG. D12 illustrates an embodiments of a back-side illuminated image sensor.

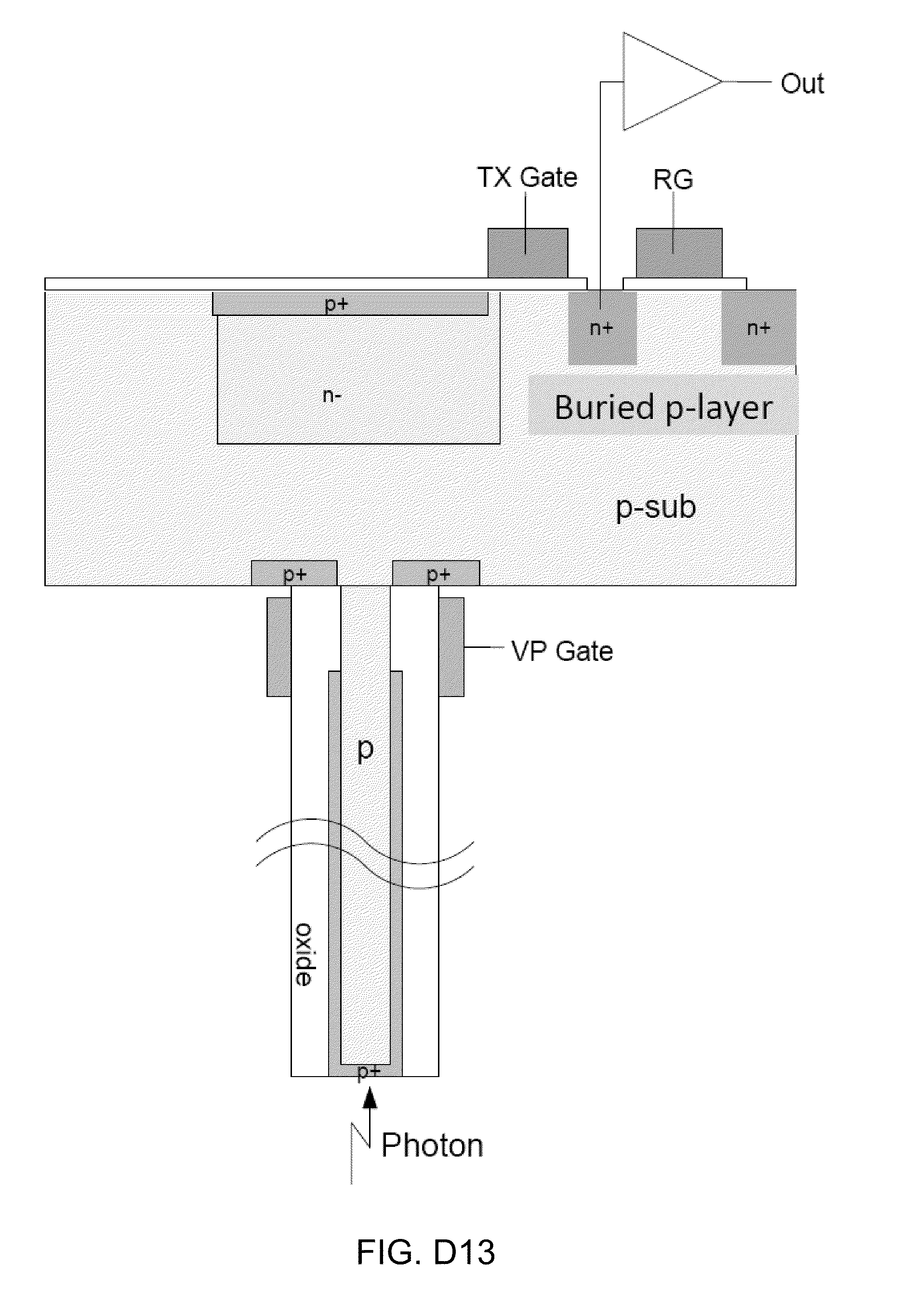

[0065] FIG. D13 illustrates an embodiments of another back-side illuminated image sensor.

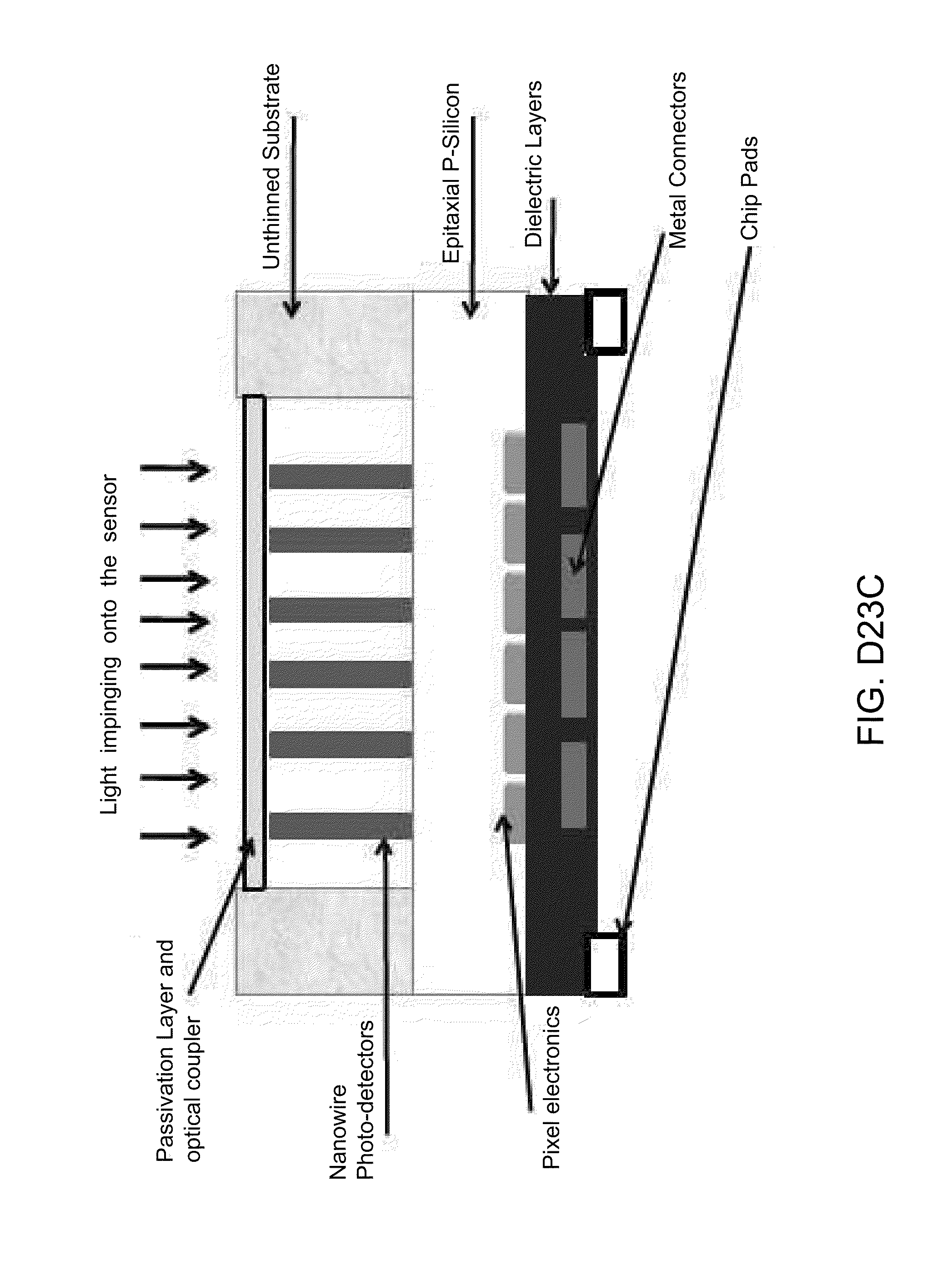

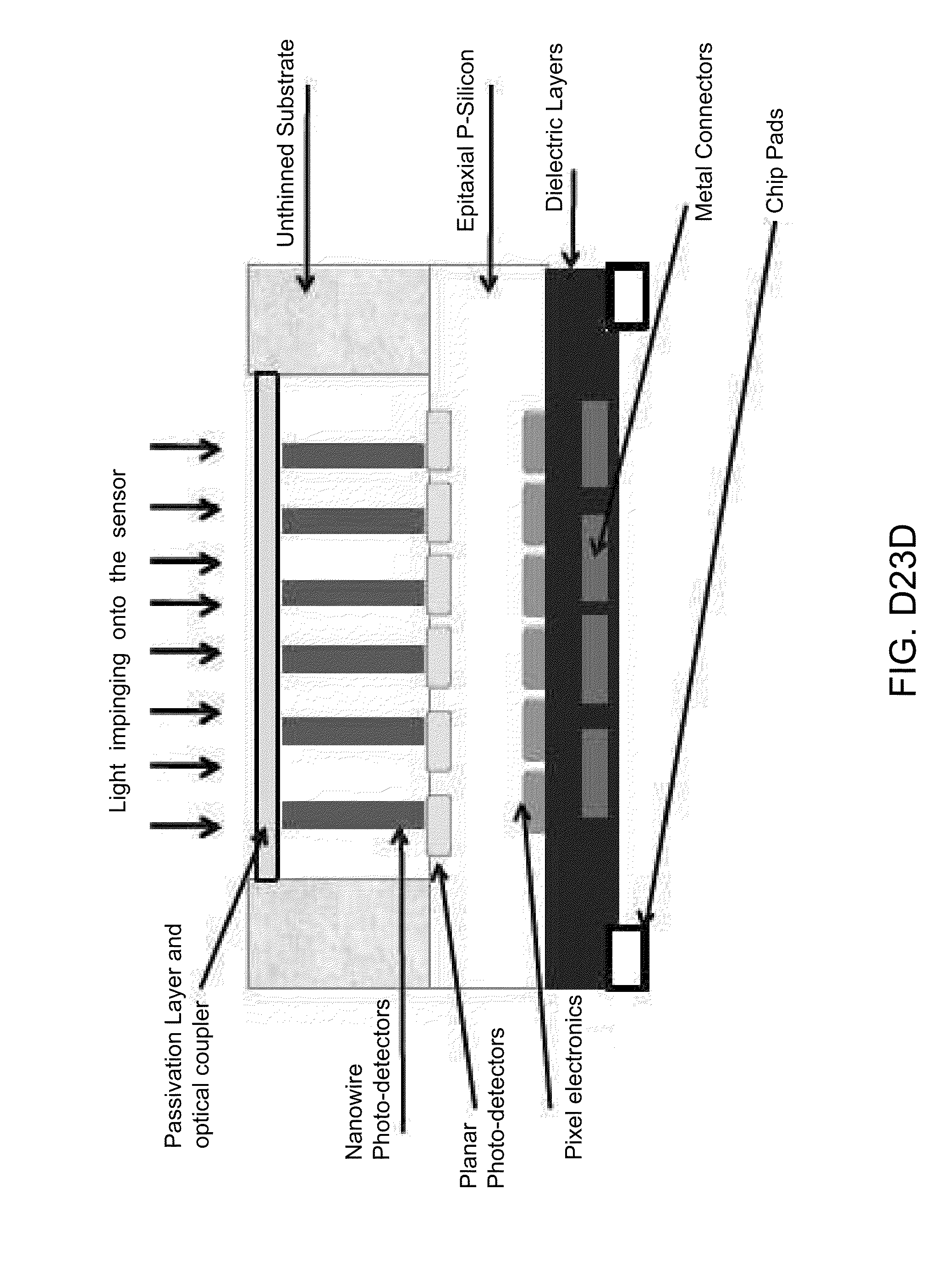

[0066] FIGS. D23C and D23D show illustrative embodiments of a cross-sectional view of a waveguide structure, such as a nanowire, containing backside-illuminated image sensor with nanowires located on the backside of the image sensor.

DETAILED DESCRIPTION

[0067] The terms "passivation" and "passivate" as used herein means a process of eliminating dangling bonds (i.e., unsatisfied valence on immobilized atoms). The term "image sensor" as used herein means a device that converts an optical image to an electric signal. The term "color image sensor" as used herein means an image sensor capable of converting an optical image in the visible spectrum (i.e. a color image) to an electric signal. The term "transparent" as used herein means a transmittance of at least 70%. The term "polarized light" as used herein means light with polarization. "Linear polarization" as used herein means the electric field of light is confined to a given plane along the direction of propagation of the light. "Circular polarization" as used herein means the electric field of light does not change strength but only changes direction in a rotary type manner. "Elliptical polarization" as used herein means electric field of light describes an ellipse in any fixed plane intersecting, and normal to, the direction of propagation of the light. The term "photovoltaic device" as used herein means a device that can generate electrical power by converting light such as solar radiation into electricity. That the structures are single crystalline as used herein means that the crystal lattice of the entire structures is continuous and unbroken throughout the entire structures, with no grain boundaries therein. An electrically conductive material can be a material with essentially zero band gap. The electrical conductivity of an electrically conductive material is generally above 103 S/cm. A semiconductor can be a material with a finite band gap up to about 3 eV and general has an electrical conductivity in the range of 103 to 10-8 S/cm. An electrically insulating material can be a material with a band gap greater than about 3 eV and generally has an electrical conductivity below 10-8 S/cm. The term "structures essentially perpendicular to the substrate" as used herein means that angles between the structures and the substrate is greater than zero, preferably greater than 5.degree., more preferably are from 85.degree. to 90.degree.. The term "recess" as used herein means a hollow space in the substrate and is open to a space outside the substrate. A group III-V compound material as used herein means a compound consisting of a group III element and a group V element. A group III element can be B, Al, Ga, In, TI, Sc, Y, the lanthanide series of elements and the actinide series of elements. A group V element can be V, Nb, Ta, Db, N, P, As, Sb and Bi. A group II-VI compound material as used herein means a compound consisting of a group II element and a group VI element. A group II element can be Be, Mg, Ca, Sr, Ba and Ra. A group VI element can be Cr, Mo, W, Sg, O, S, Se, Te, and Po. A quaternary material is a compound consisting of four elements. The term "mesh" as used herein means a web-like pattern or construction. The term "overhanging portion" as used herein means a portion of the structures that project over the sidewall of the recesses. The term "contour of a top surface of the structures" as used herein means the edge of the top surface of the structures. The term "electrode" as used herein means a conductor used to establish electrical contact with the photovoltaic device. The term "continuous" as used herein means having no gaps, holes, or breaks. The term "p-i-n junction" as used herein means a structure of a lightly doped or intrinsic semiconductor region sandwiched between a p-type semiconductor region and an n-type semiconductor region. The p-type and n-type regions can be heavily doped for Ohmic contacts. The term "p-n junction" as used herein means a structure with a p-type semiconductor region and an n-type semiconductor region in contact with each other. The term "gate electrode" as used herein means an electrode operable to control electrical current flow by a voltage applied on the gate electrode. The term "nanopillar" as used herein means a structure that has a size constrained to at most 1000 nm in two dimensions and unconstrained in the other dimension. The term "nanopillar" can also mean a structure that has a size constrained to at most 10 microns in two dimensions and unconstrained in the other dimension. The term "gate line" as used herein means an electrode or a conductor line operable to transmit an electrical signal to the gate electrodes. The term "multiplexer" as used herein means a device that performs multiplexing; it selects one of many analog or digital input signals and forwards the selected input into a single line. An analog-to-digital converter (abbreviated ADC, A/D or A to D) is a device that converts a continuous quantity to a discrete digital number. A digital-to-analog converter (DAC or D-to-A) is a device that converts a digital (usually binary) code to an analog signal (current, voltage, or electric charge). The term "foreoptics" as used herein means optical components (e.g., lenses, mirrors) placed in an optical path before the image sensor.

[0068] An intrinsic semiconductor, also called an undoped semiconductor or i-type semiconductor, is a substantially pure semiconductor without any significant dopant species present. A heavily doped semiconductor is a semiconductor with such a high doping level that the semiconductor starts to behave electrically more like a metal than as a semiconductor. A lightly doped semiconductor is a doped semiconductor but not have a doping level as high as a heavily doped semiconductor. In a lightly doped semiconductor, dopant atoms create individual doping levels that can often be considered as localized states that can donate electrons or holes by thermal promotion (or an optical transition) to the conduction or valence bands respectively. At high enough impurity concentrations (i.e. heavily doped) the individual impurity atoms may become close enough neighbors that their doping levels merge into an impurity band and the behavior of such a system ceases to show the typical traits of a semiconductor, e.g. its increase in conductivity with temperature. A "single crystalline" semiconductor as used herein means that the crystal lattice of the semiconductor is continuous and unbroken, with no grain boundaries therein. A semiconductor being "multi-crystalline" as used herein means that the semiconductor comprises grains of crystals separated by grain boundaries. A semiconductor being "amorphous" as used herein means that the semiconductor has a disordered atomic structure.

[0069] FIGS. 1A-1C each show a partial cross-sectional view of a nanostructure 1 extending essentially perpendicularly from a substrate 20.

[0070] As shown in a partial cross-sectional view of FIG. 1A, a nanostructure 1, according to an embodiment, extends essentially perpendicularly from a substrate 20 and comprises a core 11 of a doped semiconductor material, an intrinsic amorphous semiconductor layer 12 disposed isotropically over at least an end portion 14 away from the substrate 20, and a heavily doped amorphous semiconductor layer 13 of an opposite type from the core 11 and disposed isotropically over at least a portion of the intrinsic amorphous semiconductor layer 12.

[0071] As shown in a partial cross-sectional view of FIG. 1B, a nanostructure 1, according to an embodiment, extends essentially perpendicularly from a substrate 20 and comprises a core 11 of a doped semiconductor material, an intrinsic amorphous semiconductor layer 12 disposed on an end surface 16 away from the substrate 20, and a heavily doped amorphous semiconductor layer 13 of an opposite type from the core 11 and disposed on the intrinsic amorphous semiconductor layer 12. Preferably, the intrinsic amorphous semiconductor layer 12 and the heavily doped amorphous semiconductor layer 13 are coextensive with the core 11 in at least a direction parallel to the substrate 20. Preferably, sidewalls of the core 11 are at least partially covered by an electrically insulating layer 15.

[0072] As shown in a partial cross-sectional view of FIG. 1C, a nanostructure 1, according to an embodiment, extends essentially perpendicularly from a substrate 20 and comprises a core 11 of a doped semiconductor material, an intrinsic amorphous semiconductor layer 12 disposed on an end surface 16 away from the substrate 20, and a heavily doped amorphous semiconductor layer 13 of an opposite type from the core 11 and disposed on the intrinsic amorphous semiconductor layer 12. Preferably, sidewalls of the core 11 are at least partially covered by an electrically insulating layer 15. Preferably, the intrinsic amorphous semiconductor layer 12 and the heavily doped amorphous semiconductor layer 13 are coextensive with the electrically insulating layer 15 in at least a direction parallel to the substrate 20.

[0073] The substrate 20 can comprise any suitable material: semiconductor (e.g., silicon), insulator (e.g., glass), metal (e.g., gold). The substrate 20 can comprise any suitable electronic components such as transistors, interconnects, vias, diodes, amplifiers, etc.

[0074] The core 11 can comprise any suitable doped semiconductor material, such as doped silicon, doped germanium, doped III-V group compound semiconductor (e.g., gallium arsenide, gallium nitride, etc.), doped II-VI group compound semiconductor (e.g., cadmium selenide, cadmium sulfide, cadmium telluride, zinc oxide, zinc selenide, etc.), or doped quaternary semiconductor (e.g., copper indium gallium selenide). The core 11 is preferably substantially crystalline semiconductor material. The core 11 is preferably lightly doped. The core 11 can comprise a p-n junction or a p-i-n junction therein.

[0075] The intrinsic amorphous semiconductor layer 12 can comprise any suitable intrinsic amorphous semiconductor material, such as intrinsic amorphous silicon, intrinsic amorphous germanium, intrinsic amorphous III-V or II-VI group compound semiconductor. The intrinsic amorphous semiconductor layer 12 preferably has a thickness of about 2 nm to about 100 nm, more preferably about 2 nm to about 30 nm. The intrinsic amorphous semiconductor layer 12 is configured to passivate at least a surface of the core 11. The intrinsic amorphous semiconductor layer 12 can be deposited by any suitable method such as atomic layer deposition (ALD) or chemical vapor deposition (CVD).

[0076] The heavily doped amorphous semiconductor layer 13 can comprise any suitable heavily doped amorphous semiconductor material, such as heavily doped amorphous silicon, heavily doped amorphous germanium, heavily doped amorphous III-V or II-VI group compound semiconductor. The heavily doped amorphous semiconductor layer 13 being an opposite type from the core 11 means that if the core is p-type, the heavily doped amorphous semiconductor layer 13 is n-type and that if the core is n-type, the heavily doped amorphous semiconductor layer 13 is p-type. The heavily doped amorphous semiconductor layer 13 preferably has a thickness of at least about 10 nm, for example, from about 10 nm to about 200 nm. The heavily doped amorphous semiconductor layer 13 can be deposited by any suitable method such as atomic layer deposition (ALD) or chemical vapor deposition (CVD).

[0077] The heavily doped amorphous semiconductor layer 13, the intrinsic amorphous semiconductor layer 12 and the core 11 form a p-i-n junction.

[0078] The electrically insulating layer 15 can comprise any suitable material, such as HfO.sub.2, SiO.sub.2, Al.sub.2O.sub.3, Si.sub.3N.sub.4, etc.

[0079] The nanostructure 1 can be a nanowire or a nanoslab. The term "nanowire" used herein means a structure whose dimension in a direction perpendicular to the substrate (hereafter referred to as the "normal direction") is substantially greater than dimensions of the structure in any direction perpendicular to the normal direction (hereafter referred to as a "transverse direction") and the dimensions in the transverse directions are less than 1000 nm. The term "nanoslab" used herein means a structure whose dimensions in the normal direction and in the transverse direction are substantially greater than a dimension of the structure in a direction perpendicular to both the normal direction and the transverse direction (hereafter referred to as the "thickness direction") and the dimension in the thickness direction is less than 1000 nm. A nanoslab can have any suitable shape in a cross-section parallel to the substrate, such as a rectangle, an ellipse, convex-convex (i.e. like a double-convex lens), concave-concave (i.e. like a double-concave lens), plano-convex (i.e. like a plano-convex lens), plano-concave (i.e. like a plano-concave lens).

[0080] According to an embodiment, the nanostructure 1 is configured as a solar blind ultra violet (SBUV) detector. The SBUV region is the range of wavelengths in which the earth atmosphere absorbs essentially all UV radiation from the sun to the earth. For example, the wavelength region of 300 nm to 200 nm is within the SBUV region. A device that detects radiation only in the SBUV region and rejects visible and infrared radiation is called an SBUV detector or an SBUV sensor.

[0081] Sunlight does not interfere or blind a SBUV detector of the embodiments herein. Therefore, the SBUV detector of the embodiments herein is particularly useful for detecting manmade radiation sources that emit in the SBUV region and enjoys a very low false alarm rate. Such manmade radiation sources can include exhaust plumes of shoulder launched surface to air missiles (SLSAM), fire and flame, or any other UV emitting source including hydrogen flames. An SBUV detector of the embodiments herein can function at all lightning conditions including full daylight, without interference from the solar radiation and with very high signal to background ratio.

[0082] According to an embodiment, the SBUV detector comprises a substrate having a plurality of regions defined thereon (hereafter referred to as "pixels"). In each pixel, the SBUV detector comprises a plurality of nanostructures 1 extending essentially perpendicularly from the substrate. The nanostructures 1 in the SBUV detector are nanowires. The plurality of nanostructures 1 can be equally or unequally spaced from each other, arranged in a regular array or in random. The plurality of nanostructures 1 are configured to react only to radiations in the SBUV region and not to react to radiations outside the SBUV region. Here, the term "react" is meant to broadly encompass absorbing, reflecting, coupling to, detecting, interacting with, converting to electrical signals, etc.

[0083] FIG. S1A shows one of the plurality of nanostructures 1 (a nanowire in the SBUV) on an SBUV S10. For brevity, only one nanostructure 1 is shown but the SBUV S10 can comprise a plurality of nanostructures 1, such as more than 1000, or more than 1000000. The nanostructures 1 extend essentially perpendicularly from a substrate S130. Each of the nanostructures 1 preferably comprises a cladding S120 surrounding the nanostructures 1. The substrate S130 is preferably a metal. The nanostructures 1 preferably have higher refractive index than the cladding S120. The term "cladding" or "clad" as used herein means a layer of substance surrounding the nanostructures 1.

[0084] FIG. S1B shows simulated absorptance of the SBUV detector S10 of UV light with wavelengths between 100 and 400 nm, incident in the normal direction. FIG. S1B clearly shows that absorptance of the SBUV detector S10 of UV light with wavelengths between 140 and 290 nm is greater than 50% and absorptance of UV light drops quickly to almost zero outside wavelength region of 140-290 nm. FIG. S1B indicate that the SBUV detector S10 indeed only reacts to radiations in the SBUV region. As shown in FIG. S1C, each of the nanostructures 1 can further comprise a coupler S140 disposed on an end of the nanostructures 1 away from the substrate S130 (hereafter referred to as the "receiving end"). The term "coupler" as used herein means a layer effective to guide light into the nanostructures 1.

[0085] According to an embodiment, the nanostructures 1 are nanowires and have a diameter of from about 5 nm to about 30 nm, preferably about 20 nm. According to an embodiment, the nanostructures 1 have a diameter of from about 5 nm to about 150 nm. The cladding S130 has a thickness of about 10 nm to about 200 nm, preferably about 30 nm. Pitch of the nanostructures 1 (i.e. center-to-center distance of one of the plurality of nanowires to a nearest neighbor thereof) is from about 0.2 .mu.m to about 2 .mu.m. Height (i.e. dimension in the normal direction) of the nanostructures 1 is from about 0.1 .mu.m to about 5 .mu.m. Each pixel can have one or more nanostructures 1.

[0086] FIG. S2A and FIG. S2B shows a perspective view and a top view, respectively, of the SBUV detector S10. For brevity, only four pixels (regions enclosed by dotted rectangles) are shown. The nanostructures 1 preferably detect UV radiation in the SBUV region by converting it to an electrical signal. For example, each nanostructure 1 can comprise a photodiode (such as an avalanche photodiode) or form a photodiode (such as an avalanche photodiode) with the substrate S130. The SBUV detector S10 can further comprise electrical components configured to detect the electrical signal from the nanostructures 1, for example, Readout Integrated Circuits (ROIC) in the substrate S130, an electrode S150 disposed between and electrically connected to all the nanostructures 1 on each pixel, a common electrode S160 disposed on and electrically connected to the receiving ends of all the nanostructures 110 in the entire SBUV detector S10. Preferably, the SBUV detector S10 can detect electrical signals from the nanostructures 1 in different pixels separately.

[0087] According to one embodiment as shown in FIG. S9, the SBUV detector S10 can be integrated with electronic circuitry into a solar-blind image sensor. The electronic circuitry can include address decoders, a correlated double sampling circuit (CDS), a signal processor, a multiplexor and a high voltage supply (e.g. a DC high voltage supply capable of supplying at least 50 V, 100 V, 200 V or higher) for driving the nanostructures 1. The electronic circuitry is functional to detect the electrical signal generated by the nanostructures 1.

[0088] The SBUV detector S10 can also be used as fore optics in a light detector apparatus as shown in the schematic in FIG. S10.

[0089] Polarization is a property of certain types of waves that describes the orientation of their oscillations. Electromagnetic waves including visible light can exhibit polarization. By convention, the polarization of light is described by specifying the orientation of the light's electric field at a point in space over one period of the oscillation. When light travels in free space, in most cases it propagates as a transverse wave, i.e. the polarization is perpendicular to the light's direction of travel. In this case, the electric field may be oriented in a single direction (linear polarization), or it may rotate as the wave travels (circular or elliptical polarization). In the latter cases, the oscillations can rotate either towards the right or towards the left in the direction of travel. Depending on which rotation is present in a given wave it is called the wave's chirality or handedness. Polarization of fully polarized light can be represented by a Jones vector. The x and y components of the complex amplitude of the electric field of light travel along z-direction, E.sub.x(t) and E.sub.y(t), are represented as

( E x ( t ) E y ( t ) ) = E 0 ( E 0 x ( kz - .omega. t + .phi. x ) E 0 y ( kz - .omega. t + .phi. x ) ) = E 0 ( kz - .omega. t ) ( E 0 x .phi. x E 0 y .phi. y ) ( E 0 x .phi. x E 0 y .phi. y ) ##EQU00001##

is the Jones vector. Polarization of light with any polarization, including unpolarized, partially polarized, and fully polarized light, can be described by the Stokes parameters, which are four mutually independent parameters.

[0090] A device that can detect polarization of light, or even measure the light's Jones vector or Stokes parameters can be useful in many application.

[0091] According to an embodiment, the device comprises a substrate having a plurality of regions defined thereon (hereafter referred to as "subpixels"; a group of related "subpixels" may be referred to as a "pixel"). In each subpixel, the device comprises a plurality of nanostructures 1 being nanoslabs. The plurality of nanostructures 1 can be equally or unequally spaced from each other. The plurality of nanostructures 1 in different subpixels are functional to react differently to light with a same polarization. Here, the term "react" is meant to broadly encompass absorbing, reflecting, coupling to, detecting, interacting with, converting to electrical signals, etc. The plurality of nanostructures 1 in a first subpixel extends in a first transverse direction; the plurality of nanostructures 1 in a second subpixel extends in a second transverse direction, wherein the first and second pixels are adjacent and the first transverse direction is different from the second transverse direction.

[0092] FIG. P1 shows a device P10 according to one embodiment. For brevity, two subpixels P10a and P10b of a substrate P110 are illustrated. The device P10, however, can comprise a plurality of pixels such as more than 100, more than 1000, more than 1000000. The subpixels preferably have a pitch of about 1 micron to 100 microns (more preferably 5 microns). In each of the subpixels P10a and P10b, the device P10 comprises a plurality of nanostructures 1 (e.g. at least 2 features), respectively. The nanostructures 1 in the subpixel P10a and the nanostructures 1 in the subpixel P10b extend in different transverse directions. The nanostructures 1 preferably have a pitch (i.e. spacing between adjacent features 100 in the thickness direction thereof) of about 0.5 to 5 microns (further preferably about 1 micron), a height (i.e. dimension in the normal direction) of about 0.3 to 10 microns (further preferably about 5 micron) and an aspect ratio (i.e. ratio of a dimension in the transverse direction to a dimension in the thickness direction) of at least 4:1, preferably at least 10:1. Each of the nanostructures 1 forms a p-i-n diode with the substrate P110, the p-i-n diode being functional to convert at least a portion of light impinged thereon to an electrical signal. The device P10 preferably further comprises electrical components configured to detect the electrical signal from the nanostructures 1, for example, a transparent electrode disposed on each subpixel and electrically connected to all nanostructures 1 therein. The transparent electrode on each subpixel preferably is separate from the transparent electrode on adjacent subpixels. A reflective material can be deposited on areas of the substrate P110 between the nanostructures 1. The substrate P110 can have a thickness in the normal direction of about 5 to 700 microns (preferably 120 microns).

[0093] FIG. P2 shows a schematic of the nanostructures 1 in one subpixel when light with different polarization impinges thereon. For light P15a with a wavelength of about 400 nm and a linear polarization essentially in the thickness direction of the nanostructures 1, the absorptance of the nanostructures 1 is about 35%. In contrast, for light P15b with the same wavelength as light P15a and a linear polarization essentially in the transverse direction of the nanostructures 1, the absorptance of the nanostructures 1 is about 95%.

[0094] According to one embodiment as shown in FIG. P10, the device P10 can be integrated with electronic circuitry into a polarization detector array. The electronic circuitry can include address decoders in both directions of the detector array, a correlated double sampling circuit (CDS), a signal processor, a multiplexor. The electronic circuitry is functional to detect the electrical signal converted by the nanostructures 100 from at least a portion of light impinged thereon. The electric circuitry can be further functional to calculate an interpolation of electrical signals from several subpixels, the features on which extend in the same transverse direction. Other function of the electronic circuitry can include a gain adjustment, a calculation of Stoke's parameters. In particular, the subpixels can be arranged into a group (i.e. pixel). For example, in FIG. P10, a subpixel A and subpixels B, C and D can be arranged adjacent to each other and referred to as a pixel, wherein features on the subpixels B, C and D extend in transverse directions at 45.degree., 90.degree. and -45.degree. relative to a transverse direction in which features on the subpixel A extend.

[0095] According to an embodiment as shown in FIG. P12, the nanostructures 100 can each comprise a metal layer on each sidewall (i.e. surface extending in the transverse direction and the normal direction). The metal layer preferably has a thickness of about 5 nm to about 100 nm, more preferably about 50 nm. The metal layer substantially covers the entire sidewall and the metal layer does not extend to either end of the nanostructures in the normal direction.

[0096] A photovoltaic device, also called a solar cell is a solid state device that converts the energy of sunlight directly into electricity by the photovoltaic effect. Assemblies of cells are used to make solar modules, also known as solar panels. The energy generated from these solar modules, referred to as solar power, is an example of solar energy.

[0097] The photovoltaic effect is the creation of a voltage (or a corresponding electric current) in a material upon exposure to light. Though the photovoltaic effect is directly related to the photoelectric effect, the two processes are different and should be distinguished. In the photoelectric effect, electrons are ejected from a material's surface upon exposure to radiation of sufficient energy. The photovoltaic effect is different in that the generated electrons are transferred between different bands (i.e. from the valence to conduction bands) within the material, resulting in the buildup of a voltage between two electrodes.

[0098] Photovoltaics is a method for generating electric power by using solar cells to convert energy from the sun into electricity. The photovoltaic effect refers to photons of light--packets of solar energy--knocking electrons into a higher state of energy to create electricity. At higher state of energy, the electron is able to escape from its normal position associated with a single atom in the semiconductor to become part of the current in an electrical circuit. These photons contain different amounts of energy that correspond to the different wavelengths of the solar spectrum. When photons strike a PV cell, they may be reflected or absorbed, or they may pass right through. The absorbed photons can generate electricity. The term photovoltaic denotes the unbiased operating mode of a photodiode in which current through the device is entirely due to the light energy. Virtually all photovoltaic devices are some type of photodiode.

[0099] A conventional solar cell often has opaque electrodes on a surface that receives light. Any light incident on such opaque electrodes is either reflected away from the solar cell or absorbed by the opaque electrodes, and thus does not contribute to generation of electricity. Therefore, a photovoltaic device that does not have this drawback is desired.

[0100] FIG. V2A shows a schematic cross-section of a photovoltaic device V200, according to another embodiment. The photovoltaic device V200 comprises a substrate V205, a plurality of nanostructures 1 essentially perpendicular to the substrate V205 and one or more recesses V230 between the nanostructures 1. Each recess V230 has a sidewall V230a and a bottom wall V230b. The bottom wall V230b has a planar reflective layer V232. The sidewall V230a does not have any planar reflective layer V232. A continuous cladding layer 240 is disposed over an entire the nanostructures 1. The photovoltaic device V200 can further comprise a coupling layer V260 disposed on the cladding layer V240 and only directly above the top surface V220a.

[0101] The nanostructures 1 can have any cross-sectional shape. For example, the nanostructures 1 can be cylinders or prisms with elliptical, circular, rectangular, polygonal cross-sections. The nanostructures 1 can also be strips as shown in FIG. V9, or a mesh as shown in FIG. V10. According to one embodiment, the nanostructures 1 are pillars with diameters from 50 nm to 5000 nm, heights from 1000 nm to 20000 nm, a center-to-center distance between two closest pillars of 300 nm to 15000 nm. Preferably, the nanostructures 1 have an overhanging portion V224 along an entire contour of the top surface V220a of the nanostructures 1.

[0102] Each recess V230 preferably has a rounded or beveled inner edge between the sidewall V230a and the bottom wall V230b.

[0103] The planar reflective layer V232 can be any suitable material, such as ZnO, Al, Au, Ag, Pd, Cr, Cu, Ti, a combination thereof, etc. The planar reflective layer V232 preferably is an electrically conductive material, more preferably a metal. The planar reflective layer V232 preferably has a reflectance of at least 50%, more preferably has a reflectance of at least 70%, most preferably has a reflectance of at least 90%, for visible light of any wavelength. The planar reflective layer V232 has a thickness of preferably at least 5 nm, more preferably at least 20 nm. The planar reflective layer V232 in all the recesses V230 is preferably connected. The planar reflective layer V232 is functional to reflect light incident thereon to the nanostructures 1 so the light is absorbed by the nanostructures 1. The planar reflective layer V232 preferably is functional as an electrode of the photovoltaic device V200.

[0104] The cladding layer V240 is substantially transparent to visible light, preferably with a transmittance of at least 50%, more preferably at least 70%, most preferably at least 90%. The cladding layer V240 can be made of an electrically conductive material. The cladding layer V240 preferably is made of a transparent conductive oxide, such as ITO (indium tin oxide), AZO (aluminum doped zinc oxide), ZIO (zinc indium oxide), ZTO (zinc tin oxide), etc. The cladding layer V240 can have a thickness of 50 nm to 5000 nm. The cladding layer V240 preferably forms an Ohmic contact with the nanostructures 1. The cladding layer V240 preferably forms an Ohmic contact with the planar reflective layer V232. The cladding layer V240 preferably is functional as an electrode of the photovoltaic device V200.

[0105] The substrate V205 preferably has a flat surface V250 opposite the nanostructures 1. The flat surface V250 can have a doped layer V251 of the opposite conduction type from the core 11 of the nanostructures 1, i.e. if the core 11 is n type, the doped layer V251 is p type; if the core 11 is p type, the doped layer V251 is n type. The doped layer V251 is electrically connected to each of the nanostructures 1. The flat surface V250 can also have a metal layer V252 disposed on the doped layer V251. The metal layer V252 forms an Ohmic contact with the doped layer V251. The substrate V205 preferably has a thickness of at least 50 microns. Total area of the planar reflective layer V232 is preferable at least 40% of a surface area of the flat surface 250.

[0106] The coupling layer V260 can be of the same material as the cladding layer V240 or different material from the cladding layer V240. As shown in FIG. V5, refractive index of the core 11 of the nanostructure 1 n.sub.1, refractive index of the cladding layer V240 n.sub.2, refractive index of the coupling layer V260 n.sub.3, refractive index of the space between the nanostructures 1 n.sub.4, preferably satisfy relations of n.sub.1>n.sub.2>n.sub.4 and n.sub.1>n.sub.3>n.sub.4, which lead to enhanced light concentration in the nanostructures 1.

[0107] In one embodiment, the nanostructures 1 are pillars arranged in an array, such as a rectangular array, a hexagonal array, a square array, concentric ring. Each pillar is about 5 microns in height. A pitch of the nanostructures 1 is from 300 nm to 15 microns. The cladding layer V240 is about 175 nm thick.

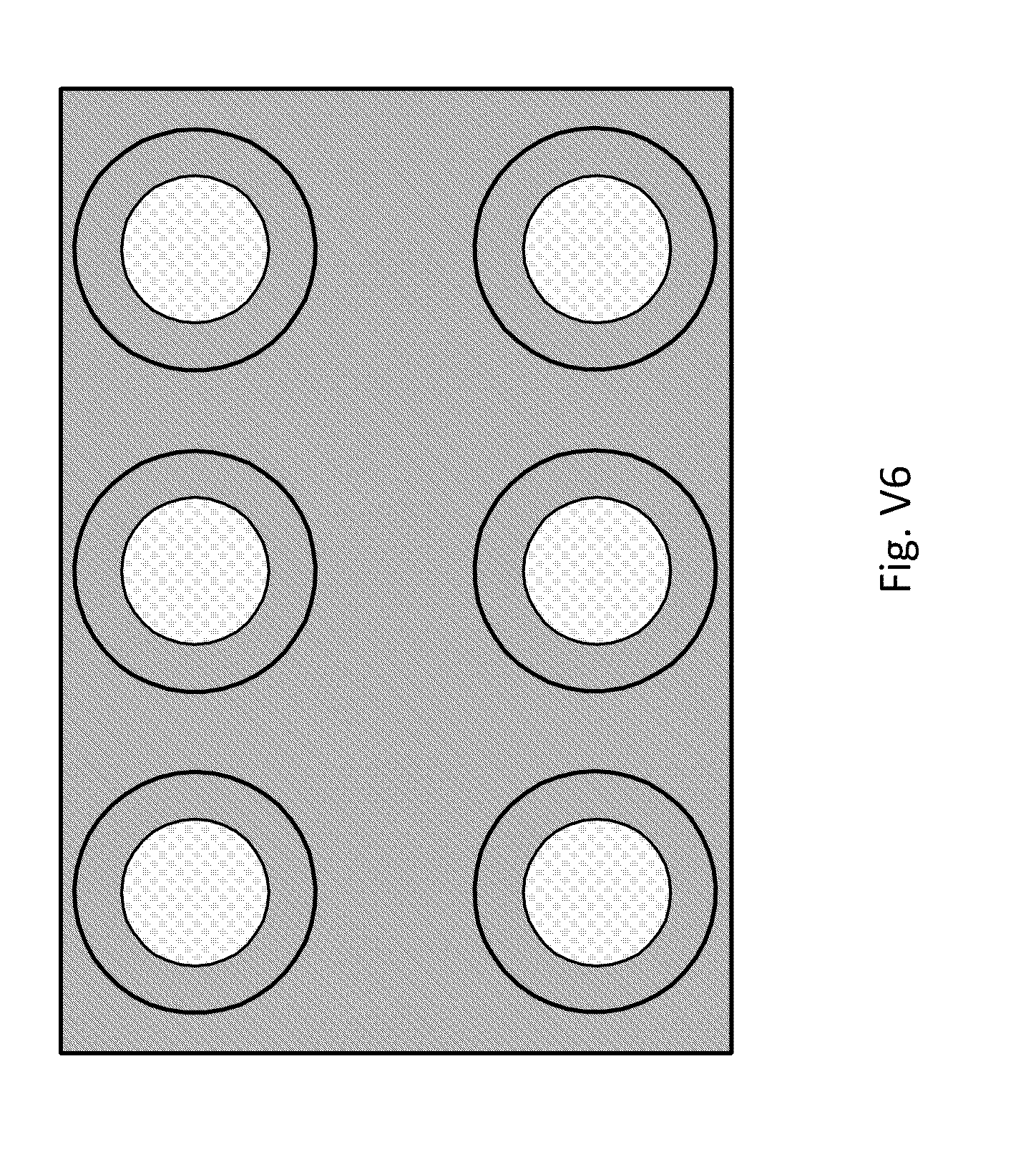

[0108] FIG. V6 shows an exemplary top cross sectional view of the photovoltaic device V200. FIG. V7 shows an exemplary perspective view of the photovoltaic device V200.

[0109] A method of converting light to electricity comprises: exposing the photovoltaic device V200 to light; reflecting light to the nanostructures 1 using the planar reflective layer V232; absorbing the light and converting the light to electricity using the nanostructures 1; drawing an electrical current from the photovoltaic device V200. As shown in FIG. V8B, the electrical current can be drawn from the metal layer V252 and/or the planar reflective layer V232 in the photovoltaic device V200.

[0110] FIG. W2A shows a schematic cross-section of a photovoltaic device W200, according to another embodiment. The photovoltaic device W200 comprises a substrate W205, a plurality of nanostructures 1 essentially perpendicular to the substrate W205, one or more recesses W230 between the nanostructures 1 and an electrode layer W280. Each recess W230 is filled with a transparent material W240. Each recess W230 has a sidewall W230a and a bottom wall W230b. The bottom wall W230b has a planar reflective layer W232. The sidewall W230a does not have any planar reflective layer. The transparent material W240 preferably has a surface coextensive with the top surface W220a of the nanostructures 1. The photovoltaic device W200 further comprises an electrode layer W280 disposed on the transparent material W240 and the nanostructures 1. The photovoltaic device W200 can further comprise a coupling layer W260 disposed on the electrode layer W280 and only directly above the top surface W220a.

[0111] The nanostructures 1 can have any cross-sectional shape. For example, the nanostructures 1 can be cylinders or prisms with elliptical, circular, rectangular, polygonal cross-sections. The nanostructures 1 can also be strips as shown in FIG. V9, or a mesh as shown in FIG. V10. According to one embodiment, the nanostructures 1 are pillars with diameters from 50 nm to 5000 nm, heights from 1000 nm to 20000 nm, a center-to-center distance between two closest pillars of 300 nm to 15000 nm. Preferably, the nanostructures 1 have an overhanging portion W224 along an entire contour of the top surface W220a of the nanostructures 1.

[0112] Each recess W230 preferably has a rounded or beveled inner edge between the sidewall W230a and the bottom wall W230b.

[0113] The planar reflective layer W232 can be any suitable material, such as ZnO, Al, Au, Ag, Pd, Cr, Cu, Ti, Ni, a combination thereof, etc. The planar reflective layer W232 preferably is an electrically conductive material, more preferably a metal. The planar reflective layer W232 preferably has a reflectance of at least 50%, more preferably has a reflectance of at least 70%, most preferably has a reflectance of at least 90%, for visible light of any wavelength. The planar reflective layer W232 has a thickness of preferably at least 5 nm, more preferably at least 20 nm. The planar reflective layer W232 in all the recesses W230 is preferably connected. The planar reflective layer W232 is functional to reflect light incident thereon to the nanostructures 1 so the light is absorbed by the nanostructures 1. The planar reflective layer W232 preferably is functional as an electrode of the photovoltaic device W200.

[0114] The transparent material W240 is substantially transparent to visible light, preferably with a transmittance of at least 50%, more preferably at least 70%, most preferably at least 90%. The transparent material W240 can be an electrically conductive material. The transparent material W240 preferably is made of a transparent conductive oxide, such as ITO (indium tin oxide), AZO (aluminum doped zinc oxide), ZIO (zinc indium oxide), ZTO (zinc tin oxide), etc. The transparent material W240 preferably forms an Ohmic contact with the heavily doped amorphous semiconductor layer 13 of the nanostructures 1. The transparent material W240 preferably forms an Ohmic contact with the planar reflective layer W232. The transparent material W240 preferably is functional as an electrode of the photovoltaic device W200. The transparent material W240 can also be a suitable electrically insulating material such as SiO.sub.2 or a polymer.

[0115] The substrate W205 preferably has a flat surface W250 opposite the nanostructures 1. The flat surface W250 can have a doped layer W251 of the opposite conduction type from the core 11 of the nanostructures 1, i.e. if the core 11 is n type, the doped layer W251 is p type; if the core 11 is p type, the doped layer W251 is n type. The doped layer W251 is electrically connected to each of the nanostructures 1. The flat surface W250 can also have a metal layer W252 disposed on the doped layer W251. The metal layer W252 forms an Ohmic contact with the doped layer W251. The substrate W205 preferably has a thickness of at least 50 microns. Total area of the planar reflective layer W232 is preferable at least 40% of a surface area of the flat surface W250.

[0116] The electrode layer W280 can be the same material as the transparent material W240 or different material from the transparent material W240. The electrode layer W280 is substantially transparent to visible light, preferably with a transmittance of at least 50%, more preferably at least 70%, most preferably at least 90%. The electrode layer W280 is an electrically conductive material. The electrode layer W280 preferably is a transparent conductive oxide, such as ITO (indium tin oxide), AZO (aluminum doped zinc oxide), ZIO (zinc indium oxide), ZTO (zinc tin oxide), etc. The electrode layer W280 preferably forms an Ohmic contact with the heavily doped amorphous semiconductor layer 13. The electrode layer W280 preferably is functional as an electrode of the photovoltaic device W200.

[0117] The coupling layer W260 can be the same material as the transparent material W240 or different material from the transparent material W240. As shown in FIG. W5, refractive index of the core 11 of the nanostructure 1 n.sub.1, refractive index of the transparent material W240 n.sub.2, refractive index of the coupling layer W260 n.sub.3, preferably satisfy relations of n.sub.1>n.sub.2 and n.sub.1>n.sub.3, which lead to enhanced light concentration in the nanostructures 1.

[0118] In one embodiment, the nanostructures 1 are pillars arranged in an array, such as a rectangular array, a hexagonal array, a square array, concentric ring. Each pillar is about 5 microns in height. A pitch of the nanostructures 1 is from 300 nm to 15 microns.

[0119] As shown in FIG. W11B, the photovoltaic device W200 can further comprise at least one via W599 in the transparent material W240 and between the electrode layer W280 and the planar reflective layer W232, wherein the at least one via W599 is an electrically conductive material, preferably an electrically conductive transparent material (e.g. ITO, AZO, etc.) and the at least one via electrically connects the electrode layer W280 and the planar reflective layer W232. As shown in FIG. W11A, the via W599 can be made by etching a recess W598 through the electrode layer W280 and the transparent material W240 until the planar reflective layer W232 is exposed and then filling the recess W598 to form the via W599. As shown in FIGS. W12A and W12B, the vias W599 can be any suitable shape such as rod-shaped or bar-shaped.

[0120] A method of converting light to electricity comprises: exposing the photovoltaic device W200 to light; reflecting light to the structures W220 using the planar reflective layer W232; absorbing the light and converting the light to electricity using the structures W220; drawing an electrical current from the photovoltaic device W200. As shown in FIG. W8B, the electrical current can be drawn from the metal layer W252 and the planar reflective layer W232, in the photovoltaic device W200.

[0121] According to an embodiment, a nanostrucuted LED with an optical feedback comprising a substrate, a nanostructure 1 in the form of a nanowire protruding from a first side the substrate, an active region to produce light, a optical sensor and a electronic circuit, wherein the optical sensor is configured to detect at least a first portion of the light produced in the active region, and the electronic circuit is configured to control an electrical parameter that controls a light output of the active region. The nanostructured LED in one example implementation, may further comprise a volume element epitaxially connected to the nanostructure 1. The volume element could provide a high doping degree for the formation of the active region, typically within or close to the nanostructure 1. Preferably, the nanostructured LED without optical feedback would be the combination of the substrate, the nanostructure 1 and a volume element, wherein a portion of the nanostructure 1 and a portion of the volume element are configured to form the active region. The volume element could be a cylindrical bulb, but is not limited to a cylindrical bulb with a dome-shaped top, a spherical/ellipsoidal, and pyramidal. The volume element can extend in three dimensions; can have a large volume, and a large surface. The volume element/nanostructure architecture enhances both electrical and optical performance of a LED. By using different material compositions in the nanostructure 1 and the volume element, the nanostructure 1 material composition can be chosen to propagate into the volume element in order to decrease the optical disturbance by the connection with the nanostructure 1.

[0122] The nanostructure 1, a part of the nanostructure 1, or a structure in connection with the nanostructure 1, could form a waveguide directing at least a portion of the light produced in the active region in a given direction.

[0123] The nanostructure 1 and the volume element could be embedded in a low index material like SiO.sub.2. In one possible implementation the low index region (e.g., a cover layer) is in turn enclosed by a cylindrical ring of metal to provide optical isolation of the each LED from its neighbors. This metal ring may also aid in the local removal of heat generated by each LED.

[0124] A nanostructured LED makes it possible to use a very large fraction of the light produced by the LED. This is at least partly achieved by the nanostructure 1 being used as a waveguide, directing the light produced in the junction out of the surface.

[0125] The use of the nanostructure 1 as a waveguide offers a possibility to direct light in well defined directions. By using concepts from the area of fiber optics light beams can be focused, or dispersed, depending on the intended use. In this case a concave surface on the nanostructure 1 and the silica surrounding it would help provide a focused beam of light suitable for a display system.

[0126] The nanostructured LED allows for inclusions of heterostructures as well as areas of different doping within the nanostructure 1, facilitating optimization of electrical and/or optical properties.

[0127] According to an embodiment, the nanostructured LED can comprise an optical feedback loop to create a uniformity of light emission for precise control of the light output of an LED or the uniformity of multiple LEDs arranged in a two dimensional grid for display purposes. Such a feedback loop would include an optical sensor to measure a fraction of the light output of the LED in real time and an electronic circuit to use the measurement to adjust the operating point of the LED.

[0128] An embodiment could include a nanostructured LED grown on a substrate that already has an embedded photodiode such as pinned photodiode. The light from the nanostructured LED is partially transmitted to the substrate where a photodiode measures and provides a signal proportional to the intensity of the light generated by the LED. This signal in turn is used in a feedback loop to control the bias point of the LED such that a stable light output is maintained at the desired intensity.

[0129] The nanostructured LED with optical feedback (NWLOF) could further comprise a partially reflective layer on the substrate surrounding and/or within the nanostructure 1, wherein the partially reflective layer is configured to allow a first portion of the light to transmit through the partially reflective layer to the optical sensor and to allow at least a second portion of the light to reflect from a surface of the partially reflective layer.

[0130] The NWLOF could further comprise one or more cladding layers surrounding the nanostructure 1, wherein the one or more cladding layers are configured such that the nanostructure 1 is configured to form a waveguide. The NWLOF could further comprise a low-index material having a lower refractive index surrounding the nanostructure 1 and a metal layer surrounding the low-index material.

[0131] The NWLOF could further comprise a volume element, wherein a portion of the nanostructure 1 and a portion of the volume element are configured to form the active region.

[0132] A nanostructured LED according to the embodiments comprises of an upstanding nanostructure 1. For the purpose of this application an upstanding nanostructure 1 should be interpreted as a nanostructure 1 protruding essentially perpendicularly from the substrate, the upstanding nanostructure 1 for example being grown from the substrate, preferably by as vapor-liquid-solid (VLS) grown nanostructures 1. The angle with the substrate will typically be a result of the materials in the substrate and the nanostructure 1, the surface of the substrate and growth conditions. By controlling these parameters it is possible to produce nanostructures 1 pointing in only one direction, for example vertical, or in a limited set of directions.

[0133] According to the embodiments, a part of the nanostructure 1 or structure formed from the nanostructure 1 could be used as a waveguide directing and confining at least a portion of the light created in the nanostructured LED in a direction given by the upstanding nanostructure 1. The waveguiding nanostructured LED structure could include a high refractive index nanostructure 1 with one or more surrounding cladding with refractive indices less than that of the nanostructure 1. The structure could be either circular symmetrical or close to being circular symmetrical. Light waveguiding in circular symmetrical structures are well know for fiber-optic applications and many parallels can be made to the area of rare-earth-doped fiber optic devices. However, one difference is that fiber amplifier are optically pumped to enhance the light guided through them while the described nanostructured LED can be seen as an efficient light to electricity converter and vice versa.

[0134] Preferably, an output of the optical sensor is an input to the electronic circuit. Preferably, the electrical parameter comprises voltage or current. Preferably, the electronic circuit is configured to control voltage or current such that the light output is maintained substantially constant irrespective of a temperature of the active region within an operating temperature range of the active region. Preferably, the optical sensor comprises a pn or p-i-n photodiode having a performance characteristic that is substantially insensitive to a temperature in an operating temperature range of the active region. Preferably, at least a portion of the light produced in the active region is directed in a direction given by the nanostructure 1. Preferably, the nanostructure 1 is configured to both produce light and form a waveguide.

[0135] Preferably, the volume element comprises a doping layer configured to provide a p or n region and a well layer. Preferably, the optical sensor comprises a pinned photodiode in the substrate. Preferably, the one or more cladding layers are configured to provide a graded refractive index such that a refractive index of the nanostructure 1 is higher than that of the one or more cladding layer. Preferably, the NWLOF comprises a plurality of the nanostructures 1 comprising different materials emit different ranges of wavelengths of the light. Preferably, the NWLOF comprises a plurality of the nanostructures 1 comprising different diameters that form waveguides for different ranges of wavelengths of the light. Preferably, the NWLOF comprises a plurality of the nanostructures 1 comprising different materials emit different ranges of wavelengths of the light and the NWLOF comprises a plurality of the nanostructures 1 comprising different diameters that form waveguides for different ranges of wavelengths of the light. Preferably, the nanostructure 1 and the volume element are arranged to direct the light through the nanostructure 1 and the substrate such that the light is emitted from a second side of the substrate opposite the first side. Preferably, the volume element is configured to spread the light by dispersion at a junction between the nanostructure 1 and the volume element. Preferably, the electronic circuit comprises a controller configured to calibrate the electrical parameter. Preferably, the controller comprises memory, the memory comprising values for controlling the electrical parameter so that the light output is set by the values stored in the memory. Preferably, the controller comprises memory; wherein the controller is configured to calibrate the electrical parameter to cause the light output to more closely match a target output based on target values of the light output stored in the memory. Preferably, the target values represent current values for different colors of the light. Preferably, the target values represent target brightness levels.

[0136] The waveguiding properties of the nanostructure 1 can be improved in different ways. The nanostructure 1 could have a first effective refractive index, n.sub.w, and a cladding surrounding at least a portion of the nanostructure 1 could have a second effective refractive index, n.sub.c, and by assuring that the first refractive index is larger than the second refractive index, n.sub.w>n.sub.c, good wave-guiding properties could be provided to the nanostructure 1. The waveguiding properties may be further improved by introducing an optically active cladding.

[0137] The high index material in the nanostructure 1 could, for example, be silicon nitride having a refractive index of about 2.0. The lower index cladding layer material could, for example, be a glass, plasma enhanced Si.sub.3N.sub.4, plasma enhanced SiO.sub.2, SiO.sub.2.

[0138] For a LED operating in different wavelengths from the visible to the IR and deep in the micrometer wavelengths, a variety of materials can be used, such as: Si, GaAs (p), InAs, Ge, ZnO, InN, GaInN, GaN AlGaInN, InP, InAsP, GaInP, InGaP:Si, InGaP:Zn, GaInAs, AlInP, GaAlInP, GaAlInAsP, GaInSb, InSb among others. To create CMOS circuits, Si and doped Si materials are preferable.

[0139] In one embodiment, the typical values of the refractive indexes for III-V semiconductor nanostructure 1 material are in the range from 2.5 to 5.5 when combined with glass type of cladding material (such as SiO.sub.2 or Si.sub.3N.sub.4) having refractive indexes ranging from 1.4 to 2.3, satisfying the waveguiding requirement, n.sub.w>n.sub.c.

[0140] One consideration in the optimization of light extraction is to make the Numerical Aperture (NA) vary along the nanostructure 1 structure to optimize light extraction from the structure. In general, it is ideal to have the NA be highest when the light generation takes place furthest away from the exit location. This will maximize the light captured and guided toward the exit, in contrast, closer to the exit end of the structure, the NA can be made smaller since light generated will radiate in random directions and most of the radiate light will hit the top and side of the top part of the structure and exit. Having a lower NA in the top part of the structure also minimizes the light captures and guide back down through the structure that may not be ideal unless a reflector is inserted in the bottom of the structure. A low NA can be obtained by surrounding the III-V nanostructure 1 core with another III-V cladding of different composition with slightly less refractive index.

[0141] A nanostructured LED according to some embodiments could comprise a substrate and a nanostructure 1 epitaxially grown from the substrate. A portion of the nanostructure 1 is enclosed by a volume element. The volume element is preferably epitaxially connected to the nanostructure 1. A portion of or all of the nanostructure 1 could be arranged to act as a waveguiding portion directing at least a portion of the impinging light in a direction given by the elongated direction of the nanostructure 1, and will be referred to as a waveguide. The nanostructure 1 could have a diameter in the order of 50 nm to 500 nm. The length of the nanostructure 1 could be of the order of 1 to 10 .mu.m.

[0142] The materials of the different members of the nanostructured LED are chosen so that the nanostructure 1 will have good waveguiding properties vis-a-vis the surrounding materials, i.e. the refractive index of the material in the nanostructure 1 should preferably be larger than the refractive indices of the surrounding materials.

[0143] If the nanostructure 1 has a first refracting index, n.sub.w, the material surrounding the nanostructure 1 in wave guide portion, typically a cover layer, a second refractive index, n.sub.c, and the a volume element, a third refractive n.sub.ve, then n.sub.w>n.sub.c and n.sub.w>n.sub.ve. Typical values for the nanostructured LED are n.sub.w.about.4, n.sub.c.about.1.5 and n.sub.ve.about.3.

[0144] In addition, the nanostructure 1 may be provided with one or more layers. For example an optical layer may be introduced specifically to improve the waveguiding properties of the nanostructure 1, in manners similar to what is well established in the area of fiber optics. The optical layer typically has a refractive index in between the refractive index of the nanostructure 1 and the surrounding cladding region material. Alternatively the intermediate layer has a graded refractive index, which has been shown to improve light transmission in certain cases. If an optical layer is utilized, the refractive index of the nanostructure 1, n.sub.w, should define an effective refractive index for both the nanostructure 1 and the layers.

[0145] The ability to grow nanostructures 1 with well defined diameters could be to optimize the waveguiding properties of the nanostructure 1 with regards to the wavelength of the light confined in the nanostructured LED. The diameter of the nanostructure 1 could be chosen so as to have a favorable correspondence to the wavelength of the desired light. Preferably the dimensions of the nanostructure 1 are such that a uniform optical cavity, optimized for the specific wavelength of the produced light, is provided along the nanostructure 1. The nanostructure 1 generally is sufficiently wide to capture the desired light. A rule of thumb would be that diameter must be larger than .lamda./2n.sub.w, wherein .lamda. is the wavelength of the desired light and n.sub.w is the refractive index of the nanostructure 1. As an example a diameter of about 60 nm may be appropriate to confine blue light only and one 80 nm may be appropriate for to confine both blue and green light in a silicon nanostructure 1.

[0146] In the infrared and near infrared a diameter above 100 nm would be sufficient. An approximate preferred upper limit for the diameter of the nanostructure 1 is given by the growth constrains, and could be in the order of 500 nm. The length of the nanostructure 1 is typically and preferably in the order of 1-10 .mu.m, providing enough volume for the active region.

[0147] A reflective layer could be in one embodiment, provided on the substrate and extending under the wire. The reflective layer is preferably provided in the form of a multilayered structure comprising repeated layers of silicates for example, or as a metal film.

[0148] An alternative approach to getting a reflection in the lower end of the nanostructure 1 could be to arrange a reflective layer in the substrate underneath the nanostructure 1. Yet another alternative could be to introduce reflective means within the waveguide. Such reflective means can be a multilayered structure provided during the growth process of the nanostructure 1, the multilayered structure comprising repeated layers of for example SiN.sub.x/SiO.sub.x (dielectric) or GaAs/AlGaAs (semiconductor). Such repeated layers with controlled thickness could also serve as optical grating filters to precisely control the output wavelength of the LED to mitigate wavelength drift for example with temperature.

[0149] In a further embodiment, a major part of the produced light is directed by the waveguide of the nanostructure 1 in a downward direction through the substrate. The light can be directed through the entire thickness of the substrate, or alternatively the substrate could be provided with a cut out beneath the base of the nanostructure 1 in order to reduce the thickness of the substrate and thereby reduce the scattering or absorption of light in the substrate. The substrate is preferably made of transparent material. A portion, or preferably the entire outer surface of the volume element may be covered by a reflective layer that increases the radiation of the produced light through the waveguide. The reflective layer, for example formed of a metal, may additionally serve as a contact. Part of the nanostructure 1 and the substrate could optionally covered by a protective layer of SiC or SiN, for example.

[0150] In an embodiment, the volume element can be arranged to be a dispersive element, giving a light radiation that is essentially evenly distributed over a wide angle. Such device can be well suited for illuminating purposes wherein an even illumination is required. The active region may be arranged in the nanostructure 1 but alternatively may be within the volume element, and above the upper end of the nanostructure 1, or radially outwards of the nanostructure 1 and possibly above. The nanostructure 1 should preferably at its lower end be provided with some of the reflective means, for example a reflective material within the nanostructure 1, in order to redirect light upwards. The geometry of the volume element can be designed to further disperse the light. Dispersion is provided at the junction between the nanostructure 1 waveguide and the volume element and further at the edge formed by the upper boundary of the volume element. The height and width of the volume element can be chosen so that the edge disperses light further. One embodiment can be optimized for providing a collected and directionally oriented beam. The nanostructure 1 of relatively large diameter, preferably above 150 nm, can extend to the upper surface of the volume element. The nanostructure 1 can be provided with a concave lens like exit surface on the upper end.

[0151] Nanostructures 1, acting as waveguides, can be used to improve the performance of conventional planar LEDs. In an embodiment, a plurality of nanostructures 1 can be arranged on the surface of a planar LED. Light is produced in the active region, which could be an active layer of the planar LED, for example of GaAsP. The nanostructures 1 can be epitaxially connected on top of the planar LED layers in order to get a good matching of the different parts. The nanostructures 1 may be coated by a cladding layer protecting the nanostructures 1 and/or improving the properties, for example Si.sub.3N.sub.4, The surface in between the nanostructures 1 can be preferably coated with a reflective layer, for example of Au. At least a part of the light, produced in the active region, could enter the nanostructures 1 that are acting as waveguides and leading the light away from the substrate plane.

[0152] A wide range of materials can be used for the different parts of the nanostructured LED. Suitable materials for LED have to be matched with suitable materials for the photo diodes based on the wavelength of the light being emitted/detected by the system. Both the LED and the photo diode should work as intended in the wavelength range of light for which the system is configured to operate.

[0153] In addition, the nanostructure 1 based technology allows for defect free combinations of materials that otherwise would be impossible to combine. The III-V semiconductors are of particular interest due to their properties facilitating high speed and low power electronics. Suitable materials for the substrate include, but is not limited to: Si, GaAs, GaP, GaP:Zn, InAs, InP, GaN, Al.sub.2O.sub.3, SiC, Ge, GaSb, ZnO, InSb, SOI (silicon-on-insulator), CdS, ZnSe, CdTe. In the case of the present invention (i.e. for creating display structure in the visible light), a Si substrate is preferred since it embeds a CMOS photodiode underneath the LED. For wavelengths between blue and near IR, Si could be used in the photo diode. For wavelengths outside the range of light detected by Si, such as IR or UV light, it is possible to use GaAs in photodiodes for LED in the range of 800-1500 nm, e.g., 850 nm; and InGaAs/InP in the range 1310-1550 nm.