Excelli Con!!!!

# **TIMING & LOGICAL EQUIVALENCY**

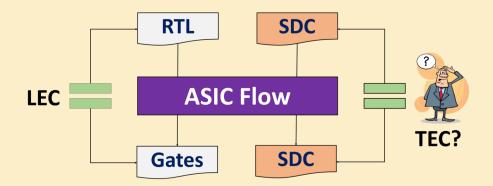

- Chip design comprises of:

- Functionality

- Timing

- No one tapes out without LEC

- Why not TEC?

**Timing Equivalence Checking**

**Extremely Dangerous to Tapeout Chip without running TEC**

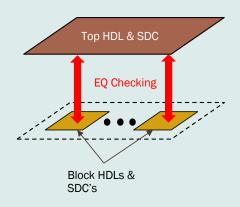

# **EQUIVALENCY & INSYNC CHECKING**

### Top2Block

Checks Equivalency of Top level SDC against Block level SDC's

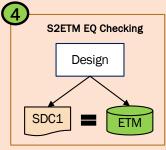

SDC to ETM equivalency checking

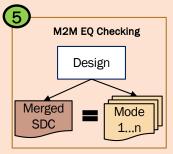

Merged SDC to Multiple Mode SDC equivalency checking

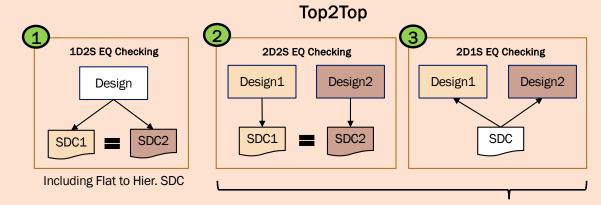

#### 2D2S & 2D1S

Includes support for the InSync Feature Example of InSync: Effect of timing constraints after design undergoes:

- ✓ Cloning

- ✓ Decloning/Merging

- ✓ Optimization out cells

- ✓ Buffering

- ✓ Pin Swapping

- ✓ Logical Structuring

- ✓ ECO Changes

### LOGICAL RESTRUCTURING WITH BOUNDARY OPTIMIZATION

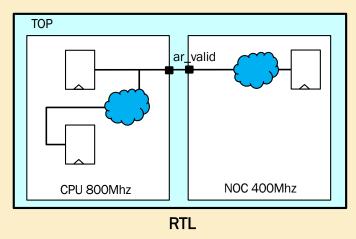

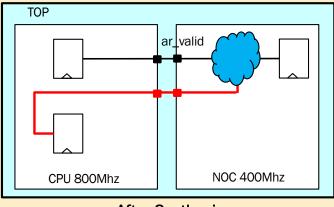

- CPU clock is 800Mhz, NOC is 400MHz

- Paths between CPU & NOC are multicycle

set\_multicycle\_path 2 -through noc/ar\_valid

**After Synthesis**

SDC generated after synthesis had the same -through multicycle

Synthesis created new ports and the path that was previously internal to the CPU is now going through the NOC *ar\_valid* port and is also MCP'd

### **CLONING ON DATAPATH**

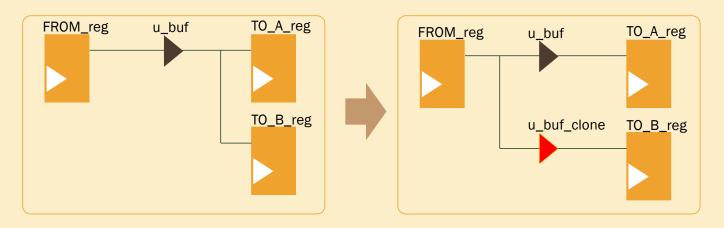

set\_multicycle\_path -start 2 -setup -through [get\_cells u\_buf]

#### **Before**

FROM\_reg -> TO\_A\_reg = setup:2 (multicycle path)

FROM\_reg -> TO\_B\_reg = setup:2 (multicycle path)

#### After

FROM\_reg -> TO\_A\_reg = setup:2 (multicycle path)

FROM\_reg -> TO\_B\_reg = setup:1

Use variable cloning\_map\_pins or cloning\_map\_cells to specify cloned pins/cells

## **PIN SWAPPING**

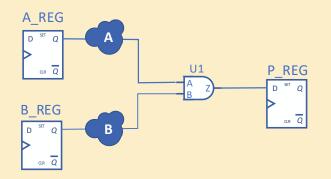

set\_false\_path -through U1/A

All paths from A\_REG to P\_REG are False

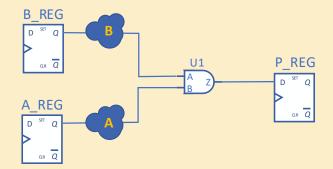

set\_false\_path -through U1/A

All paths from **B\_REG** to P\_REG are False