Single transducer audio in/out device

Price , et al. April 12, 2

U.S. patent number 11,304,002 [Application Number 16/947,687] was granted by the patent office on 2022-04-12 for single transducer audio in/out device. This patent grant is currently assigned to SIGMASENSE, LLC.. The grantee listed for this patent is SIGMASENSE, LLC.. Invention is credited to Patrick Troy Gray, Phuong Huynh, John Christopher Price, Daniel Keith Van Ostrand.

View All Diagrams

| United States Patent | 11,304,002 |

| Price , et al. | April 12, 2022 |

Single transducer audio in/out device

Abstract

An audio in/out device includes an audible in/out transducer operable to convert an audible input signal to an audio receive (RX) signal and convert an audio transmit (TX) signal to an audible output signal. The audio in/out device further includes an audio receive/transmit (RX/TX) circuit operable to convert a digital TX signal to the audio TX signal for transmission to the audible in/out transducer, receive the audio RX signal from the audible in/out transducer, and convert the audio RX signal into a digital transmit/receive (Tx/Rx) signal. The digital Tx/Rx signal includes a representation of the audio RX signal.

| Inventors: | Price; John Christopher (Austin, TX), Huynh; Phuong (Fairfax, VA), Van Ostrand; Daniel Keith (Leander, TX), Gray; Patrick Troy (Cedar Park, TX) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Applicant: |

|

||||||||||

| Assignee: | SIGMASENSE, LLC. (Wilmington,

DE) |

||||||||||

| Family ID: | 1000006231836 | ||||||||||

| Appl. No.: | 16/947,687 | ||||||||||

| Filed: | August 12, 2020 |

Prior Publication Data

| Document Identifier | Publication Date | |

|---|---|---|

| US 20220053269 A1 | Feb 17, 2022 | |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H03M 1/001 (20130101); H04R 1/2803 (20130101); H04R 3/04 (20130101) |

| Current International Class: | H03G 5/00 (20060101); H03M 1/00 (20060101); H04R 3/04 (20060101); H04R 1/28 (20060101); H04R 3/00 (20060101) |

| Field of Search: | ;381/98,96 |

References Cited [Referenced By]

U.S. Patent Documents

| 6218972 | April 2001 | Groshong |

| 6665013 | December 2003 | Fossum et al. |

| 7528755 | May 2009 | Hammerschmidt |

| 8031094 | October 2011 | Hotelling |

| 8089289 | January 2012 | Kremin et al. |

| 8279180 | October 2012 | Hotelling et al. |

| 8547114 | October 2013 | Kremin |

| 8587535 | November 2013 | Oda et al. |

| 8625726 | January 2014 | Kuan |

| 8982097 | March 2015 | Kuzo et al. |

| 9201547 | December 2015 | Elias |

| 2010/0177846 | July 2010 | Rofougaran |

| 2011/0063154 | March 2011 | Hotelling et al. |

| 2011/0298745 | December 2011 | Souchkov |

| 2012/0278031 | November 2012 | Oda |

| 2013/0278447 | October 2013 | Kremin |

| 2014/0327644 | November 2014 | Mohindra |

| 2015/0091847 | April 2015 | Chang |

| 2015/0346889 | December 2015 | Chen |

| 2016/0182989 | June 2016 | Kim |

| 2016/0188049 | June 2016 | Yang et al. |

| 103995626 | Aug 2014 | CN | |||

| 104182105 | Dec 2014 | CN | |||

Other References

|

Baker; How delta-sigma ADCs work, Part 1; Analog Applications Journal; Oct. 1, 2011; 6 pgs. cited by applicant . Brian Pisani, "Digital Filter Types in Delta-Sigma ADCs", Application Report SBAA230, May 2017, pp. 1-8, Texas Instruments Incorporated, Dallas, Texas. cited by applicant. |

Primary Examiner: Hamid; Ammar T

Attorney, Agent or Firm: Garlick & Markison Markison; Timothy W. Healy; Patricia M.

Claims

What is claimed is:

1. An audio in/out device comprises: an audible in/out transducer operable to: convert an audible input signal to an audio receive (RX) signal; and convert an audio transmit (TX) signal to an audible output signal; and an audio receive/transmit (RX/TX) circuit including: a digital to analog converter module operable to convert the digital TX signal to an analog TX reference signal; an operational amplifier operable to compare an audible in/out transducer voltage with the analog TX reference signal to a produce an analog comparison signal; a feedback circuit operable to convert the analog comparison signal to an analog regulation signal; a controlled source circuit operable to provide the audio TX signal to the audible in/out transducer based on the regulation signal, wherein the audio TX signal is adjusted based on the regulation signal in order to keep the audible in/out transducer voltage and the analog TX reference signal substantially matching; and an analog to digital converter operable to convert the analog comparison signal to the digital Tx/Rx signal, wherein the digital Tx/Rx signal includes a representation of the audio RX signal.

2. The audio in/out device of claim 1 further comprises: an audio codec module operable to: convert the digital Tx/Rx signal into a digital inbound signal in accordance with a desired inbound audio file format; and convert a digital outbound signal having an outbound audio file format into the digital TX signal.

3. The audio in/out device of claim 2, wherein the audio codec module comprises: an audio file formatting module operable to: convert the digital outbound signal into the digital TX signal; and convert a digital RX signal into the digital inbound signal; a summing circuit operable to subtract a delayed digital TX signal from the digital Tx/Rx signal to produce the digital RX signal; and a delay circuit operable to: determine the delayed digital TX signal based on the digital TX signal; and provide the delayed digital TX signal to the summing circuit.

4. The audio in/out device of claim 2, wherein the audio codec module further comprises: a level adjust circuit operable to adjust magnitude of the digital TX signal.

5. The audio in/out device of claim 2 further comprises: an interface module coupled to the audio codec module, wherein the interface module is operable to: transmit the digital inbound signal in accordance with an inbound communication protocol; and receive the digital outbound signal in accordance with an outbound communication protocol.

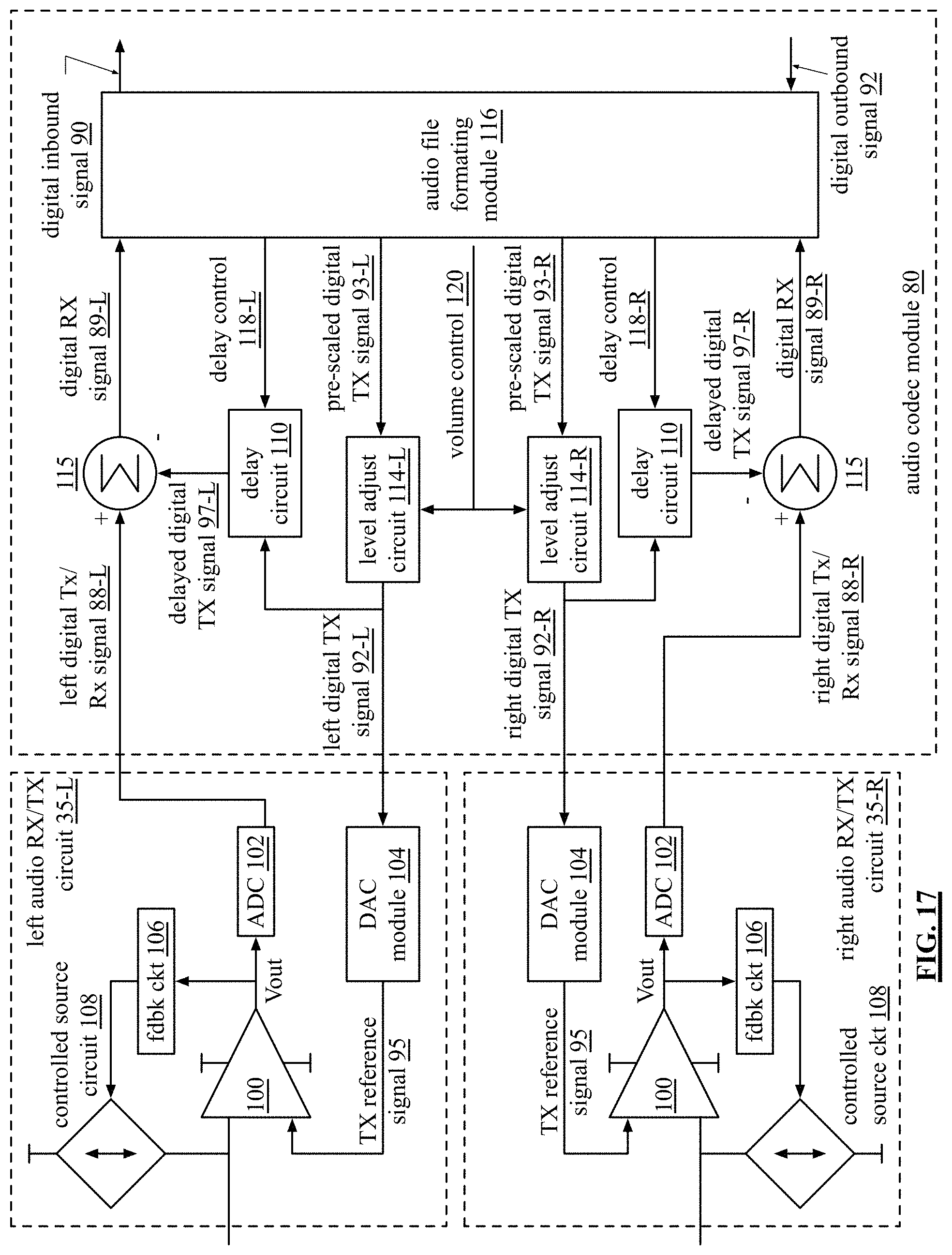

6. The audio in/out device of claim 1 further comprises: a left audible in/out transducer operable to: convert a left audible input signal to a left audio receive (RX) signal; and convert a left audio transmit (TX) signal to a left audible output signal; and a left audio receive/transmit (RX/TX) circuit operable to: convert a left digital TX signal to the left audio TX signal for transmission to the left audible in/out transducer; receive the left audio RX signal from the left audible in/out transducer; and convert the left audio RX signal into a left digital transmit/receive (Tx/Rx) signal, wherein the left digital Tx/Rx signal includes a representation of the left audio RX signal; and a right audible in/out transducer operable to: convert a right audible input signal to a right audio receive (RX) signal; and convert a right audio transmit (TX) signal to a right audible output signal; and a right audio receive/transmit (RX/TX) circuit operable to: convert a right digital TX signal to the right audio TX signal for transmission to the right audible in/out transducer; receive the right audio RX signal from the right audible in/out transducer; and convert the right audio RX signal into a right digital transmit/receive (Tx/Rx) signal, wherein the right digital Tx/Rx signal includes a representation of the right audio RX signal.

7. The audio in/out device of claim 6, wherein the right audio TX signal and the left audio TX signal include different audio information.

8. The audio in/out device of claim 7, wherein the right audio TX signal and the left audio TX signal include substantially matching audio information.

9. An audio in/out device comprises: an audible in/out transducer operable to: convert an audible input signal to an audio receive (RX) signal; and convert an audio transmit (TX) signal to an audible output signal; and an audio receive/transmit (RX/TX) circuit operable to: convert an analog TX reference signal to the audio TX signal for transmission to the audible in/out transducer; receive the audio RX signal from the audible in/out transducer; and convert the audio RX signal into an analog comparison signal, wherein the analog comparison signal includes a representation of the audio RX signal; and an audio codec module operable to: convert the analog comparison signal into a digital inbound signal in accordance with a desired inbound audio file format; and convert a digital outbound signal having an outbound audio file format into the analog TX reference signal.

10. The audio in/out device of claim 9, wherein the audio RX/TX circuit comprises: an operational amplifier operable to compare an audible in/out transducer voltage with the analog TX reference signal to produce the analog comparison signal; a feedback circuit operable to convert the analog comparison signal to an analog regulation signal; and a controlled source circuit operable to adjust the audio TX signal provided to the audible in/out transducer based on the analog regulation signal in order to keep the audible in/out transducer voltage and the analog TX reference signal substantially matching.

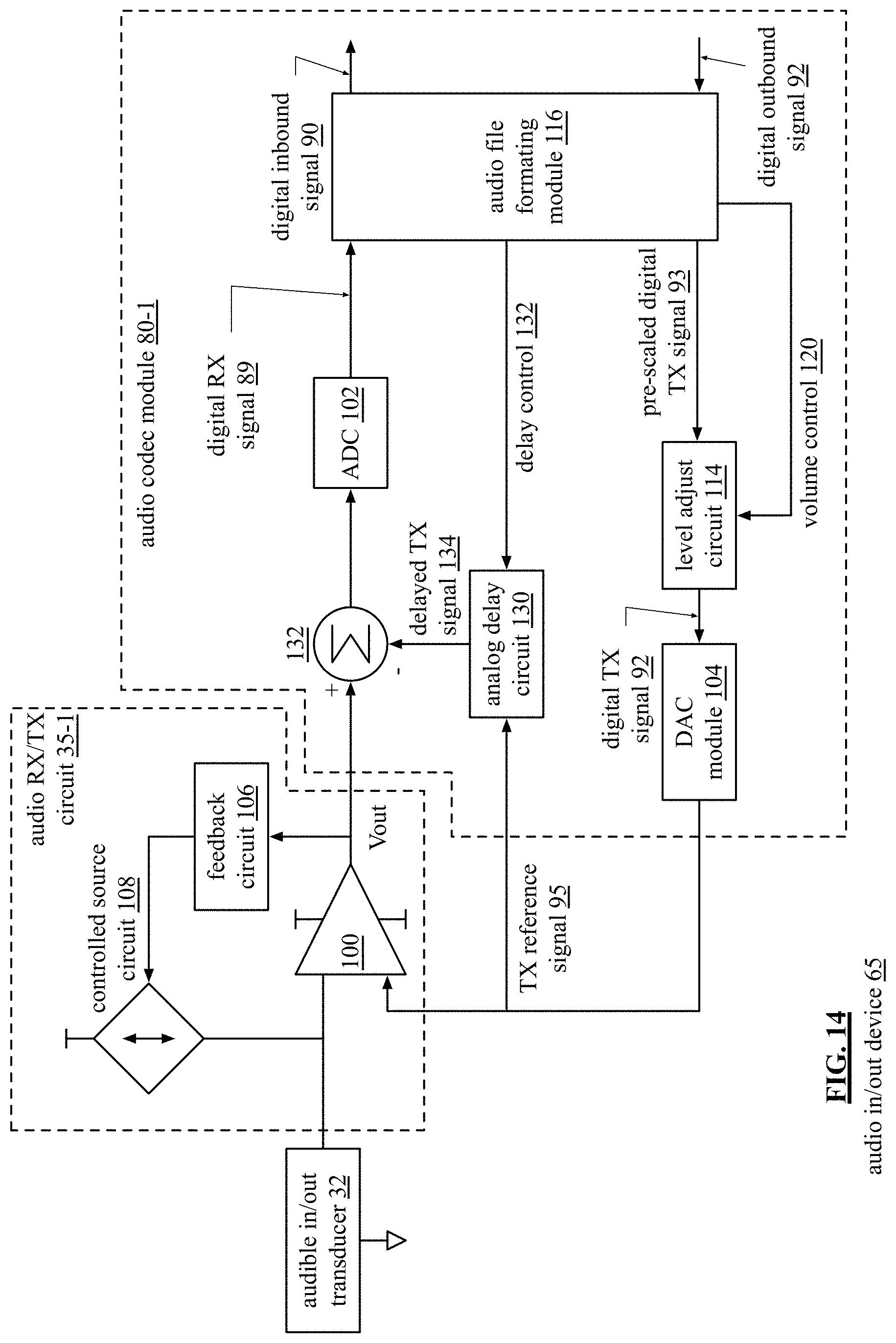

11. The audio in/out device of claim 9, wherein the audio codec module comprises: an audio file formatting module operable to convert the digital outbound signal into a digital TX signal; a digital to analog converter module operable to convert the digital TX signal into the analog TX reference signal; a summing circuit operable to subtract a delayed TX signal from the analog comparison signal to produce an analog receive signal; an analog delay circuit operable to: determine the delayed TX signal based on the digital TX signal; and provide the delayed TX signal to the summing circuit; and an analog to digital converter operable to convert the analog receive signal to a digital receive signal, wherein the audio file formatting module is further operable to convert the digital receive signal into the digital inbound signal in accordance with the desired inbound audio file format.

12. The audio in/out device of claim 11, wherein the audio codec module further comprises: a level adjust circuit operable to control magnitude of the digital TX signal.

13. The audio in/out device of claim 9 further comprises: an interface module coupled to the audio codec module, wherein the interface module is operable to: transmit the digital inbound signal in accordance with an inbound communication protocol; and receive the digital outbound signal in accordance with an outbound communication protocol.

14. The audio in/out device of claim 9 further comprises: a left audible in/out transducer operable to: convert a left audible input signal to a left audio receive (RX) signal; and convert a left audio transmit (TX) signal to a left audible output signal; and a left audio receive/transmit (RX/TX) circuit operable to: convert a left analog TX reference signal to the left audio TX signal for transmission to the left audible in/out transducer; receive the left audio RX signal from the left audible in/out transducer; and convert the left audio RX signal into a left analog comparison signal, wherein the left analog comparison signal includes a representation of the left audio RX signal; and a right audible in/out transducer operable to: convert a right audible input signal to a right audio receive (RX) signal; and convert a right audio transmit (TX) signal to a right audible output signal; and a right audio receive/transmit (RX/TX) circuit operable to: convert a right analog TX reference signal to the right audio TX signal for transmission to the right audible in/out transducer; receive the right audio RX signal from the right audible in/out transducer; and convert the right audio RX signal into a right analog comparison signal, wherein the right analog comparison signal includes a representation of the right audio RX signal; and the audio codec module operable to: convert the left and right analog comparison signals into left and right digital inbound signals in accordance with the desired inbound audio file format; and convert a stereo digital outbound signal having a stereo outbound audio file format into the left and right analog TX reference signals.

15. The audio in/out device of claim 14, wherein the left and right analog TX reference signals include substantially matching audio information.

16. The audio in/out device of claim 14, wherein the left and right analog TX reference signals include different audio information.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

Not Applicable.

STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

Not Applicable.

INCORPORATION-BY-REFERENCE OF MATERIAL SUBMITTED ON A COMPACT DISC

Not Applicable.

BACKGROUND OF THE INVENTION

Technical Field of the Invention

This invention relates generally to communication systems and more particularly to a single transducer audio in/out device of a communication system.

Description of Related Art

Data communication involves sending data from one device to another device via a communication medium (e.g., a wire, a trace, a twisted pair, a coaxial cable, air, etc.). The devices range from dies within an integrated circuit (IC), to ICs on a printed circuit board (PCB), to PCBs within a computer, to computers, to networks of computers, and so on.

Data is communicated via a wired and/or a wireless connection and is done so in accordance with a data communication protocol. Data communication protocols dictate how the data is to be formatted, encoded/decoded, transmitted, and received. For example, a wireless data communication protocol such as IEEE 802.11 dictates how wireless communications are to be done via a wireless local area network. As another example, Sony/Philips Digital Interface Format (SPDIF) dictates how digital audio signals are transmitted and received. As yet another example, Inter-Integrated Circuit (I.sup.2C) is a two-wire serial protocol to connect devices such as microcontrollers, digital to analog converters, analog to digital converters, peripheral devices to a computer, and so on.

In addition, data communication protocols dictate how transmission errors are to be handled. For example, wireless communications often experience data errors, so the protocol dictates a form of forward error correction (e.g., Reed Solomon encoding, Turbo encoded, etc.) be used. As another example, wired communications experience much less data errors than wireless communications so the protocol dictates a form of feedback error correction (e.g., resend request, etc.) be used.

For some data communications, digital data is modulated with an analog carrier signal and transmitted/received via a modulated radio frequency (RF) signal. For other data communications, the digital data is transmitted "as is" via a wire or metal trace on a PCB. Regardless of the data communication protocol, digital data is in binary form where a logic "1" value is represented by a voltage that is at least 90% of the positive rail voltage and a logic "0" is represented by a voltage it is at most 10% of the negative rail voltage.

BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING(S)

The patent or application file contains at least one drawing executed in color. Copies of this patent or patent application publication with color drawing(s) will be provided by the Office upon request and payment of the necessary fee.

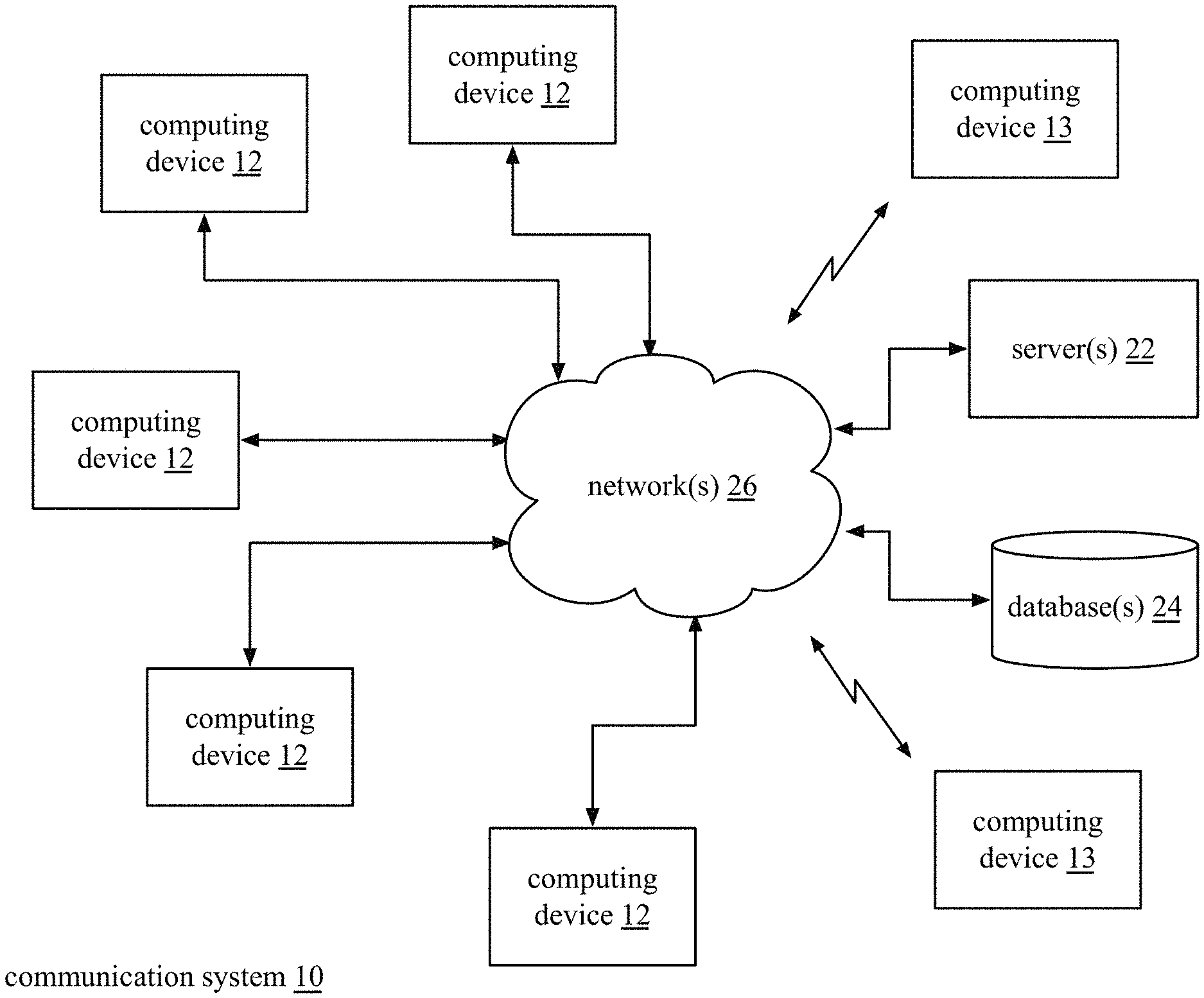

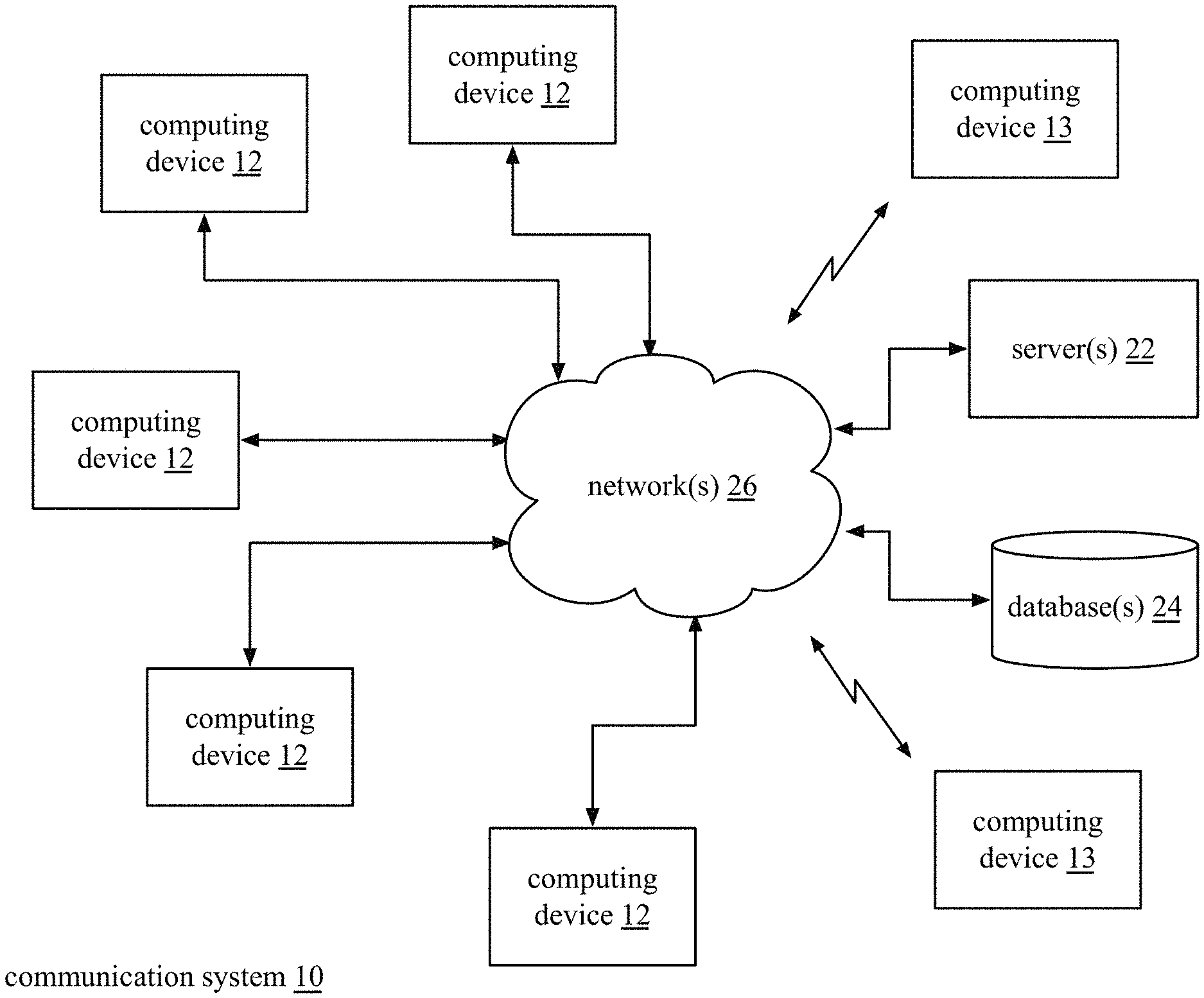

FIG. 1 is a schematic block diagram of an embodiment of a communication system in accordance with the present invention;

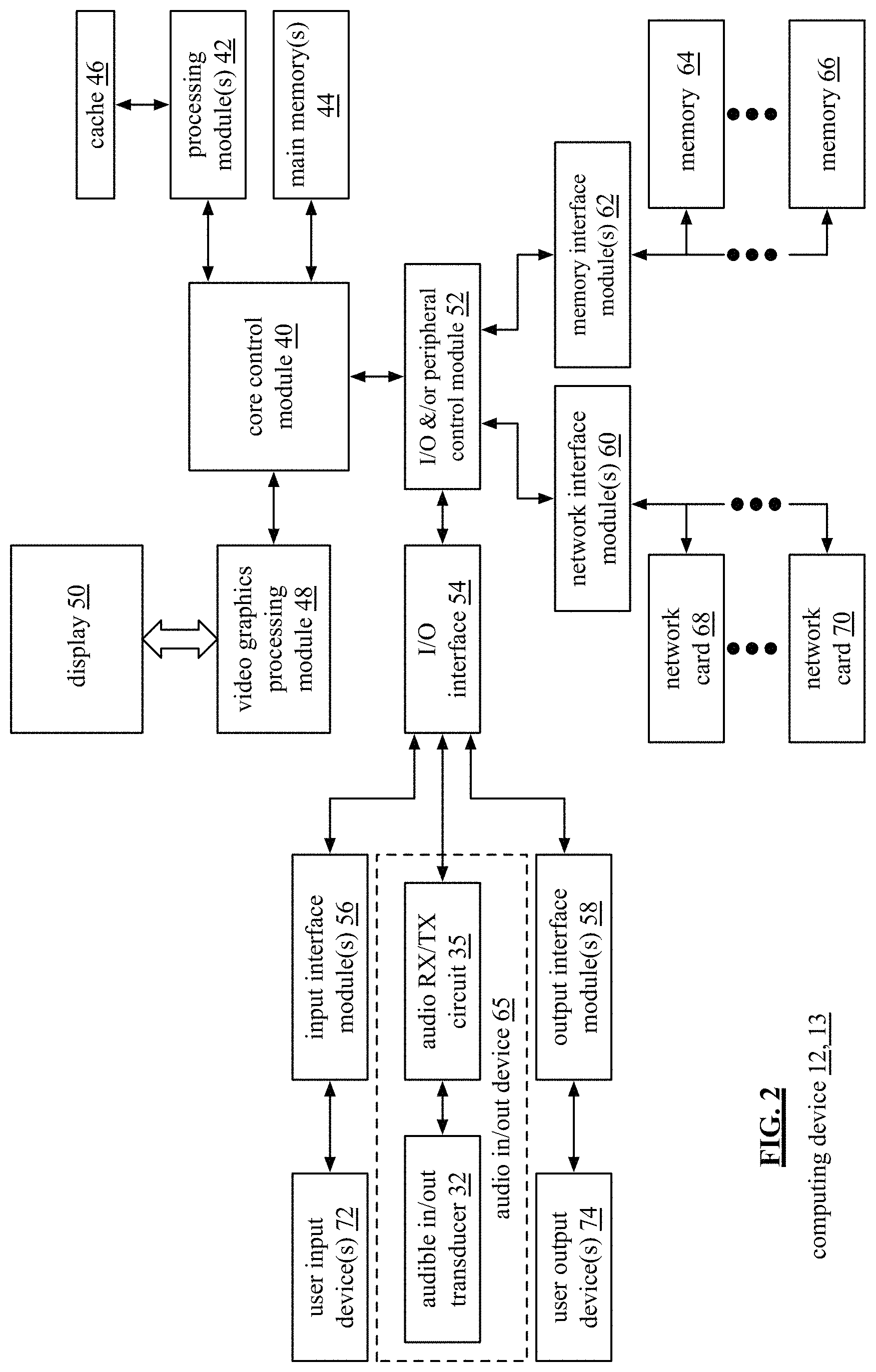

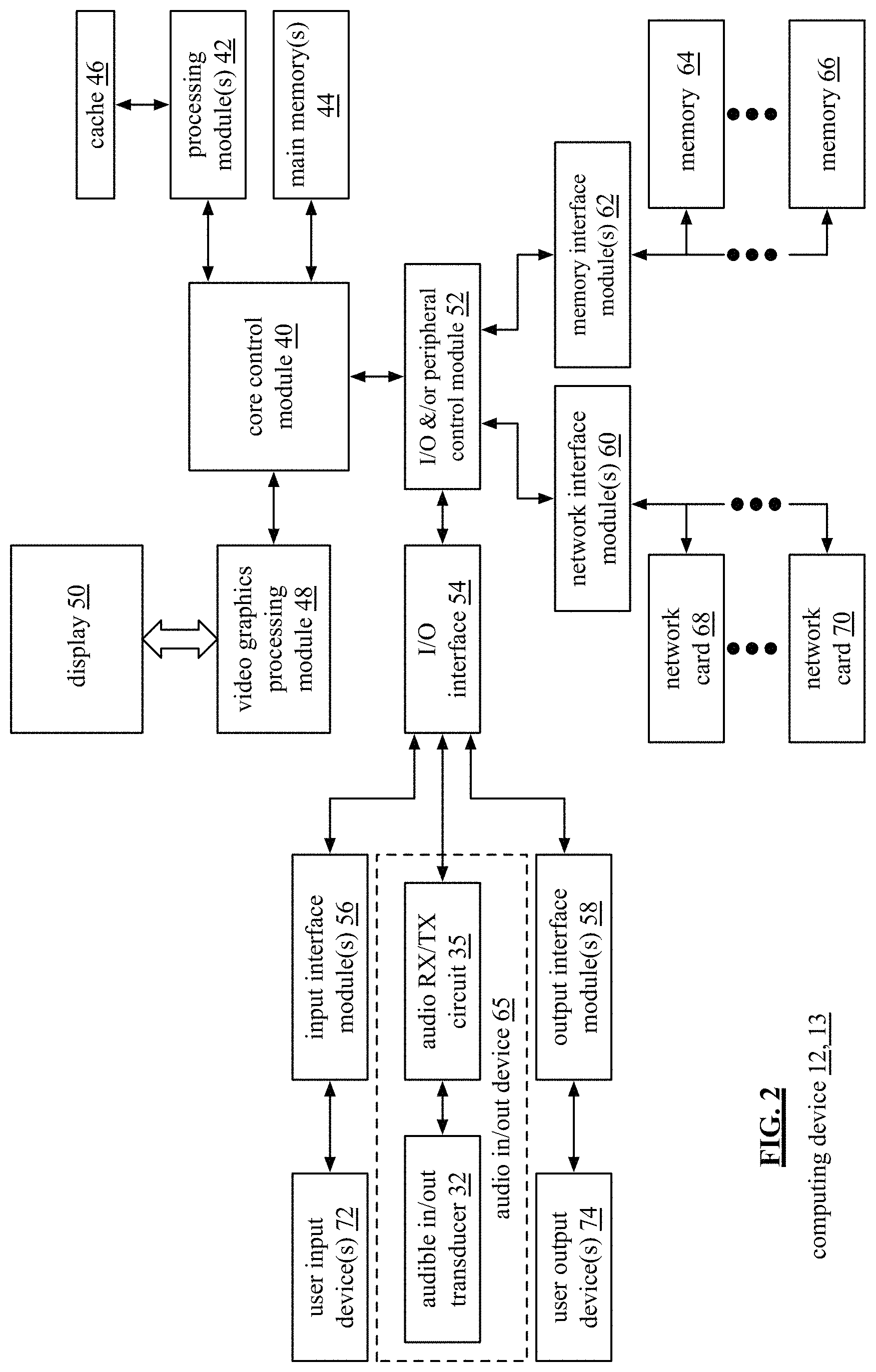

FIG. 2 is a schematic block diagram of an embodiment of a computing device in accordance with the present invention;

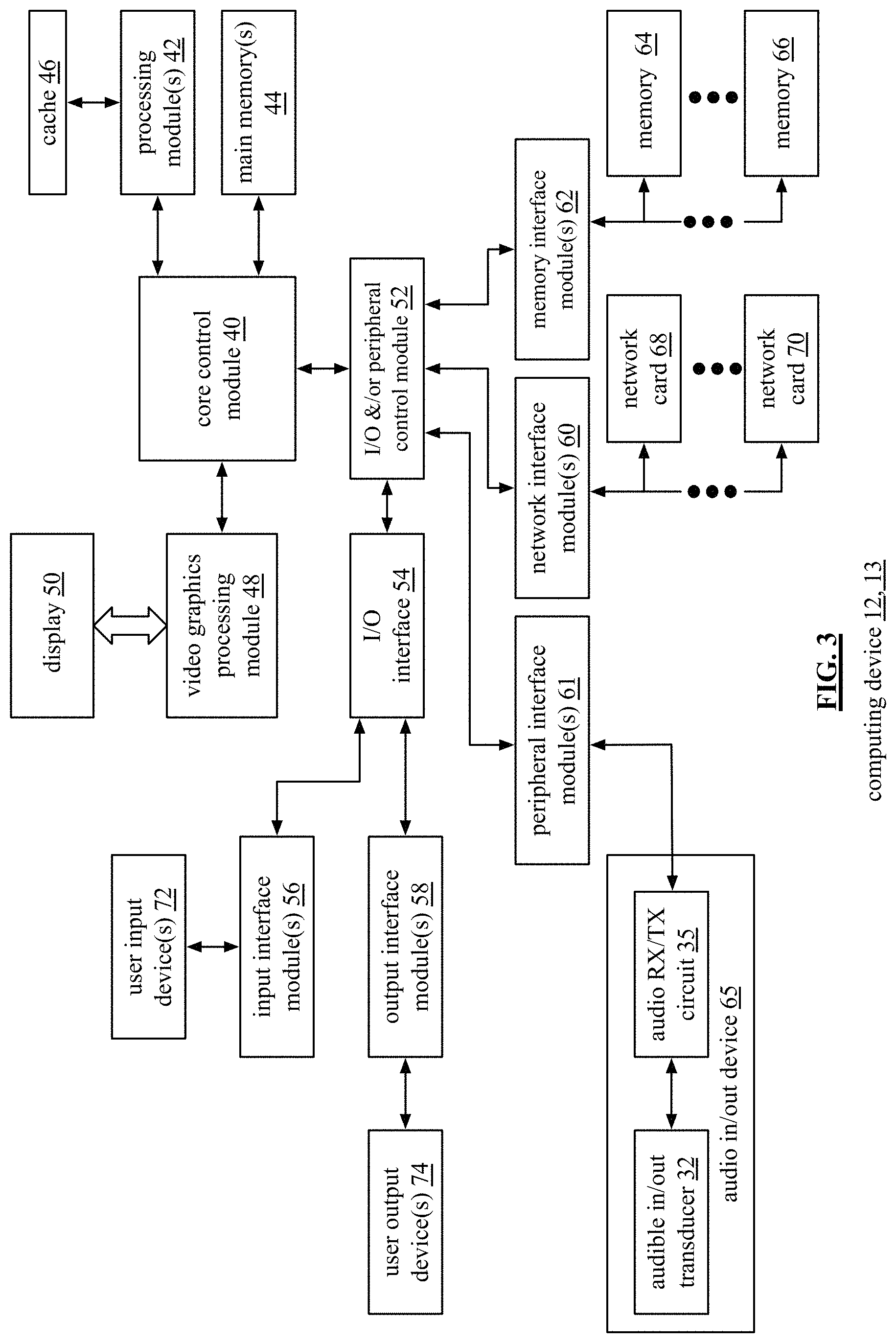

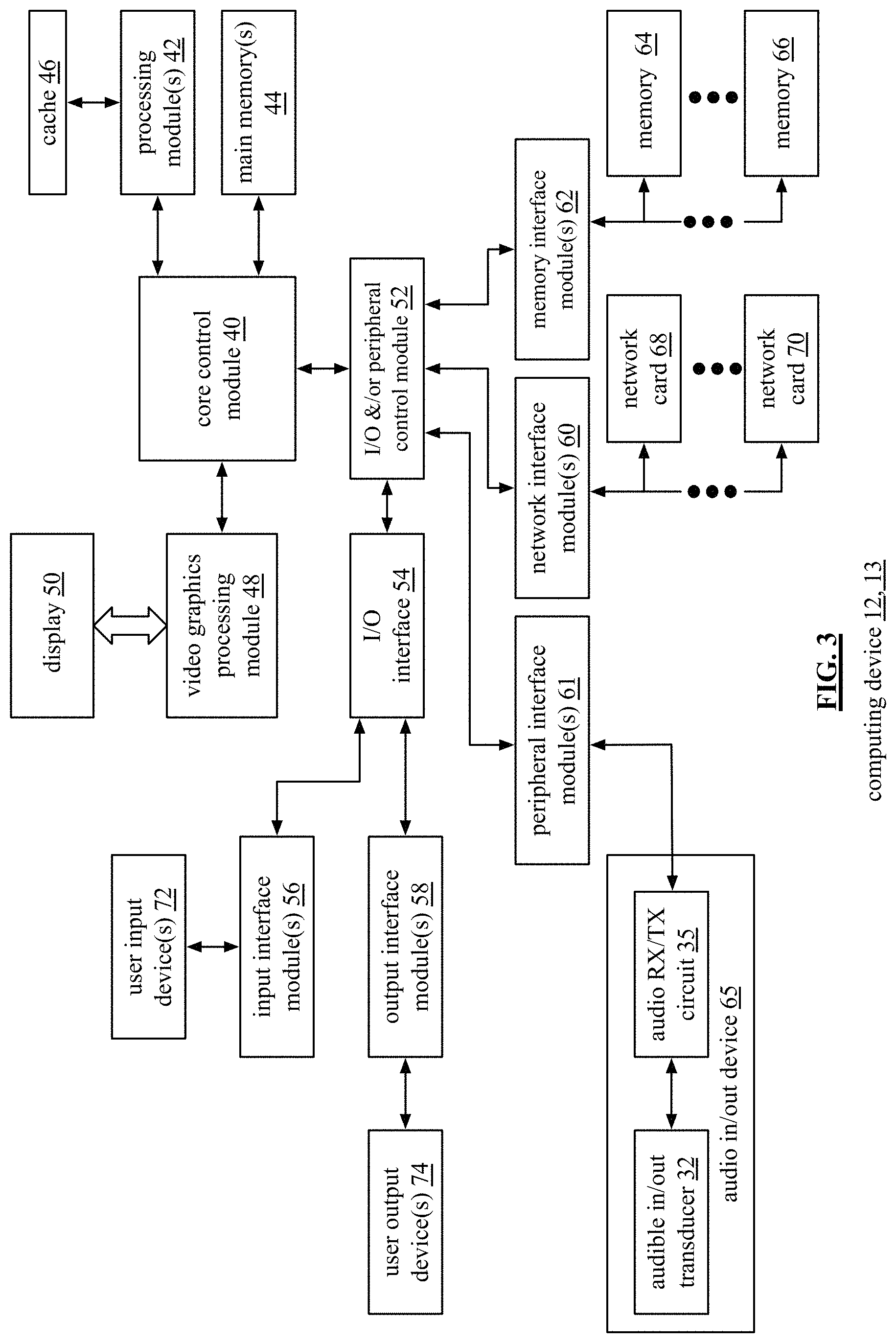

FIG. 3 is a schematic block diagram of another embodiment of a computing device in accordance with the present invention;

FIG. 3A is a schematic block diagram of another embodiment of a computing device in accordance with the present invention;

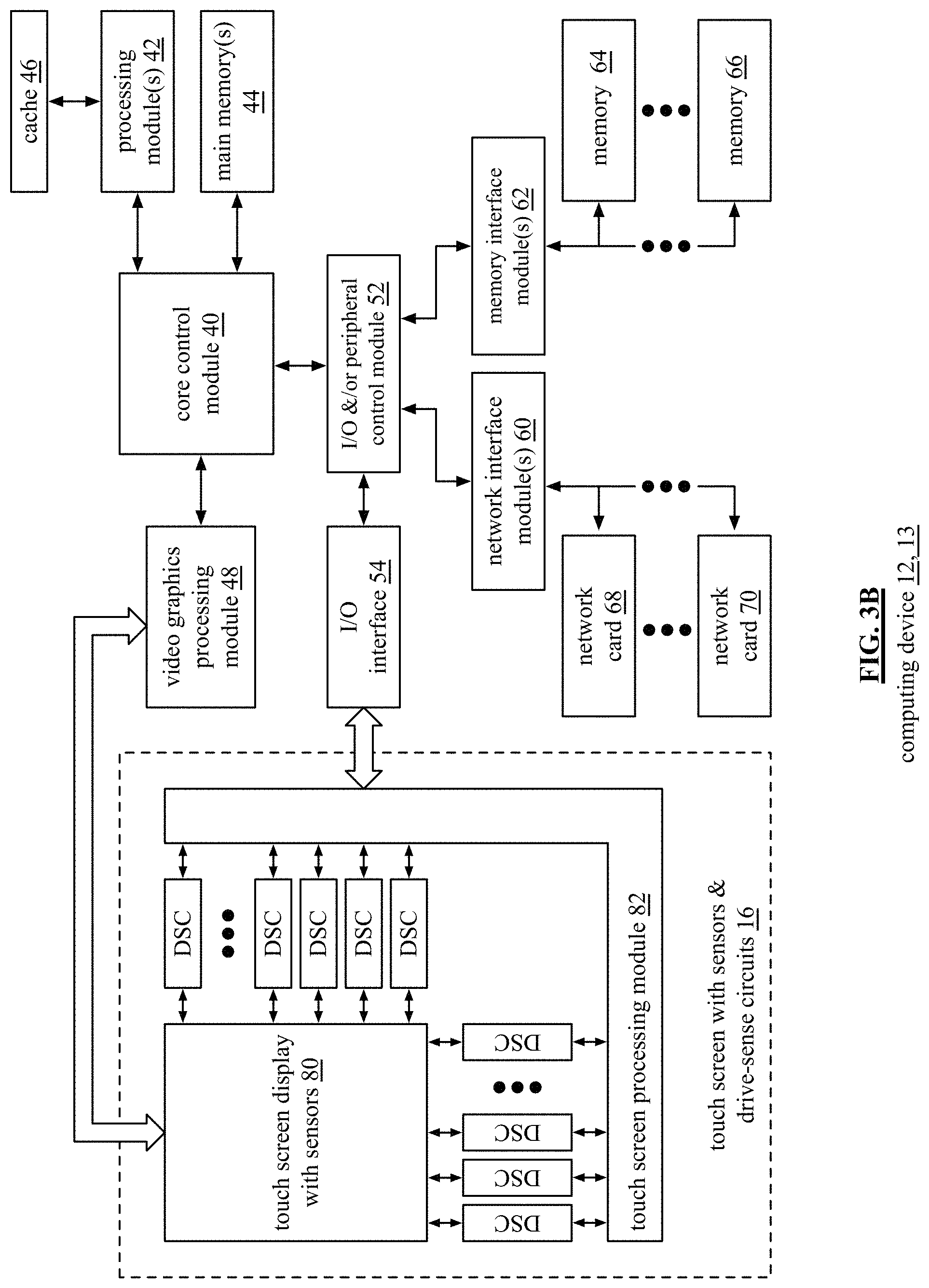

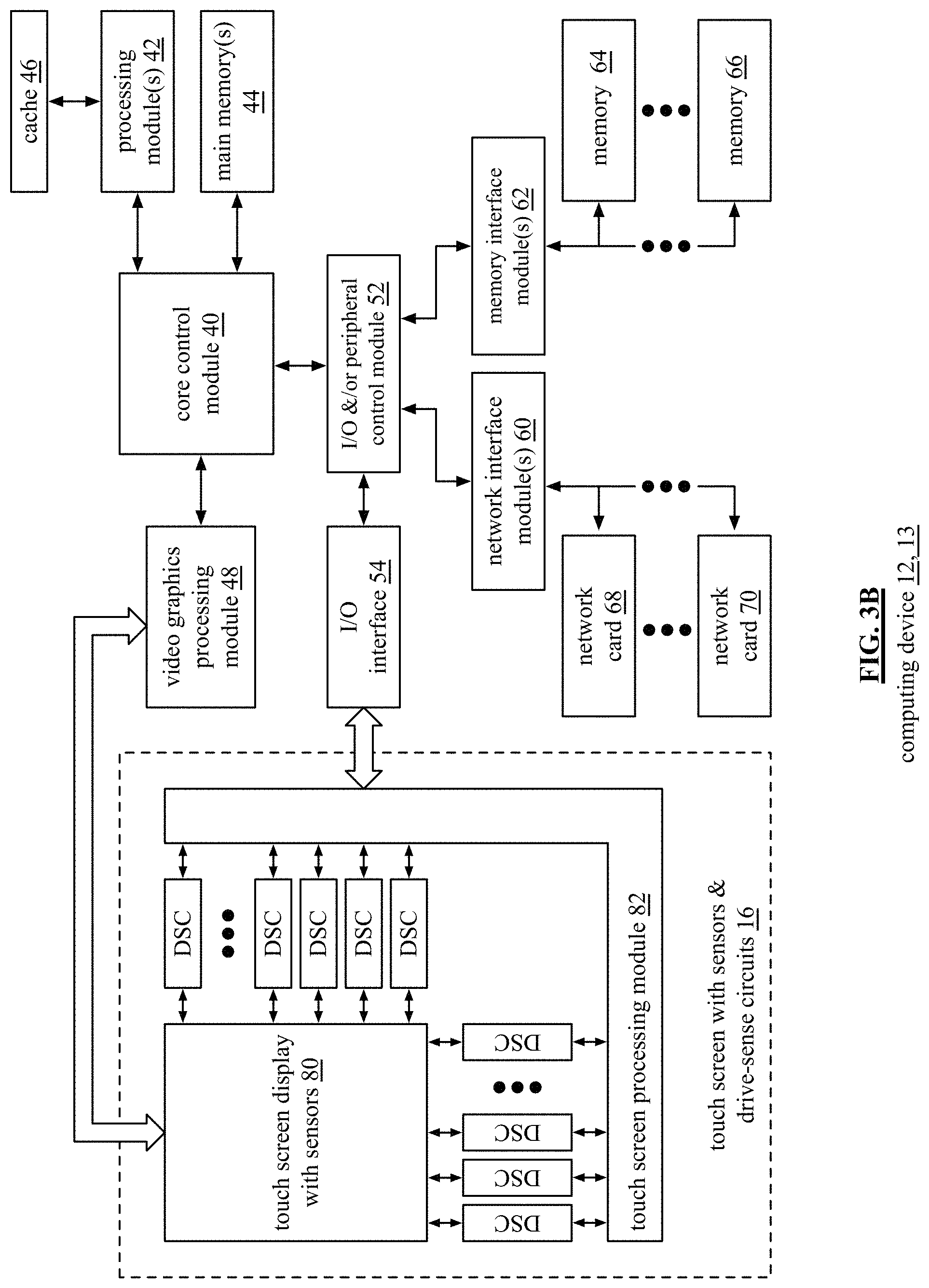

FIG. 3B is a schematic block diagram of another embodiment of a computing device in accordance with the present invention;

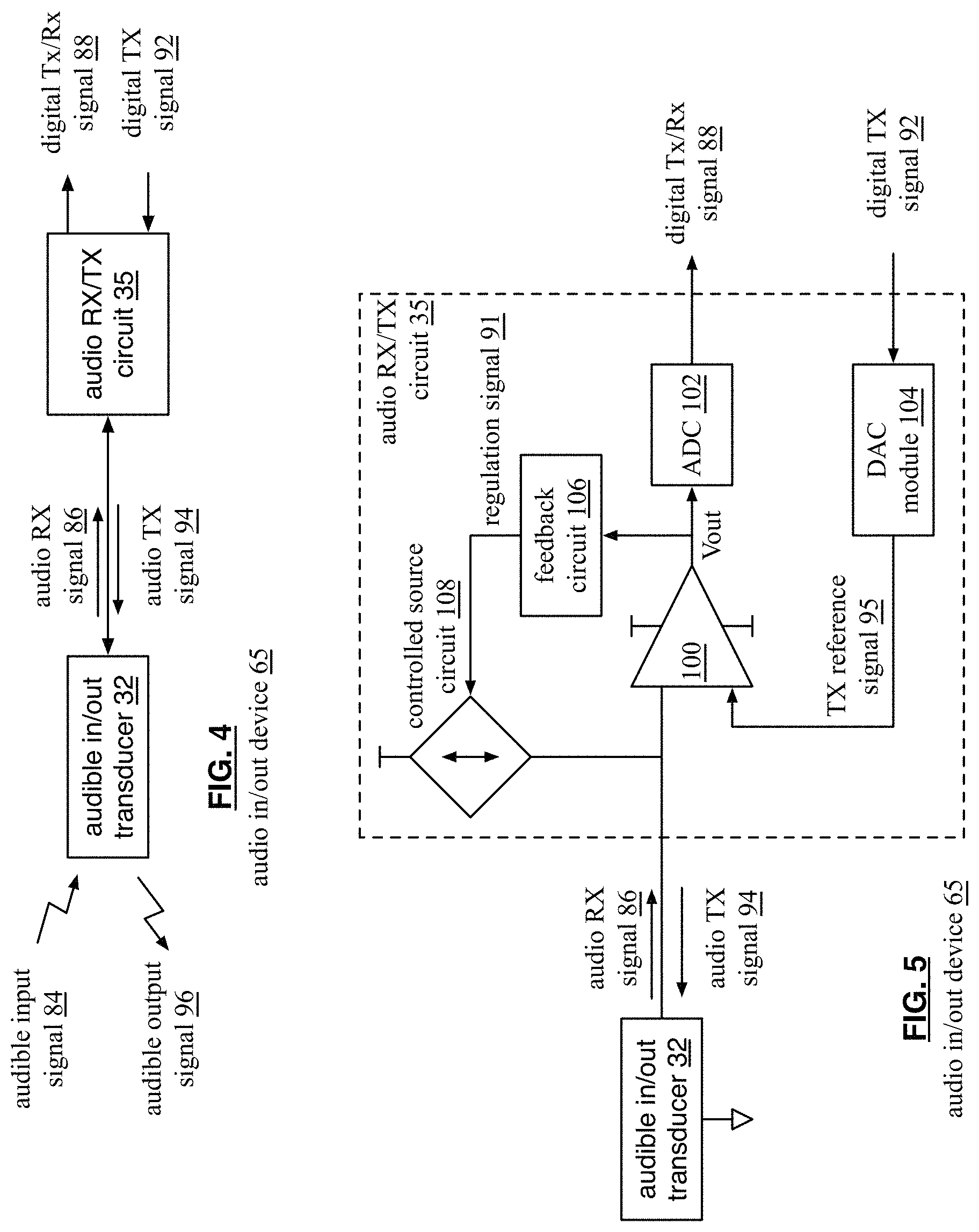

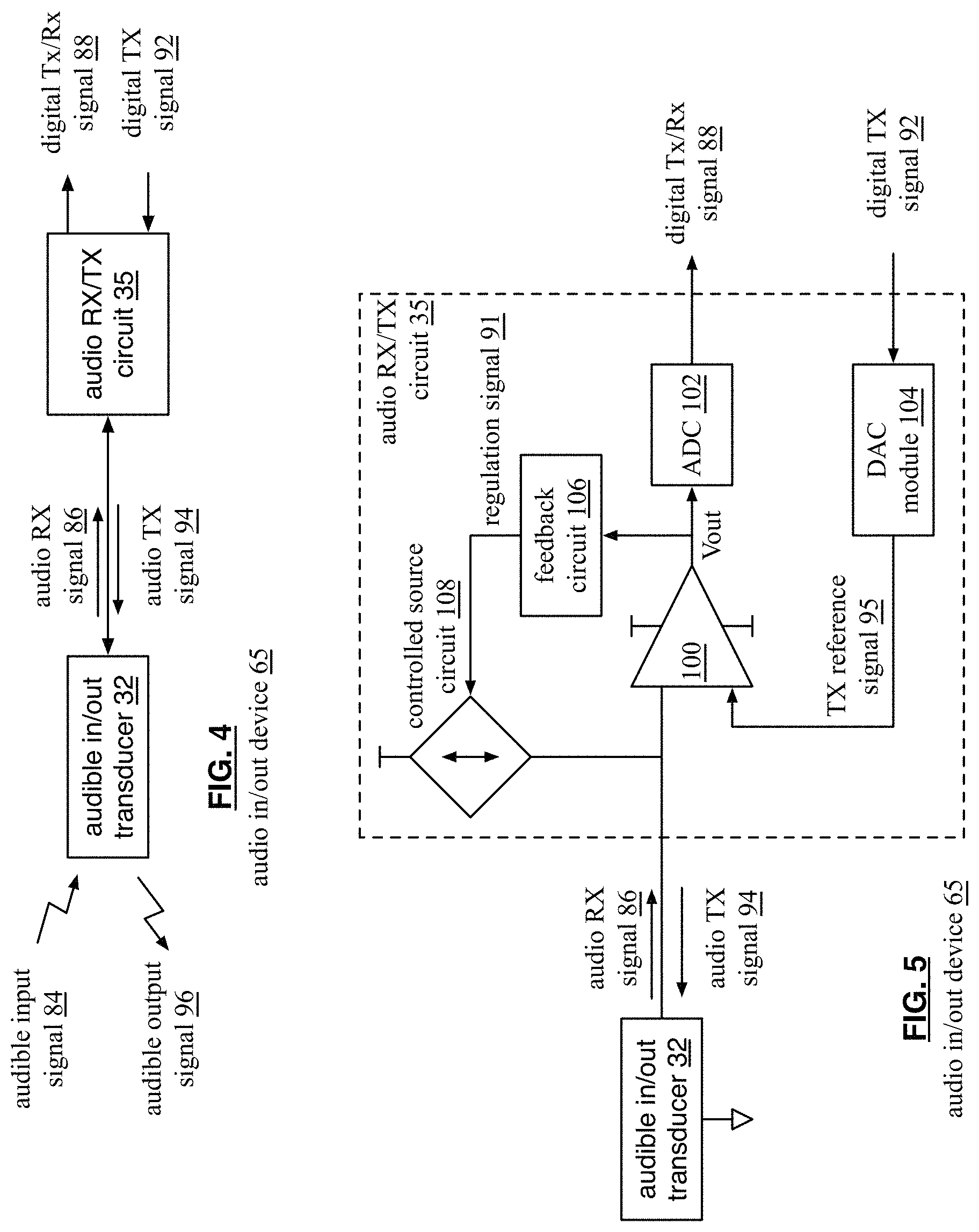

FIG. 4 is a schematic block diagram of an embodiment of an audio in/out device in accordance with the present invention;

FIG. 5 is a schematic block diagram of another embodiment of an audio in/out device in accordance with the present invention;

FIG. 6 is a schematic block diagram of an embodiment of a digital to analog converter (DAC) module in accordance with the present invention;

FIG. 7 is an example of a transmit (TX) reference signal in accordance with the present invention;

FIG. 8 is a schematic block diagram of an embodiment of an audio input/output device in a microphone (mic) only mode in accordance with the present invention;

FIG. 8A is an example of signals of the audio in/out device of FIG. 8 in accordance with the present invention;

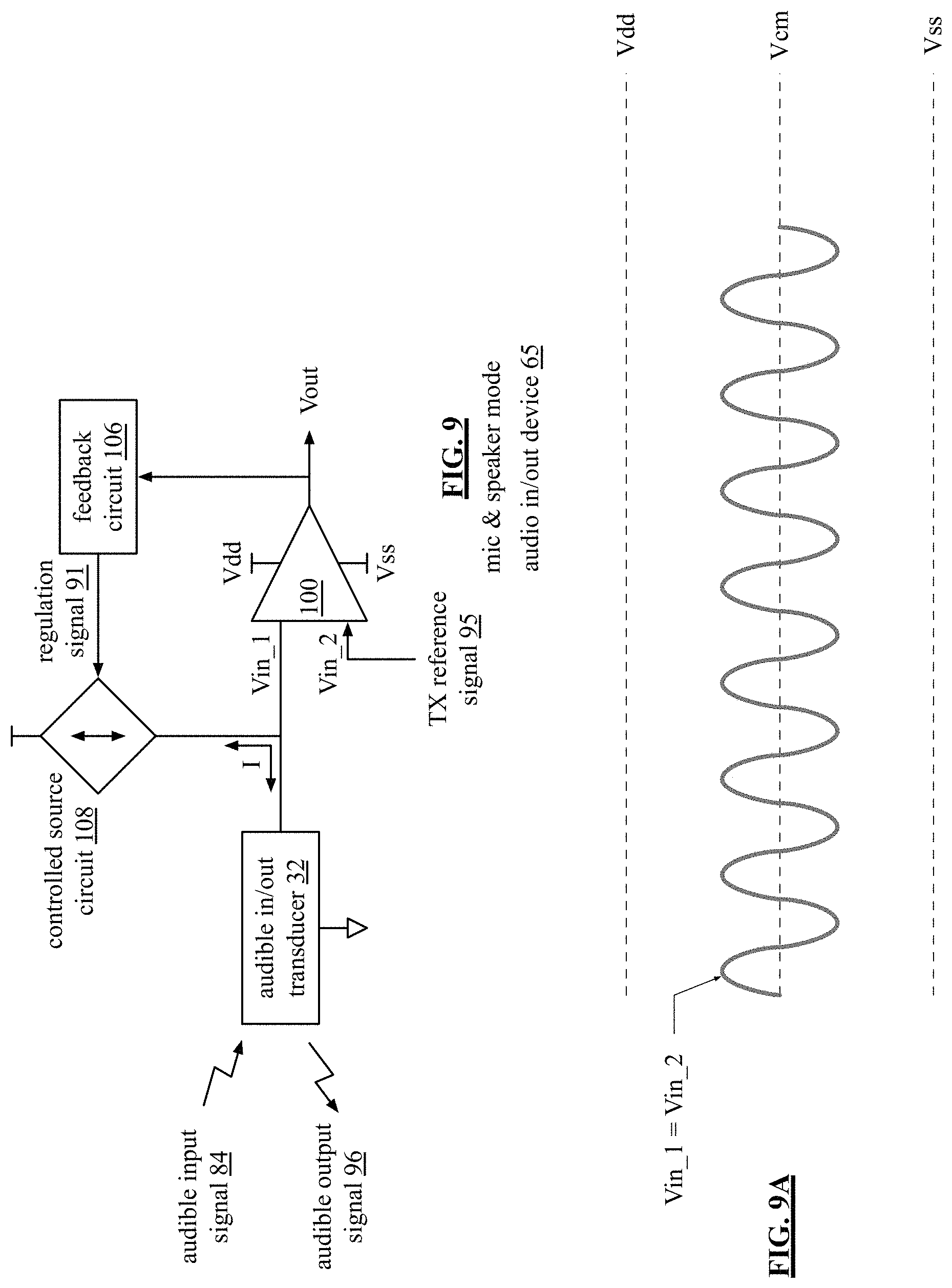

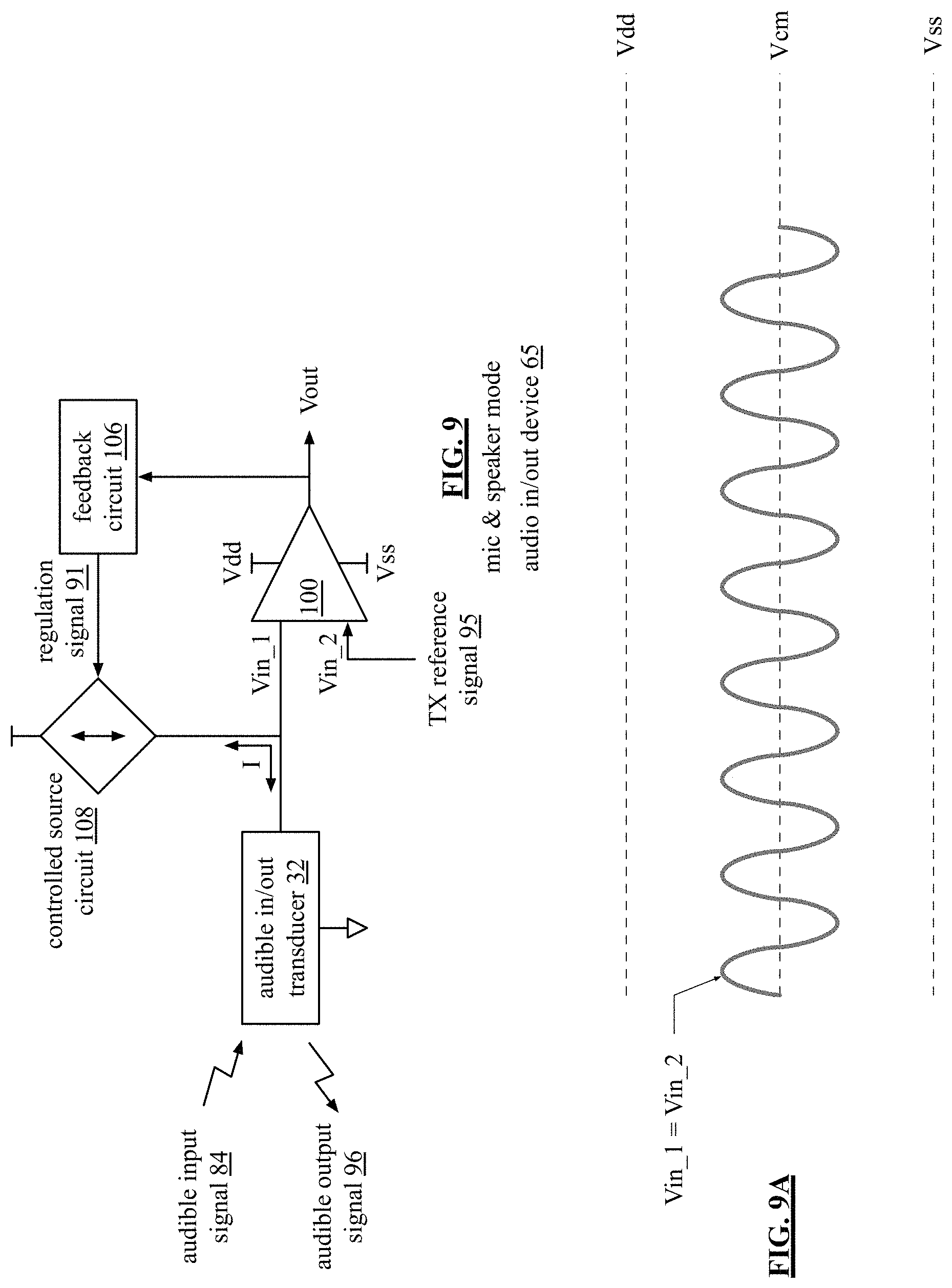

FIG. 9 is a schematic block diagram of an embodiment of an audio input/output device in a microphone (mic) and speaker mode in accordance with the present invention;

FIGS. 9A-9D are examples of signals of the audio in/out device of FIG. 9 in accordance with the present invention;

FIG. 10 is a schematic block diagram of another embodiment of an audio in/out device in accordance with the present invention;

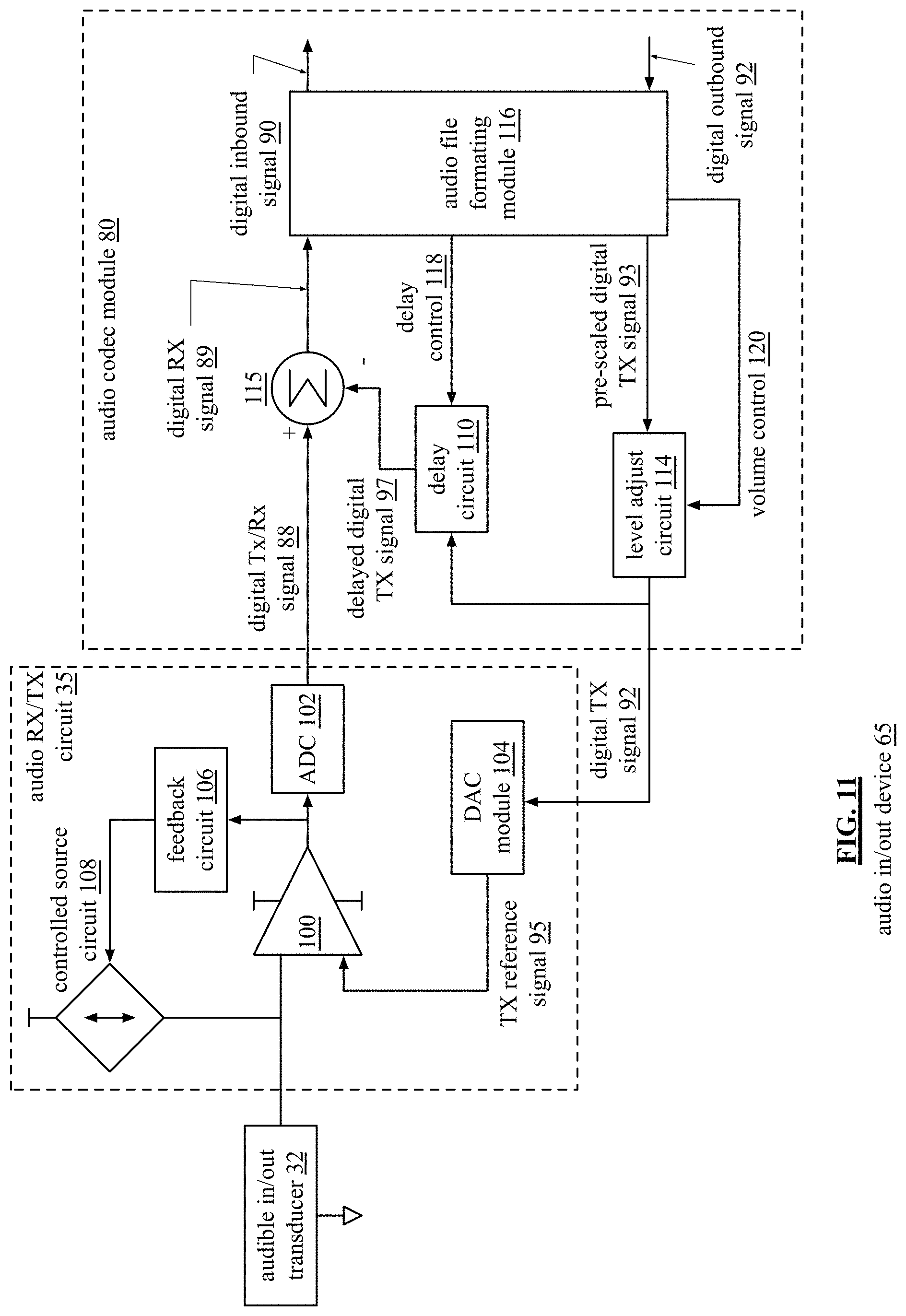

FIG. 11 is a schematic block diagram of another embodiment of an audio in/out device in accordance with the present invention;

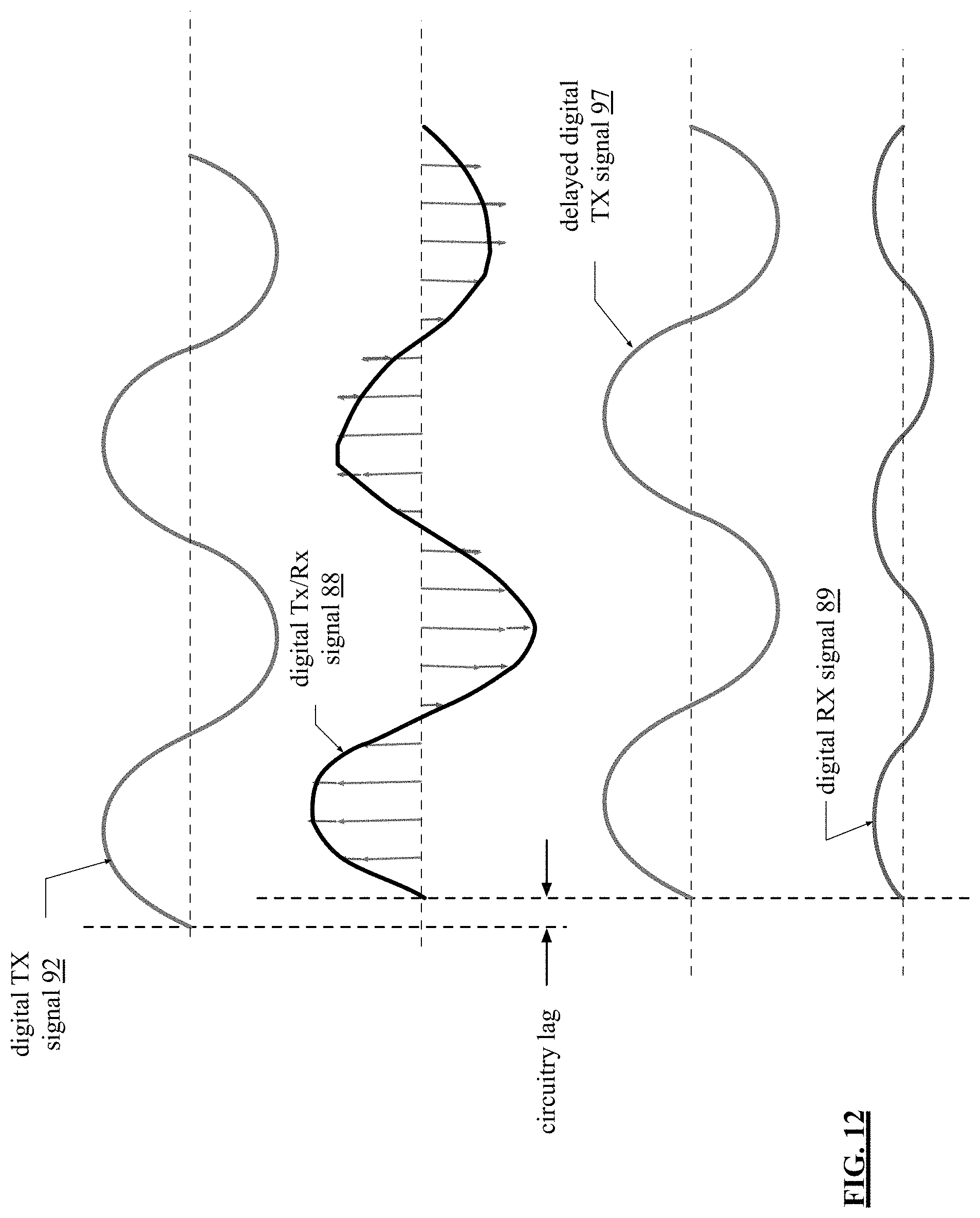

FIG. 12 is an example of signals of the audio in/out device of FIG. 11 in accordance with the present invention;

FIG. 13 is a schematic block diagram of another embodiment of an audio in/out device in accordance with the present invention;

FIG. 14 is a schematic block diagram of another embodiment of an audio in/out device in accordance with the present invention;

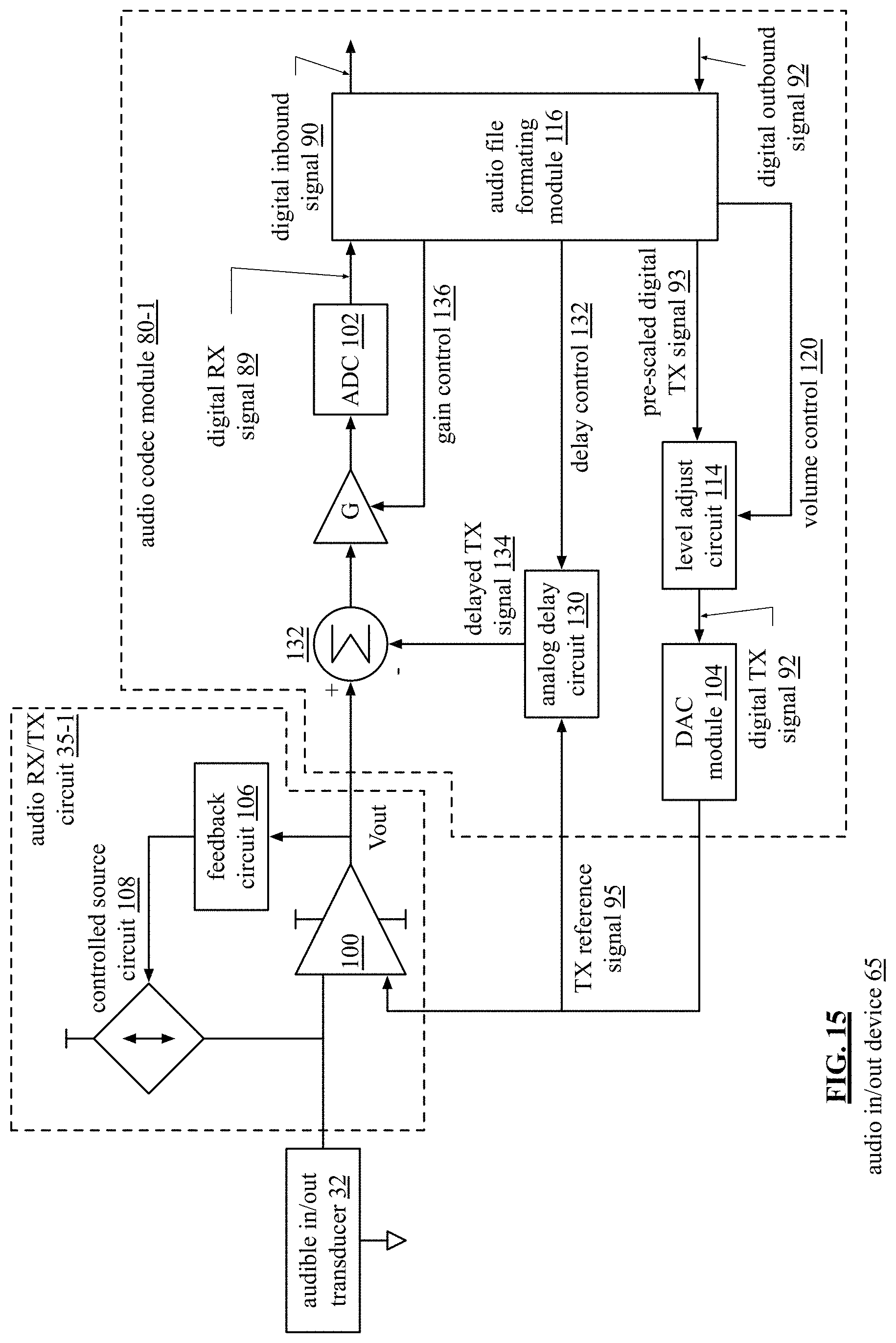

FIG. 15 is a schematic block diagram of another embodiment of an audio in/out device in accordance with the present invention;

FIG. 16 is a schematic block diagram of another embodiment of an audio in/out device in accordance with the present invention;

FIG. 17 is a schematic block diagram of another embodiment of an audio in/out device in accordance with the present invention;

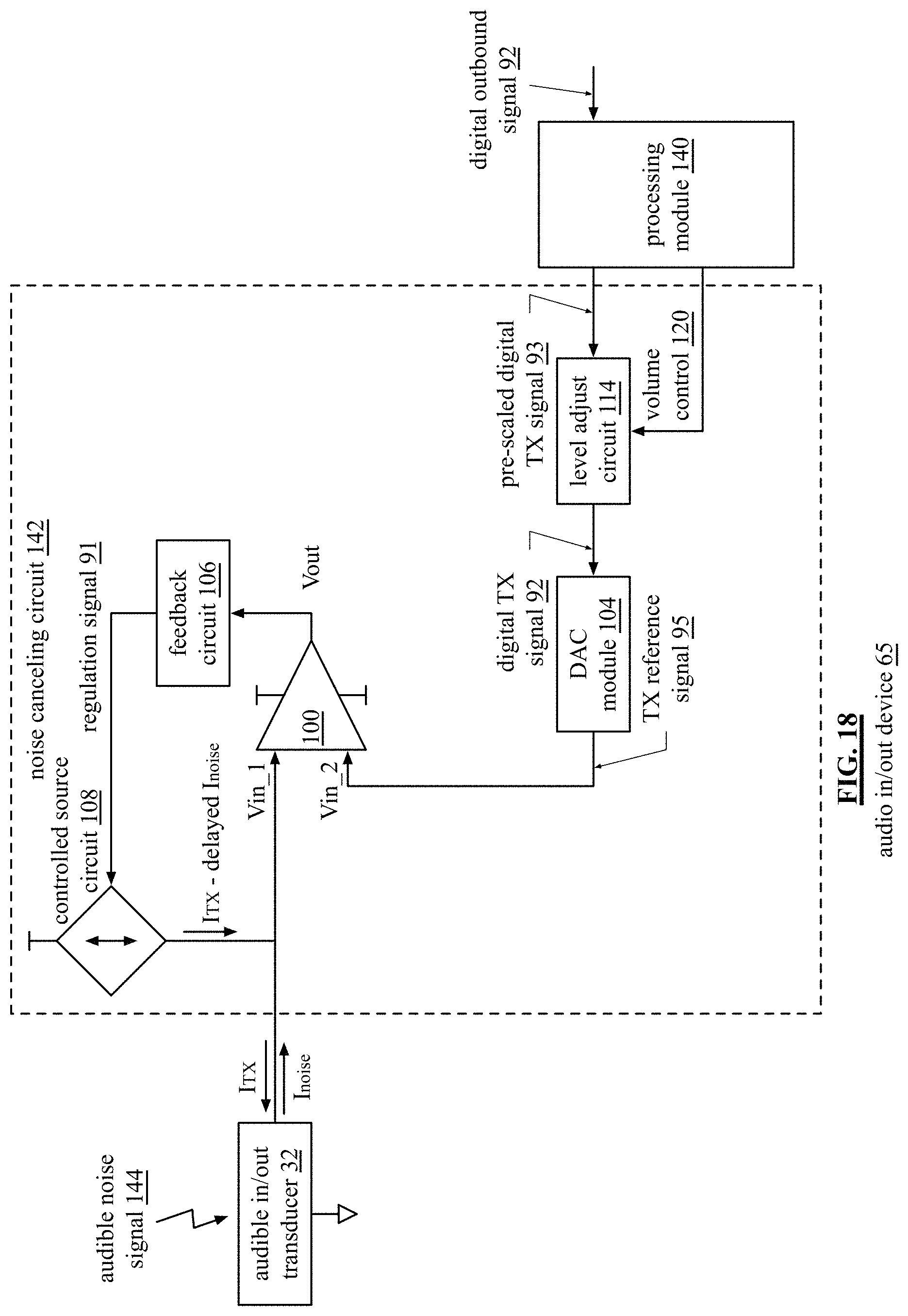

FIG. 18 is a schematic block diagram of an embodiment of an audio in/out device as a noise canceling speaker system in accordance with the present invention;

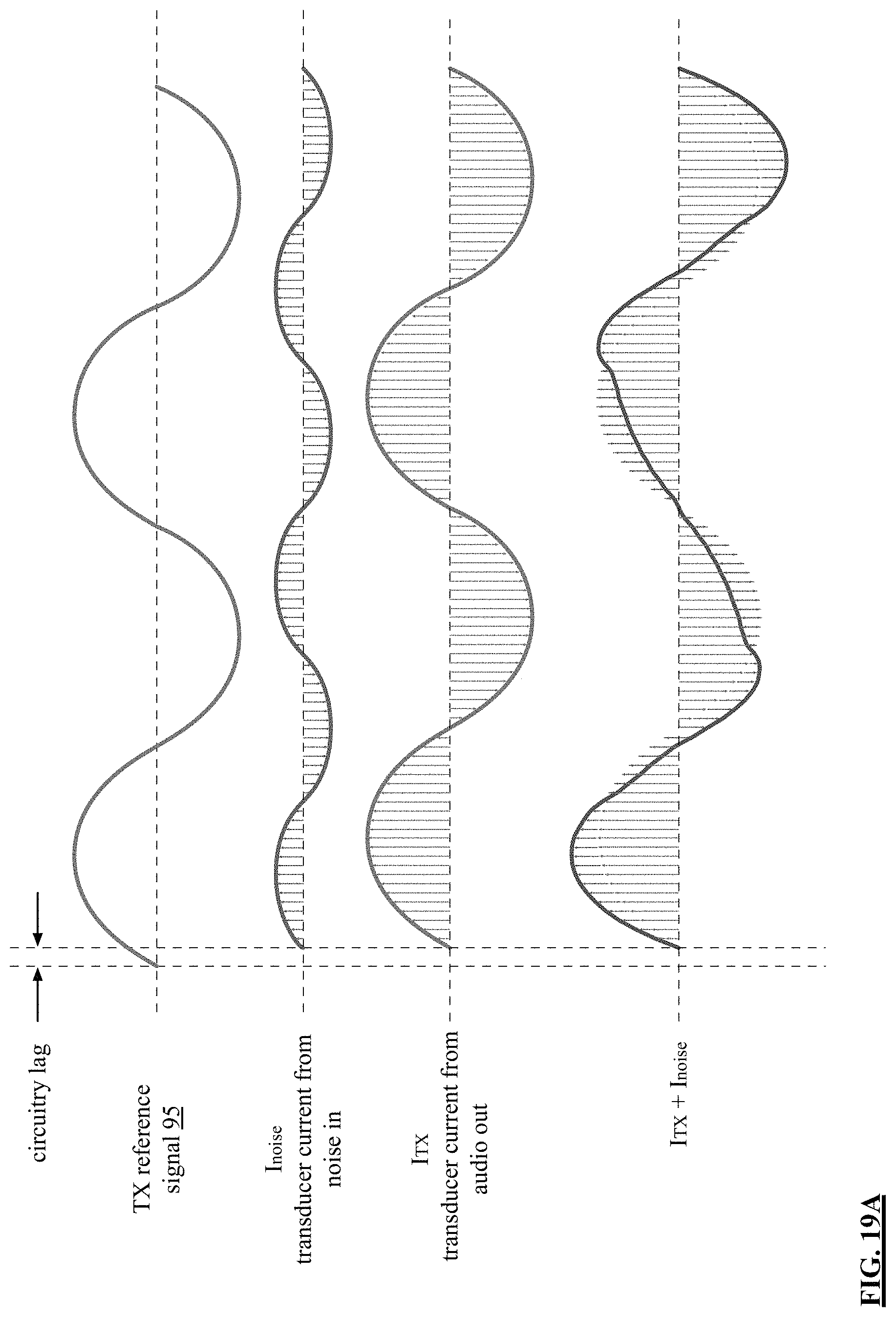

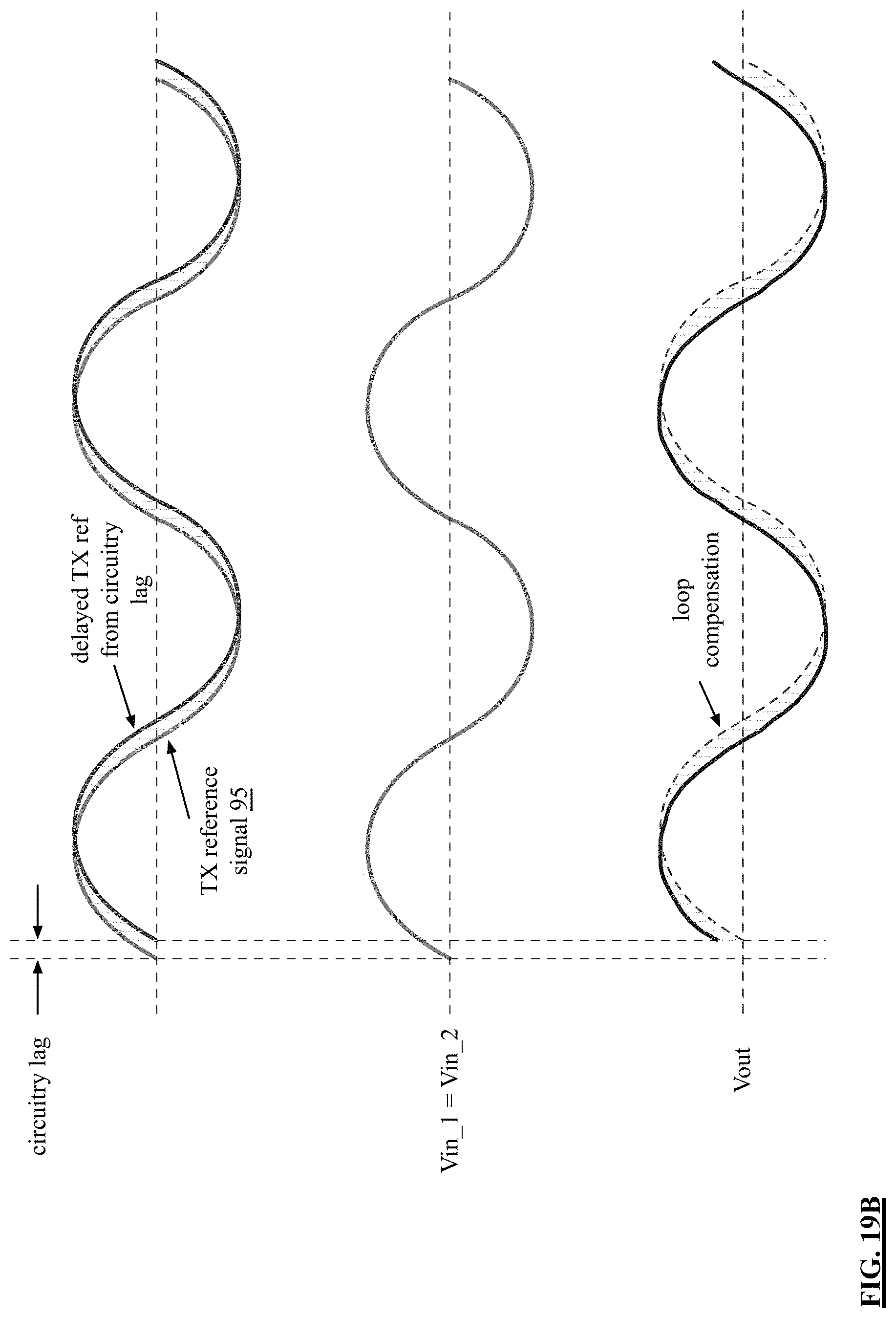

FIGS. 19A-19C are examples of the signals of the audio in/out device of FIG. 18 in accordance with the present invention;

FIG. 20 is a schematic block diagram of another embodiment of an audio in/out device as a noise canceling speaker system in accordance with the present invention;

FIG. 21 is a schematic block diagram of another embodiment of an audio in/out device as a noise canceling speaker system in accordance with the present invention;

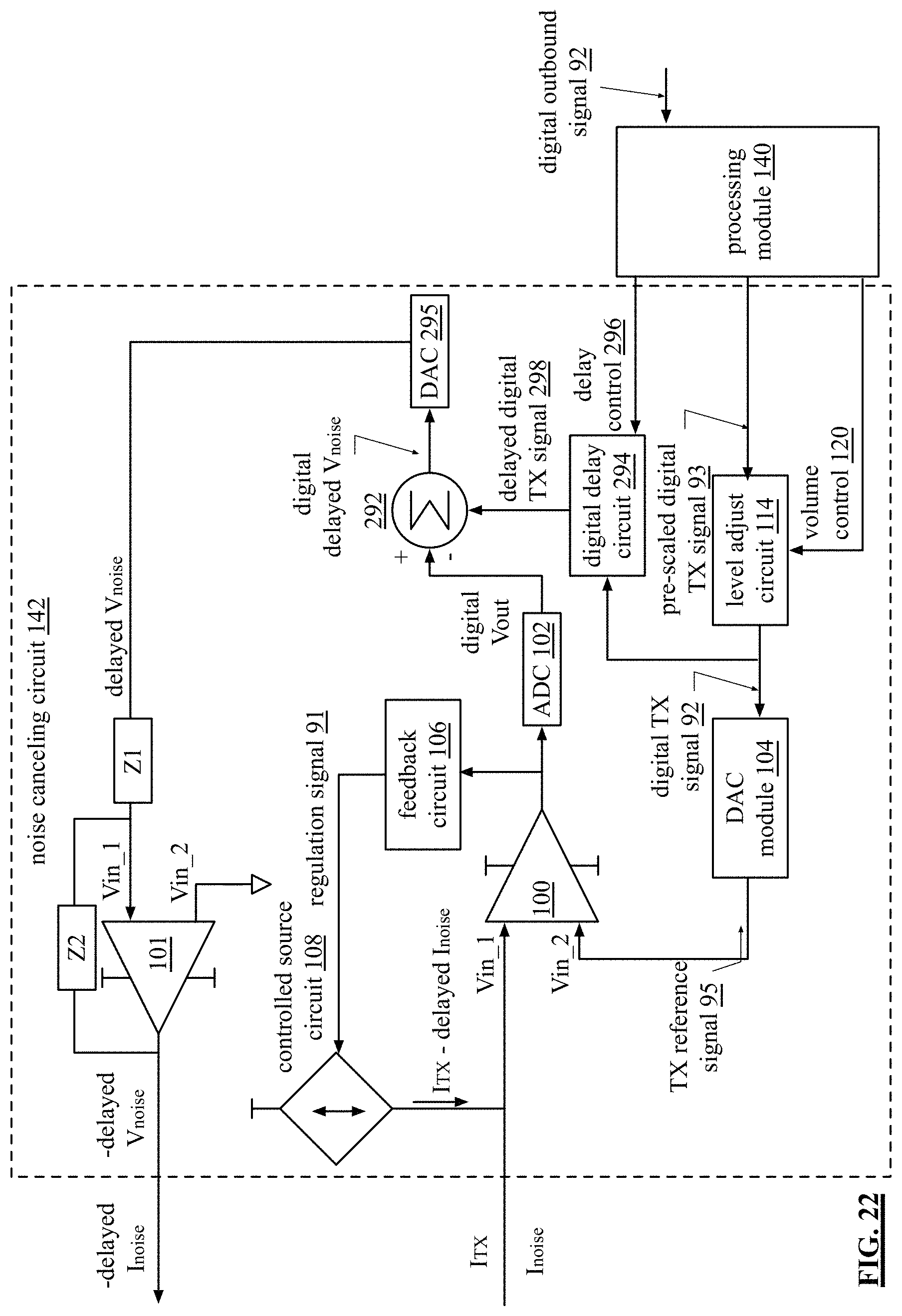

FIG. 22 is a schematic block diagram of an embodiment of a portion of an audio in/out device as a noise canceling speaker system in accordance with the present invention;

FIG. 23 is a schematic block diagram of another embodiment of an audio in/out device as a noise canceling speaker system in accordance with the present invention;

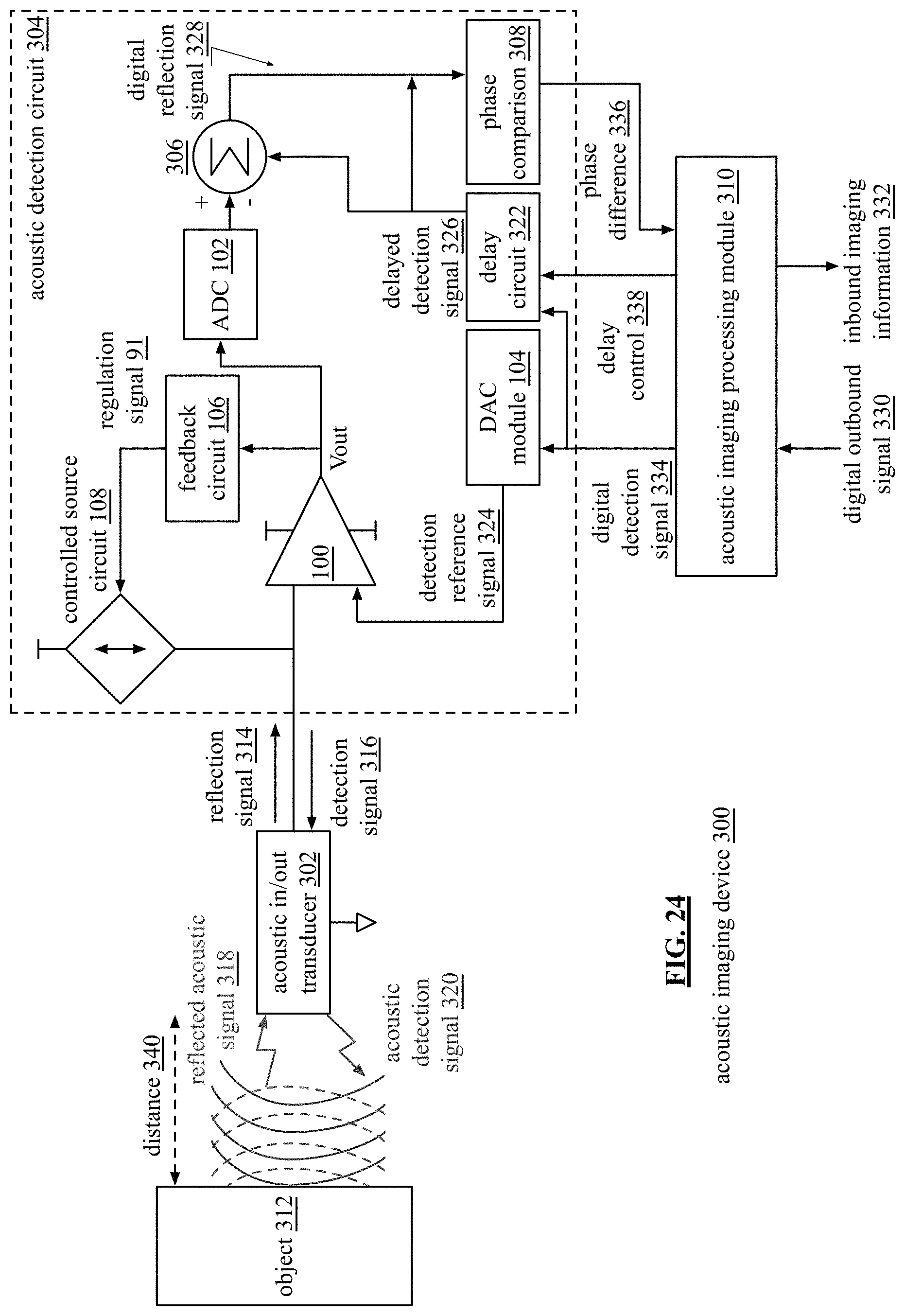

FIG. 24 is a schematic block diagram of an embodiment of an acoustic imaging device in accordance with the present invention;

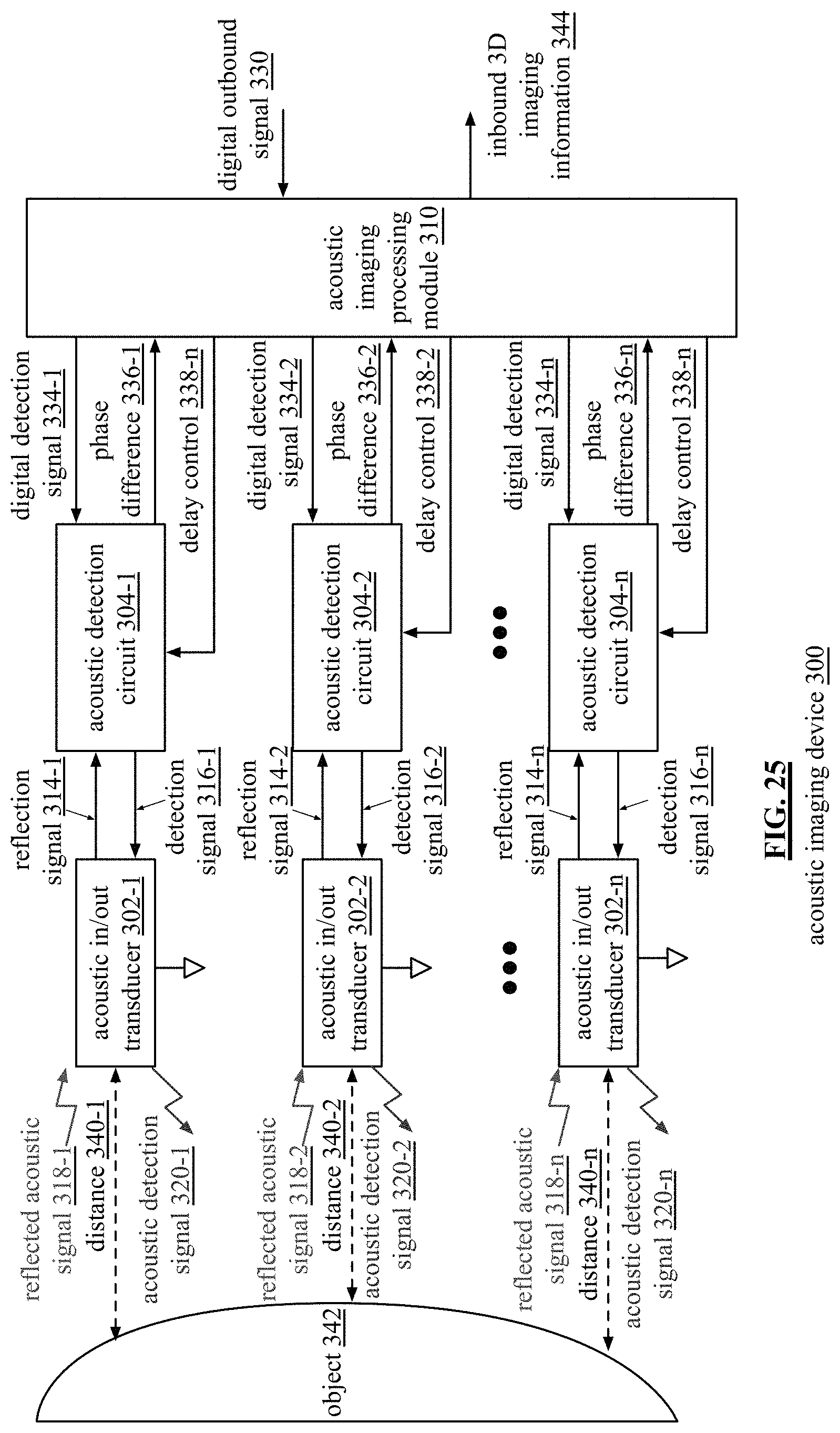

FIG. 25 is a schematic block diagram of another embodiment of an acoustic imaging device in accordance with the present invention;

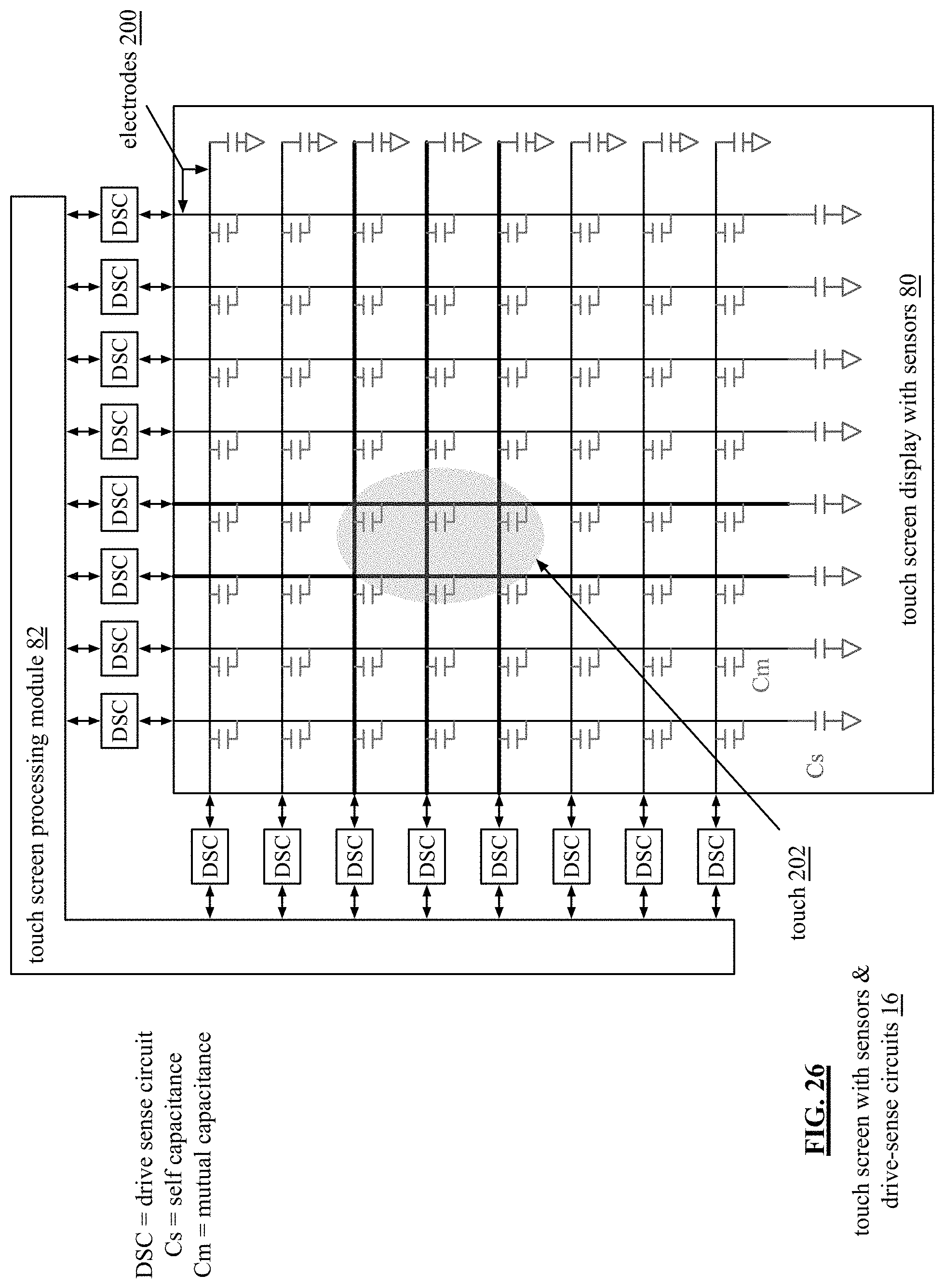

FIG. 26 is a schematic block diagram of an embodiment of a touch screen with sensors and drive sense circuits (DSC) in accordance with the present invention;

FIG. 27 is a schematic block diagram of an embodiment of a drive-sense circuit (DSC) coupled to an electrode and a voltage reference generator in accordance with the present invention;

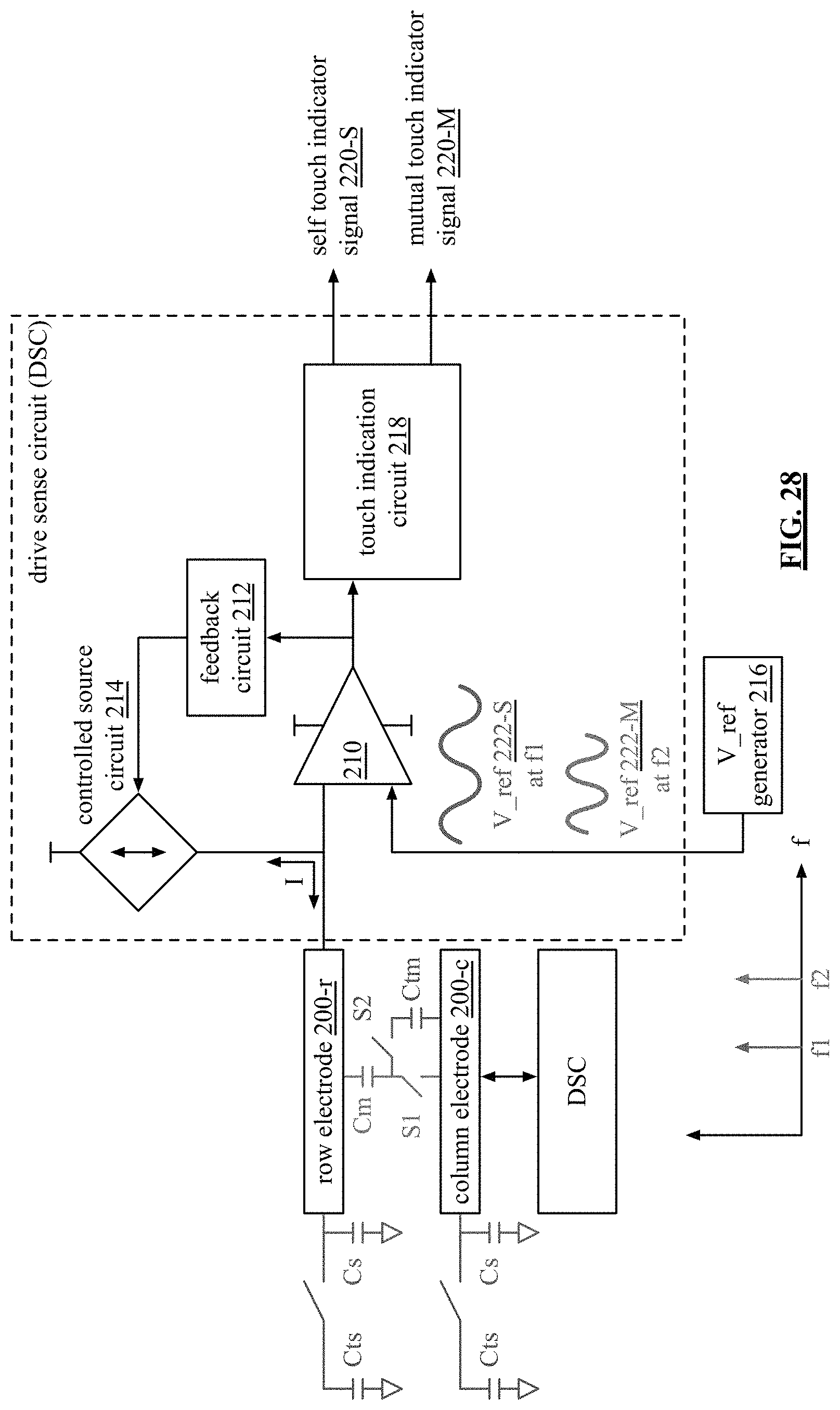

FIG. 28 is a schematic block diagram of an embodiment of a drive-sense circuit (DSC) coupled to a row electrode and a voltage reference generator in accordance with the present invention;

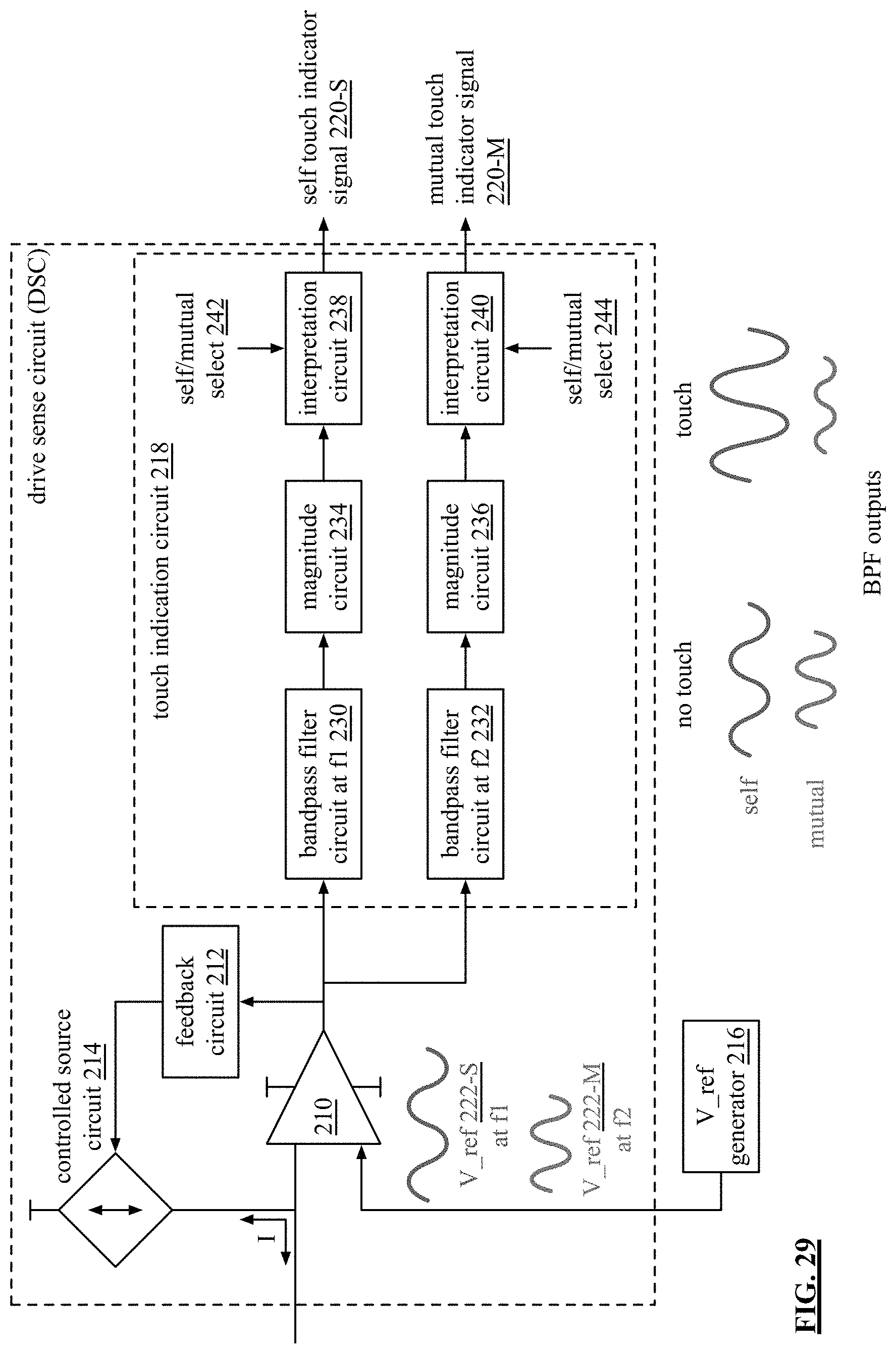

FIG. 29 is a schematic block diagram of another embodiment of a drive-sense circuit (DSC) coupled to an electrode and a voltage reference generator in accordance with the present invention;

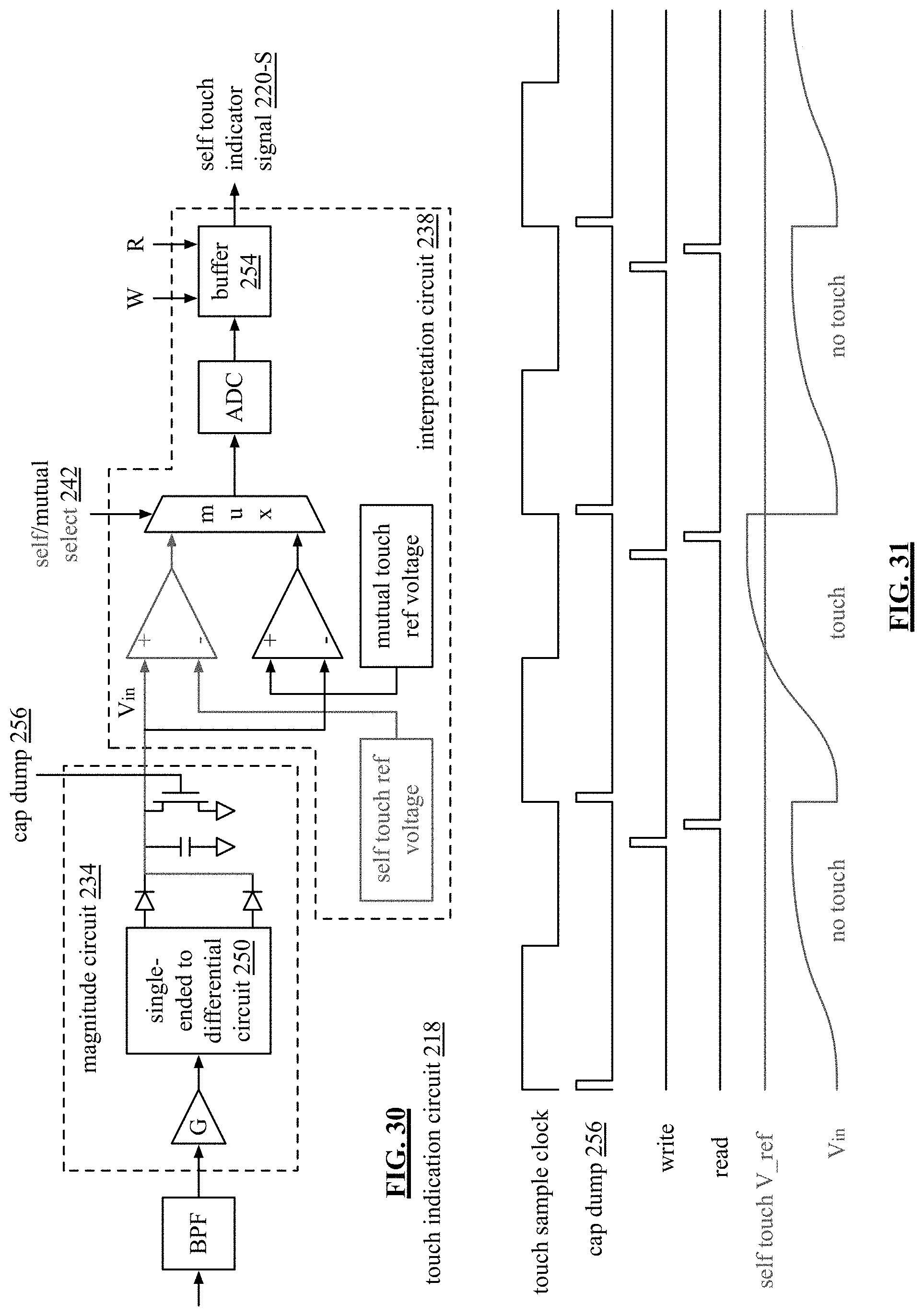

FIG. 30 is a schematic block diagram of an embodiment of a touch indication circuit in accordance with the present invention;

FIG. 31 is an example of signals of the touch indication circuit of FIG. 30 in accordance with the present invention;

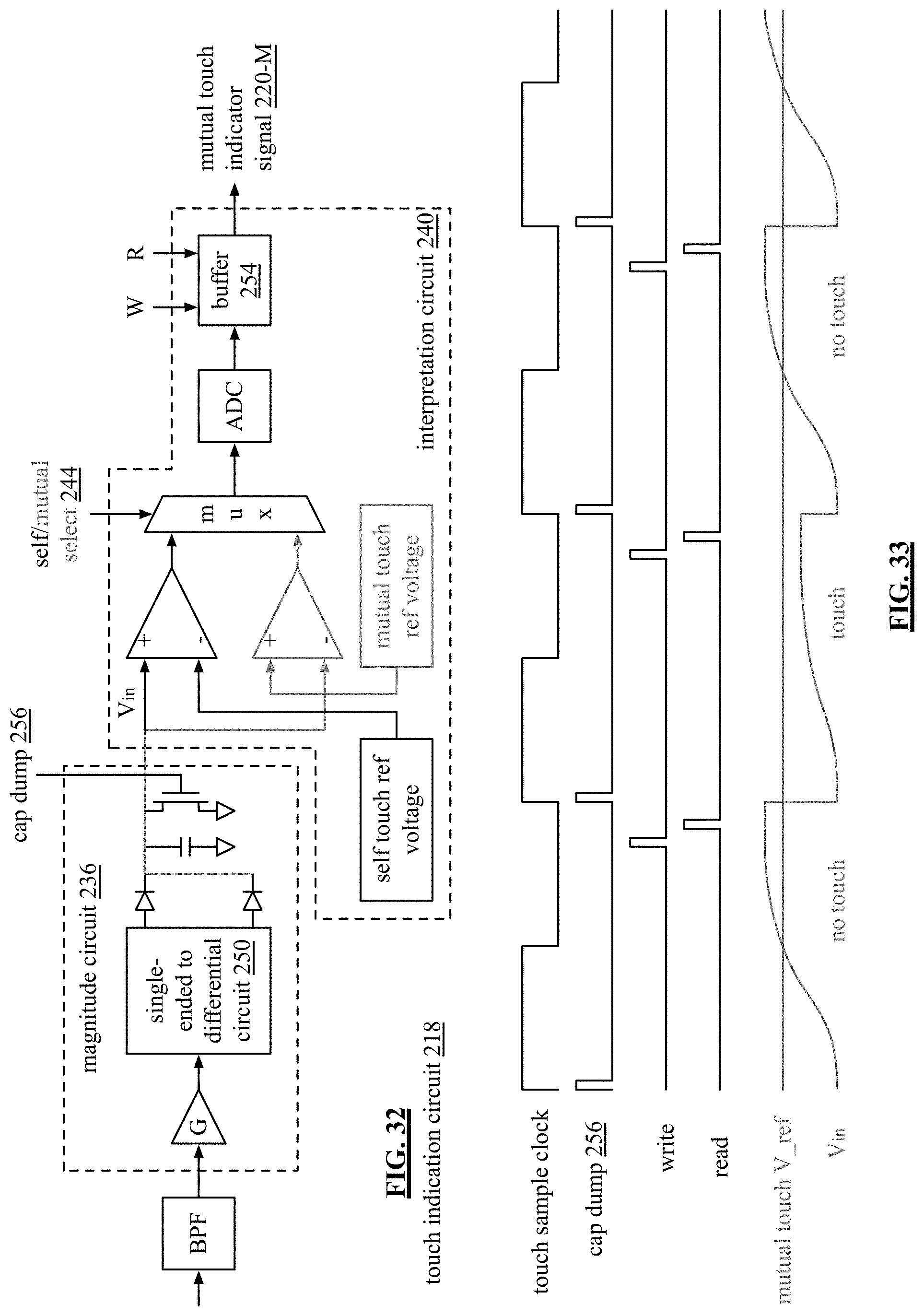

FIG. 32 is a schematic block diagram of another embodiment of a touch indication circuit in accordance with the present invention;

FIG. 33 is an example of signals of the touch indication circuit of FIG. 32 in accordance with the present invention;

FIG. 34A is a flowchart of an example of a method of determining a self touch reference voltage in accordance with the present invention;

FIG. 34B is an example of determining a self touch reference voltage in accordance with the present invention;

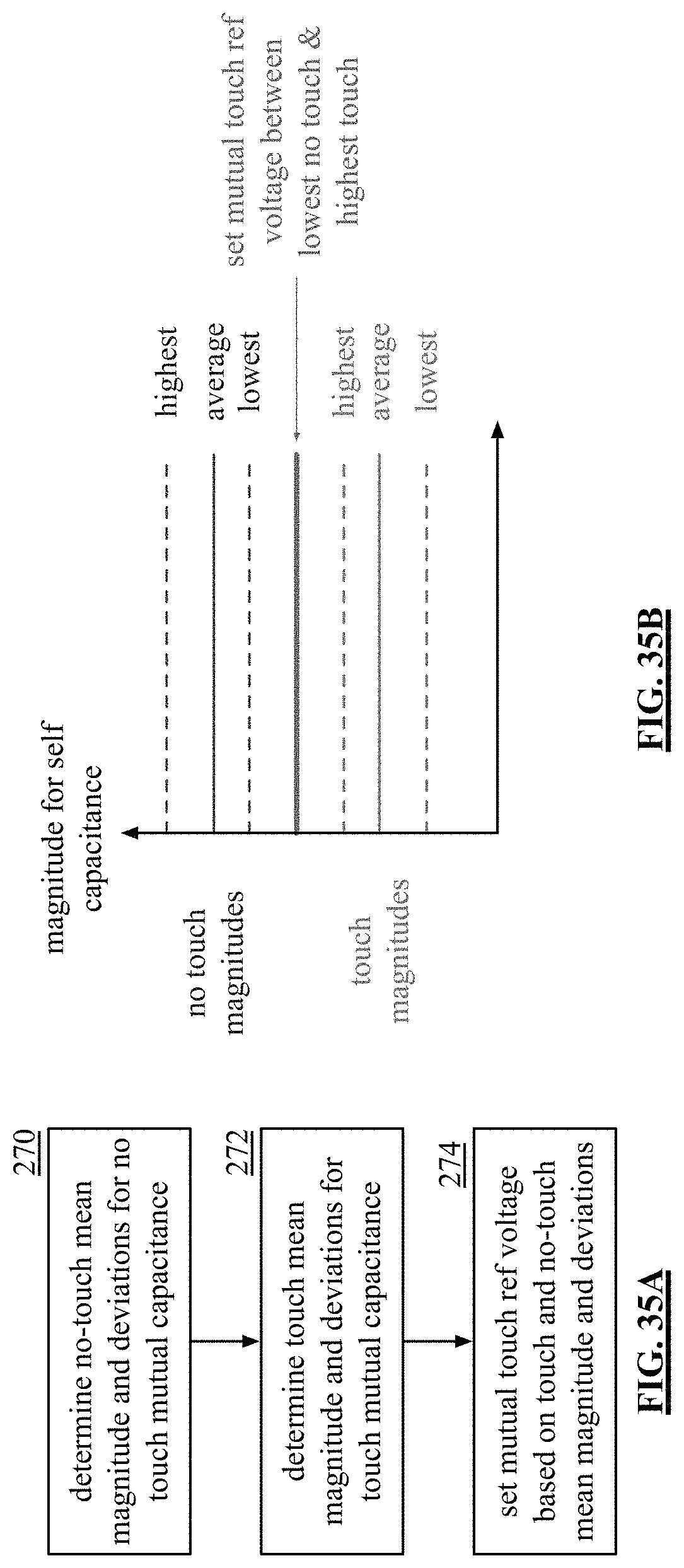

FIG. 35A is a flowchart of an example of a method of determining a mutual touch reference voltage in accordance with the present invention; and

FIG. 35B is an example of determining a mutual touch reference voltage in accordance with the present invention.

DETAILED DESCRIPTION OF THE INVENTION

FIG. 1 is a schematic block diagram of an embodiment of a communication system 10 that includes a plurality of wired computing devices 12, a plurality of wireless computing devices 13, one or more servers 22, one or more databases 24, and one or more networks 26. Embodiments of computing devices 12 and 13 are similar in construct and/or functionality with a difference being the computing devices 12 couple to the network(s) 26 via a wired network card and the wireless communication devices 13 coupled to the network(s) 26 via a wireless connection. In an embodiment, a computing device can have both a wired network card and a wireless network card such that it is both computing devices 12 and 13.

A computing device 12 and/or 13 may be a portable computing device and/or a fixed computing device. A portable computing device may be a social networking device, a gaming device, a cell phone, a smart phone, a digital assistant, a digital music player, a digital video player, a laptop computer, a handheld computer, a tablet, a video game controller, and/or any other portable device that includes a computing core. A fixed computing device may be a computer (PC), a computer server, a cable set-top box, a satellite receiver, a television set, a printer, a fax machine, home entertainment equipment, a video game console, and/or any type of home or office computing equipment. The computing devices 12 and 13 will be discussed in greater detail with reference to one or more of FIGS. 2-3A.

A server 22 is a special type of computing device that is optimized for processing large amounts of data requests in parallel. A server 22 includes similar components to that of the computing devices 12 and/or 13 with more robust processing modules, more main memory, and/or more hard drive memory (e.g., solid state, hard drives, etc.). Further, a server 22 is typically accessed remotely; as such it does not generally include user input devices and/or user output devices. In addition, an embodiment of a server is a standalone separate computing device and/or may be a cloud computing device.

A database 24 is a special type of computing device that is optimized for large scale data storage and retrieval. A database 24 includes similar components to that of the computing devices 12 and/or 13 with more hard drive memory (e.g., solid state, hard drives, etc.) and potentially with more processing modules and/or main memory. Further, a database 24 is typically accessed remotely; as such it does not generally include user input devices and/or user output devices. In addition, an embodiment of a database 24 is a standalone separate computing device and/or may be a cloud computing device.

The network(s) 26 includes one or more local area networks (LAN) and/or one or more wide area networks (WAN), which may be a public network and/or a private network. A LAN may be a wireless-LAN (e.g., Wi-Fi access point, Bluetooth, ZigBee, etc.) and/or a wired LAN (e.g., Firewire, Ethernet, etc.). A WAN may be a wired and/or wireless WAN. For example, a LAN is a personal home or business's wireless network and a WAN is the Internet, cellular telephone infrastructure, and/or satellite communication infrastructure.

The wired computing devices 12 and/or the wireless computing devices 13 communicate sensed data within the communication system 10. For example, wired computing devices 12 and/or the wireless computing devices 13 include or connect to one or more single transducer audio in/out devices (also referred to herein as "audio in/out devices") for communicating audio information within the communication system 10. The audio information communication is between devices and/or is within a device. A single transducer audio in/out device is operable to convert sound waves to an electrical signal (e.g., operate as a microphone) and convert electrical signals to a sound output (e.g., operate as a speaker) using a single transducer. The single transducer audio in/out device is discussed in more detail with reference to FIGS. 2-3 and 4-23.

In another example, the wired computing devices 12 and/or the wireless computing devices 13 include or connect to one or more single transducer acoustic imaging devices (also referred to herein as "acoustic imaging devices") for detecting and image mapping objects in proximity to the communication system 10. A single acoustic imaging device is operable to convert an electrical detection signal to an acoustic detection signal (e.g., ultrasound waves) and, when the acoustic detection signal reflects off of an object, to convert an acoustic reflection signal to an electrical reflection signal using a single transducer. The time between the detection signal is sent and the reflection signal is received is used to calculate the transducer's distance from the object and generate an image.

For example, the single transducer acoustic imaging device is a sonar (sound navigation and ranging) device for mapping an ocean floor. As another example, the single transducer acoustic imaging device is an ultrasound machine for generating images of internal organs and/or other bodily materials. The single transducer acoustic imaging device is discussed in more detail with reference to FIGS. 3A and 24-25.

In another example, the wired computing devices 12 and/or the wireless computing devices 13 include or connect to one or more touch screens with sensors and drive sense circuits for communicating touch sense data within the communication system 10. The touch sense data communication is between devices and/or is within a device. The touch screen with sensors and drive sense circuits is discussed in more detail with reference to FIGS. 3A and 26-35B.

FIG. 2 is a schematic block diagram of an embodiment of a computing device 12 or 13 that includes a core control module 40, one or more processing modules 42, one or more main memories 44 (e.g., volatile memory), cache memory 46, a video graphics processing module 48, a display 50, an Input-Output (I/O) and/or peripheral control module 52, one or more input interface modules 56, one or more output interface modules 58, an integrated (i.e., built in) audio in/out device 65, one or more network interface modules 60, and one or more memory interface modules 62.

A processing module 42 is described in greater detail at the end of the detailed description of the invention section and, in an alternative embodiment, has a direct connection to the main memory 44. In an alternate embodiment, the core control module 40 and the I/O and/or peripheral control module 52 are one module, such as a chipset, a quick path interconnect (QPI), and/or an ultra-path interconnect (UPI).

Each of the main memories 44 includes one or more Random Access Memory (RAM) integrated circuits, or chips. For example, a main memory 44 includes four DDR4 (4.sup.th generation of double data rate) RAM chips, each running at a rate of 2,400 MHz. In general, the main memory 44 stores data and operational instructions most relevant for the processing module 42. For example, the core control module 40 coordinates the transfer of data and/or operational instructions from the main memory 44 and the memory 64-66. The data and/or operational instructions retrieved from memory 64-66 are the data and/or operational instructions requested by the processing module or will most likely be needed by the processing module. When the processing module is done with the data and/or operational instructions in main memory, the core control module 40 coordinates sending updated data to the memory 64-66 for storage.

The memory 64-66 (i.e., non-volatile memory) includes one or more hard drives, one or more solid state memory chips, and/or one or more other large capacity storage devices that, in comparison to cache memory and main memory devices, is/are relatively inexpensive with respect to cost per amount of data stored. The memory 64-66 is coupled to the core control module 40 via the I/O and/or peripheral control module 52 and via one or more memory interface modules 62. In an embodiment, the I/O and/or peripheral control module 52 includes one or more Peripheral Component Interface (PCI) buses to which peripheral components connect to the core control module 40. A memory interface module 62 includes a software driver and a hardware connector for coupling a memory device to the I/O and/or peripheral control module 52. For example, a memory interface 62 is in accordance with a Serial Advanced Technology Attachment (SATA) port.

The core control module 40 coordinates data communications between the processing module(s) 42 and a network, or networks, via the I/O and/or peripheral control module 52, the network interface module(s) 60, and a network card 68 or 70. A network card 68 or 70 includes a wireless communication unit (e.g., for a wireless computing device 13) or a wired communication unit (e.g., for a wired computing device 12). A wireless communication unit includes a wireless local area network (WLAN) communication device, a cellular communication device, a Bluetooth device, and/or a ZigBee communication device. A wired communication unit includes a Gigabit LAN connection, a Firewire connection, and/or a proprietary computer wired connection. A network interface module 60 includes a software driver and a hardware connector for coupling the network card to the I/O and/or peripheral control module 52. For example, the network interface module 60 is in accordance with one or more versions of IEEE 802.11, cellular telephone protocols, 10/100/1000 Gigabit LAN protocols, etc.

The core control module 40 coordinates data communications between the processing module(s) 42 and the user input device(s) 72 via the input interface module(s) 56 and the I/O and/or peripheral control module 52. A user input device 72 includes a keypad, a keyboard, control switches, a touchpad, a microphone, a camera, etc. An input interface module 56 includes a software driver and a hardware connector for coupling a user input device to the I/O and/or peripheral control module 52. In an embodiment, an input interface module is in accordance with one or more Universal Serial Bus (USB) protocols.

The core control module 40 coordinates data communications between the processing module(s) 42 and the user output device(s) 74 via the output interface module(s) 58 and the I/O and/or peripheral control module 52. A user output device 74 includes a speaker, etc. An output interface module 58 includes a software driver and a hardware connector for coupling a user output device 58 to the I/O and/or peripheral control module 52. In an embodiment, an output interface module 58 is in accordance with one or more audio codec protocols.

The core control module 40 coordinates data communications between the processing module(s) 42 and the audio in/out device(s) 65 and the I/O and/or peripheral control module 52. The audio in/out device 65 includes an audible in/out transducer 32 and an audio receive/transmit (RX/TX) circuit 35. In comparison to the user input device(s) 72 and the user output device(s) 74, the audio in/out device 65 is both an input and output device.

A transducer has varying electrical characteristics (e.g., capacitance, inductance, impedance, current, voltage, etc.) based on varying physical conditions (e.g., pressure, temperature, biological, chemical, etc.). As such, a transducer functions to convert one form of energy (e.g., force, sound, etc.) into another form of energy (e.g., electrical signal). Sound transducers include dynamic transducers, condenser transducers, electret condenser transducers, ribbon transducers, piezoelectric transducers, etc. Piezoelectric transducers consist of materials that experience the piezoelectric effect. The piezoelectric effect is the ability of certain materials to generate an electric charge in response to applied mechanical stress such as the presence of sound waves. Examples of piezoelectric materials include quartz crystals, piezoelectric ceramics, and certain kinds of biological matter.

Acoustic or sound transducers typically include two types: input transducers (or sound to electrical transducers (e.g., a microphone, noise sensor, etc.)) and output actuators (or electrical to sound transducers (e.g., a speaker)). A microphone is operable to convert the air pressure variations of a sound wave into an electrical signal and a speaker is operable to convert an electrical signal into a sound wave for output. In conventional audio devices, for every microphone transducer, there is a corresponding speaker transducer.

Due to the unique circuitry of the audio receive/transmit (RX/TX) circuit 35, a single audible in/out transducer 32 is operable as both a microphone and a speaker. In general, the audio RX/TX circuit 35 is operable to drive the single audible in/out transducer 32 using a generated TX signal for output while receiving and processing an RX signal representative of sound from the single audible in/out transducer 32. The audio receive/transmit (RX/TX) circuit 35 of the audio in/out device 65 will be discussed in further detail with reference to FIGS. 4-23.

While one audible in/out transducer 32 is shown here, multiple audible in/out transducers 32 and audio receive/transmit (RX/TX) circuits 35 can be used for multiple speaker/microphone implementations. For example, stereophonic ("stereo") sound is a method of sound reproduction that creates the illusion of multi-directional sound perspective. For stereo sound, two or more independent audio channels (i.e., signals) are used and thus two transducers, where one channel feeds one transducer (e.g., a left speaker) and another channel feeds the other (e.g., a right speaker). In monoaural ("mono") sound, one signal is used. A mono sound signal can be copied to multiple speakers thus requiring more transducers or to a single speaker thus requiring one transducer. Surround sound uses more than two channels and thus more than two transducers to produce a more immersive sound experience coming from multiple directions.

The processing module 42 communicates directly with a video graphics processing module 48 to display data on the display 50. The display 50 includes an LED (light emitting diode) display, an LCD (liquid crystal display), and/or other type of display technology. The display has a resolution, an aspect ratio, and other features that affect the quality of the display. The video graphics processing module 48 receives data from the processing module 42, processes the data to produce rendered data in accordance with the characteristics of the display, and provides the rendered data to the display 50. While not shown, the computing device 12 or 13 further includes a BIOS (Basic Input Output System) memory coupled to the core control module 40.

FIG. 3 is a schematic block diagram of another embodiment of a computing device 12 or 13 that includes a core control module 40, one or more processing modules 42, one or more main memories 44, cache memory 46, a video graphics processing module 48, an Input-Output (I/O) peripheral control module 52, one or more input interface modules 56, one or more output interface modules 58, one or more network interface modules 60, one or more peripheral interface module(s) 61, one or more memory interface modules 62, and an audio in/out device 65.

Computing device 12 or 13 operates similarly to computing device 12 or 13 of FIG. 2 except for the addition of the one or more peripheral interface module(s) 61 and that the audio in/out device 65 is a peripheral device external to the computing device 12 or 13 (as opposed to the built in example shown in FIG. 2).

The core control module 40 coordinates data communications between the processing module(s) 42 and peripheral audio in/out device 65 via the peripheral interface module(s) 61 and the I/O and/or peripheral control module 52. The peripheral audio in/out device 65 may be a single ear mono headset requiring one audible in/out transducer 32 and one audio TX/RX circuit 35, a dual ear mono headset requiring two audible in/out transducers 32 and two audio TX/RX circuits 35, a stereo headset requiring two audible in/out transducers 32 and two audio TX/RX circuits 35, an external surround sound system requiring multiple audible in/out transducers 32 and multiple audio TX/RX circuits 35, and/or any other external device having dual speaker/microphone functionality (e.g., a speaker/microphone device for a conference table, etc.).

The peripheral audio in/out device 65 may include a noise canceling feature when applicable (e.g., when the peripheral audio in/out device 65 is a headset, headphones, earphones, ear buds, etc.). Because noise can be detected on the same line as transmission, the circuitry of the audio in/out device 65 allows for improved noise canceling in comparison to conventional noise canceling technology. The audio in/out device as a noise canceling speaker system is discussed in more detail with reference to FIGS. 18-23.

The peripheral interface module(s) 61 may include a software driver and a hardware connector for coupling the peripheral audio in/out device 65 to the I/O and/or peripheral control module 52. In an embodiment, the peripheral interface module(s) 61 is in accordance with one or more Universal Serial Bus (USB) protocols. In another embodiment, the peripheral interface module(s) 61 is in accordance with one or more audio codec protocols. The peripheral interface module(s) 61 may facilitate a network connection (e.g., via Bluetooth) between the audio in/out device 65 and the I/O and/or peripheral control module 52 of the computing device 12 or 13.

FIG. 3A is a schematic block diagram of another embodiment of a computing device 12 or 13 that includes a core control module 40, one or more processing modules 42, one or more main memories 44, cache memory 46, a video graphics processing module 48, an Input-Output (I/O) peripheral control module 52, one or more input interface modules 56, one or more output interface modules 58, one or more acoustic imaging devices 300, one or more network interface modules 60, and one or more memory interface modules 62. The computing device 12 or 13 of FIG. 3A may also include one or more audio in/out devices as discussed with reference to FIGS. 2 and/or 3.

Computing device 12 or 13 operates similarly to computing device 12 or 13 of FIG. 2 except that an acoustic imaging device 300 is integrated into the computing device 12 or 13 instead of the audio in/out device. The core control module 40 coordinates data communications between the processing module(s) 42 and the acoustic imaging device 300 and the I/O and/or peripheral control module 52.

The acoustic imaging device 300 includes an acoustic in/out transducer 302, an acoustic detection circuit 304, and an acoustic imaging processing module 310. The acoustic imaging processing module 310 may be part of the processing module(s) 42. The acoustic imaging device 300 is both an input and output device. The acoustic in/out transducer 302 is similar to the audible in/out transducer in that it functions to convert sound to and from an electrical signal. However, the acoustic in/out transducer 302 is affected by high frequency sound waves used for object detection and measurement that may be out of the human audible range (e.g., greater than 20 kHz). For example, the acoustic in/out transducer 302 is an ultrasonic piezoelectric transducer that is capable of generating and receiving ultrasonic vibrations.

Due to the unique circuitry of the acoustic detection circuit 304, a single acoustic in/out transducer 302 is operable to both transmit a detection signal and receive a reflected signal. In general, the acoustic detection circuit 304 is operable to drive the single acoustic in/out transducer 302 using a generated detection signal for output while receiving and processing a reflected signal representative of sound from the single acoustic in/out transducer 302. The acoustic detection circuit 304 detects a phase change between the transmitted detection signal and the received reflection signal and provides the phase change to the acoustic imaging processing module 310.

The acoustic imaging processing module 310 is operable to determine a time delay based off of the phase change and determine a distance measurement based off of the time delay. The distance measurement is used to generate imaging information. The acoustic imaging processing module 310 and the acoustic detection circuit 304 will be discussed in greater detail with reference to FIGS. 24-25.

While one acoustic in/out transducer 302 is shown here, multiple acoustic in/out transducers 302 and acoustic detection circuits 304 can be used to generate a plurality of distance measurements to generate three dimensional (3D) image mapping.

The processing module 42 communicates directly with a video graphics processing module 48 to display data on the display 50. The display 50 includes an LED (light emitting diode) display, an LCD (liquid crystal display), and/or other type of display technology. The display has a resolution, an aspect ratio, and other features that affect the quality of the display. The video graphics processing module 48 receives data from the processing module 42, processes the data to produce rendered data in accordance with the characteristics of the display, and provides the rendered data to the display 50. While not shown, the computing device 12 or 13 further includes a BIOS (Basic Input Output System) memory coupled to the core control module 40.

FIG. 3B is a schematic block diagram of another embodiment of a computing device 12 or 13 that includes a core control module 40, one or more processing modules 42, one or more main memories 44, cache memory 46, a video graphics processing module 48, a touch screen with sensors and drive sense circuits (DSC) 16, an Input-Output (I/O) peripheral control module 52, one or more input interface modules 56, one or more output interface modules 58, one or more network interface modules 60, and one or more memory interface modules 62. The touch screen with sensors and drive sense circuits (DSC) 16 includes a touch screen display integrated with a plurality of sensors 80, a plurality of drive-sense circuits (DSC), and a touch screen processing module 82. The computing device 12 or 13 of FIG. 3A may also include one or more audio in/out devices and/or one or more acoustic imaging devices 300 as discussed with reference to FIGS. 2-3A.

The computing device 12 or 13 operates similarly to computing device 12 or 13 of FIGS. 2 and 3 with the addition of a touch screen with sensors and drive sense circuits (DSC) 16 as an input device. The touch screen with sensors and drive sense circuits (DSC) is integrated with a plurality of sensors (e.g., electrodes, capacitor sensing cells, capacitor sensors, inductive sensor, etc.) to detect a proximal touch of the screen. For example, when one or more fingers touches the screen, capacitance of sensors proximal to the touch(es) are affected (e.g., impedance changes).

Each sensor of the touchscreen with sensors and drive sense circuits (DSC) 16 is coupled to a drive-sense circuit (DSC). The DSCs provide electrode signals to the sensors and detect changes in electrical characteristics of the sensors. The DSCs will be described in greater detail with reference to FIGS. 26-29 and as described in co-pending patent application entitled, "DRIVE SENSE CIRCUIT WITH DRIVE-SENSE LINE," having a serial number of Ser. No. 16/113,379, and a filing date of Aug. 27, 2018. The drive-sense circuits (DSC) provide a representation of the detected change to the touch screen processing module 82, which may be a separate processing module or integrated into the processing module 42.

The touch screen processing module 82 processes the representative signals from the drive-sense circuits (DSC) to determine the location of the touch(es). This information is inputted to the processing module 42 for processing as an input. For example, a touch represents a selection of a button on screen, a scroll function, a zoom in-out function, etc.

FIG. 4 is a schematic block diagram of an embodiment of an audio in/out device 65 that includes an audible in/out transducer 32 and an audio transmit/receive (RX/TX) circuit 35. The audio in/out device 65 requires a single transducer for both audio input and output functionality.

Transducers are operable to convert one form of energy (e.g., pressure, temperature, biological, chemical, etc.) to another (e.g., capacitance, inductance, impedance, current, voltage, etc.). For example, a microphone is a transducer that is operable to convert the air pressure variations of a sound wave into an electrical signal and a speaker is a transducer that is operable to convert an electrical signal into a sound wave for output. In conventional audio devices, for every microphone transducer, there is a corresponding speaker transducer. However, due to the unique circuitry of the audio receive/transmit (RX/TX) circuit 35, a single audible in/out transducer 32 is operable as both a microphone and a speaker.

In an example of operation, an audible input signal 84 (e.g., sound waves) changes the electrical characteristics of the audible in/out transducer 32 which produces an audio RX signal 86. For example, the audible in/out transducer 32 is a piezoelectric transducer that generates an electric charge (and thus the electrical audio RX signal 86) in response to the presence of sound waves due to the piezoelectric effect. The audio RX/TX circuit 35 receives the audio RX signal 86 produced by the audible in/out transducer 32.

The audio RX/TX circuit 35 is further operable to receive a digital TX signal 92 (e.g., from a processing module, etc.) that contains audio information for transmission to the audible in/out transducer 32. The audio RX/TX circuit 35 regulates the audible in/out transducer 32 voltage to be substantially equal to a voltage reference signal based on the digital TX signal 92 such that the digital TX signal 92 is transmitted to the audio RX/TX circuit 35 and the effect of the audio RX signal 86 is removed. The electrical characteristics of the audible in/out transducer 32 are affected by the audio TX signal 94 which produces an audible output signal 96 (e.g., sound waves).

To regulate the audible in/out transducer 32 voltage, the audio RX/TX circuit 35 detects and compensates for the effect of the audio RX signal 86 on the audible in/out transducer 32 voltage. Thus, the output of the audio RX/TX circuit 35 is a digital Tx/Rx signal 88 which includes a representation of the audio RX signal 86 and a transmit signal (delayed due to circuitry lag). With further processing, the audio RX signal can be extracted from the digital Tx/Rx signal 88. The audio RX/TX circuit 35 and the signals of the audio/in out device 65 will be discussed in more detail with reference to FIGS. 5-17.

FIG. 5 is a schematic block diagram of an embodiment of an audio in/out device 65 that includes an audible in/out transducer 32 and an audio transmit/receive (RX/TX) circuit 35. FIG. 5 operates similarly to the audio in/out device 65 of FIG. 4 except that the audio RX/TX circuit 35 is described in more detail. The audio RX/TX circuit 35 includes a non-inverting operational amplifier (op-amp) 100, an analog to digital converter (ADC) 102, a digital to analog converter (DAC) module 104, a feedback circuit 106, and a controlled source circuit 108.

The controlled source circuit 108 may be implemented in a variety of ways. For example, the controlled source circuit 108 is a current mirror circuit sourced via a DC input voltage. As another example, the controlled source circuit 108 is a current controlled current source or a voltage controlled current source. As yet another example, the controlled source circuit 108 is a bidirectional dependent voltage source circuit or a bidirectional dependent current source circuit (e.g., a Howland current pump circuit that produces a voltage controlled current and requires one op-amp and multiple resistors).

The feedback circuit 106 may be implemented with a controlled source regulation circuit, a biasing circuit, a wire, etc. The ADC 102 may be implemented as one of: a flash ADC, a successive approximation ADC, a ramp-compare ADC, a Wilkinson ADC, an integrating ADC, a delta encoded ADC, and/or a sigma-delta ADC of desired resolution (e.g., 8-bit, 16-bit, 32-bit, etc.).

The DAC module 104 includes a DAC. The DAC may be implemented as one of: a sigma-delta DAC, a pulse width modulator DAC, a binary weighted DAC, a successive approximation DAC, and/or a thermometer-coded DAC of desired resolution (e.g., 8-bit, 16-bit, 32-bit, etc.).

In an example of operation, the DAC module 104 receives a digital TX signal 92 (e.g., from a processing module, etc.) that includes audio information for transmission to the audible in/out transducer 32. The DAC module 104 generates an analog voltage reference signal (TX reference signal 95) based on the digital TX signal 94. The TX reference signal 95 includes a DC component and an oscillating component. The DAC module 104 and the TX reference signal 95 will be described in greater detail with reference to FIGS. 6-7.

An audible input signal 84 (e.g., sound waves) changes the electrical characteristics of the audible in/out transducer 32 such that the audible in/out transducer 32 produces an audio RX signal 86. The audio RX signal 86 affects the voltage on the audible in/out transducer 32 caused by transmitting an audio TX signal 94. The op-amp 100 compares the voltage of the audible in/out transducer 32 with the TX reference signal 95 to produce an analog comparison signal (Vout). For a non-inverting op-amp with unity gain, Vout is equal to the current on the audible in/out transducer 32 (e.g., a result of the audio RX signal 86 and the audio TX signal 94 currents) multiplied by an I-to-V loop gain. The I-to-V loop gain is the ratio of how much the voltage output changes as a result of a current change on the audible in/out transducer 32. The I-to-V loop gain is very high which allows for very small current changes (e.g., micro-amp differences) to be detected. For example, there can be a greater than 100 dB TX to RX ratio (e.g., 120 dB ratio) and still be able to detect the RX signal. As such, the Vout signal follows the current on the audible in/out transducer 32 and includes a representation of the audio RX signal 86 and a delayed audio TX signal 94 (due to circuitry delay).

The feedback circuit 106 generates a regulation signal 91 based on the Vout signal and provides the regulation signal 91 to the controlled source circuit 108. The regulation signal 91 may be the Vout signal (e.g., when the feedback circuit is a wire) or a processed version of the Vout signal depending on the components of the feedback circuit 106 and input requirements of the controlled source circuit 108.

The controlled source circuit 108 adjusts generation of its output based on the regulation signal 91 to compensate for the effects that the audio RX signal 86 has on the audible in/out transducer 32 voltage to keep the inputs of the op-amp 100 substantially matching. The output of the controlled source circuit 108 has a DC component and oscillating component such that the audible in/out transducer 32 voltage as measured at the op-amp 100 input will have a substantially matching DC component and oscillating component as the TX reference signal 95. Thus, the audio RX/TX circuit 35 operates as a control loop that regulates the audible in/out transducer 32 voltage to substantially match the voltage of the TX reference signal 95 by compensating for the effect that the audio RX signal 86 has on the audible in/out transducer 32 voltage.

The ADC 102 converts the Vout signal to a digital Tx/Rx signal 88 for output. The digital Tx/Rx signal 88 undergoes further processing such that the correct delayed transmit signal is extracted from the digital Tx/Rx signal 88 to produce the correct digital audio RX signal. A transmit signal delay occurs due to the circuitry lag in transmitting the TX reference signal 95 through the circuitry of the audio RX/TX circuit 35. For example, the bandwidth of the audio RX/TX circuit 35 is approximately 1 MHz, resulting in an approximately 1 microsecond delay between receiving the audio RX signal 86 and transmitting audio TX signal 94. Further processing of the digital Tx/Rx signal 88 is discussed in greater detail with reference to FIGS. 11-15.

In another embodiment, the audio RX/TX circuit 35 further includes a DAC connected to the output of the ADC 102 and the input of the feedback circuit 106. Instead of providing the Vout signal at the output of the op-amp 100 to the feedback circuit 106, the Vout signal is provided to the ADC 102 and converted to the digital Tx/Rx signal 88. The digital Tx/Rx signal 88 is provided to the DAC where the DAC converts the digital Tx/Rx signal 88 to an analog signal. The DAC then provides the analog signal to the feedback circuit 106 where the feedback circuit 106 converts the analog signal to the regulation signal 91.

FIG. 6 is a schematic block diagram of an embodiment of a digital to analog converter (DAC) module 104 that includes a DAC 105, a DC (direct current) reference voltage source 107, and a summing circuit. The DAC 105 may be implemented in a variety of ways. For example, the DAC is one of: a sigma-delta DAC, a pulse width modulator DAC, a binary weighted DAC, a successive approximation DAC, and/or a thermometer-coded DAC of adequate resolution (e.g., 8-bit, 16-bit, 32-bit, etc.).

The DAC 105 converts a digital TX signal 92 (received from a processing module, etc.) to an analog TX signal 93 having a waveform (e.g., sinusoidal (as shown), square, triangular, polygonal, multiple step, etc.), a frequency, a phase, and a magnitude. The DC reference voltage source 107 produces a DC reference 97 component of the TX reference signal 95. The DC reference 97 is a DC voltage at a desired DC level. For example, the DC reference 97 is set and/or adjusted to a desired magnitude to avoid op-amp saturation and to stay within the operating range of the op-amp. The summing circuit combines the analog TX signal 93 with the DC reference 97 to produce the TX reference signal 95.

FIG. 7 is an example of a transmit (TX) reference signal 95 in the time domain. The TX reference signal 95 includes an analog TX signal 93 and a DC (direct current) reference 97 component. The analog TX signal 93 is an oscillating component of the transmit (TX) reference signal 95 having a waveform (e.g., sinusoidal (as shown), square, triangular, polygonal, multiple step, etc.), a frequency, a phase, and a magnitude. The DC reference 97 component is at a particular magnitude. For example, the DC reference 97 is a DC voltage in the range of a few hundred milli-volts to tens of volts or more.

The frequency of the analog TX signal 93 may vary so that it can be tuned to the impedance of the audible in/out transducer and/or to be off-set in frequency from other sensor signals in a system. For example, a capacitance sensor's impedance decreases with frequency. As such, if the frequency of the oscillating component is too high with respect to the capacitance, the capacitor looks like a short and variances in capacitances will be missed. Similarly, if the frequency of the oscillating component is too low with respect to the capacitance, the capacitor looks like an open and variances in capacitances will be missed.

FIG. 8 is a schematic block diagram of an embodiment of an audio input/output device 65 in a microphone (mic) only mode. The audio input/output device 65 operates similarly to the audio input/output device 65 of FIGS. 4-5 and includes an audible in/out transducer 32 and a portion of an audio RX/TX circuit 35. The portion of the audio RX/TX circuit 35 shown includes an non-inverting op-amp 100, a feedback circuit 106, and a controlled source circuit 108.

In this example, the controlled source circuit 108 is a voltage controlled current source (bidirectional or one directional) that produces a current signal to keep the inputs to the op-amp 100 substantially matching. The op-amp 100 is powered by a positive supply Vdd and a negative supply Vss. Voltage that is common between either of the op-amp 100 inputs and ground is referred to as common mode voltage (Vcm).

In a microphone only mode, the TX reference signal 95 is a voltage reference signal set to a common mode voltage (Vcm) of zero because there is no audio transmit signal to output to the audible in/out transducer 32. The electrical characteristics of the audible in/out transducer 32 change based on a received audible input signal 84 (sound waves) and the changes in electrical characteristics produce a current signal. The current signal produced by the controlled source circuit 108 as affected by the current signal produced by the audible in/out transducer 32 is represented as the current signal "I."

The op-amp 100 compares the audible in/out transducer 32 voltage (Vin_1) with the TX reference signal 95 (Vin_2) to produce an analog comparison signal Vout. The output of the op-amp 100 (Vout) varies based on the current signal I such that Vout includes a representation of the audible input signal 84. The feedback circuit 106 generates a regulation signal 91 based on the Vout signal and provides the regulation signal 91 to the controlled source circuit 108. The controlled source circuit 108 adjusts generation of its current signal output based on the regulation signal 91 so that the audible in/out transducer 32 voltage remains substantially equal to the TX reference signal 95 (e.g., at zero volts).

FIG. 8A is an example of signals of the audio in/out device 65 of FIG. 8 when the audio in/out device 65 is operating in a microphone (mic) only mode. The bolded signal is the current signal I. The current signal I is the current signal produced by the controlled source circuit 108 as affected by the current signal generated by the audible in/out transducer 32 due to the audible input signal 84.

The TX reference signal 95 (Vin_2) is set to a common mode voltage (Vcm) at zero volts because there is no audio transmit signal to output to the audible in/out transducer 32. Therefore, both Vin_1 and Vin_2 are shown as flat lines at Vcm (e.g., at zero). The voltage output signal Vout follows the current signal I and has a high I-to-V gain. Thus, Vout includes a representation of the current generated based on the audible input signal 84. The output signal Vout is further processed to accurately extract the representation of the current generated based on the audible input signal 84.

FIG. 9 is a schematic block diagram of an embodiment of an audio input/output device 65 in a microphone (mic) and speaker mode. The audio input/output device 65 operates similarly to the audio input/output device 65 of FIGS. 4-5 and includes an audible in/out transducer 32 and a portion of the audio RX/TX circuit 35. The portion of the audio RX/TX circuit 35 includes the non-inverting op-amp 100, the feedback circuit 106, and the controlled source circuit 108.

In this example, the controlled source circuit 108 is a voltage controlled current source (bidirectional or one directional) that produces a current signal to keep the inputs to the op-amp 100 substantially equal. In a microphone and speaker mode, the TX reference signal 95 is a voltage reference signal (Vin_2) set to a particular output voltage signal representative of the audio transmit signal for transmission to the audible in/out transducer 32.

The electrical characteristics of the audible in/out transducer 32 change based on a received audible input signal 84 (sound waves) to produce a current signal. The current produced by the controlled source circuit 108 as affected by the current signal produced by the audible in/out transducer 32 is represented as the current signal "I." The electrical characteristics of the audible in/out transducer 32 change based on the current signal produced by the controlled source circuit and the changes in electrical characteristics produce an audible output signal 96.

As the electrical characteristics of the audible in/out transducer 32 change due to the audible input signal 84 the current signal provided by the controlled source circuit 108 changes so that the audible in/out transducer 32 voltage (Vin_1) remains substantially equal to the TX reference signal 95 (Vin_2). The op-amp 100 compares the audible in/out transducer 32 voltage (Vin_1) with the TX reference signal 95 (Vin_2) to produce a comparison signal Vout. The output of the op-amp 100 (Vout) varies based on the current signal I such that Vout includes a representation of the audible input signal 84 and a transmit signal (delayed due to circuitry lag).

The feedback circuit 106 generates a regulation signal 91 based on the Vout signal and provides the regulation signal 91 to the controlled source circuit 108. The controlled source circuit 108 adjusts generation of its current signal output based on the regulation signal 91 to keep the inputs of the op-amp 100 substantially matching. The current signal output is received by the audible in/out transducer which causes electrical characteristic changes in the audible in/out transducer 32 to produce the audible output signal 96 (e.g., sound waves).

FIGS. 9A-9D are examples of signals of the audio in/out device 65 of FIG. 9 when the audio in/out device 65 is operating in a microphone (mic) and speaker mode. While pure tones sinusoids are shown for simplicity purposes, other waveforms can be used.

FIG. 9A shows an example of transmit signals of the audio in/out device 65. The TX reference signal 95 (Vin_2) is an analog voltage reference signal generated based on a desired transmit signal for transmission to the audible in/out transducer 32. The voltage signal on the audible in/out transducer 32 (Vin_1) is regulated by the current signal produced by the controlled source circuit so that it substantially matches the TX reference signal 95 (Vin_2).

As such, the Vin_1 signal is regulated to be substantially equal to the signal Vin_2 signal as shown. Here, example sinusoidal signals Vin_1 and Vin_2 are shown having a magnitude within the voltage supply rails (Vdd and Vss) of the op-amp 100.

FIG. 9B shows a signal representative of the electrical variation of the audible in/out transducer 32 due to the audible input signal 84. When voltage is regulated, the audible in/out transducer 32 current, impedance, and/or other electrical characteristics vary. When current is regulated, the audible in/out transducer 32 voltage, impedance, and/or other electrical characteristics vary.

FIG. 9C shows a signal representative of current variation of the audible in/out transducer 32 from audio out compared with a signal representative of the current variation of the audible in/out transducer 32 due to audio in. A combination of the two current signals represents the current on the audible in/out transducer which affects the voltage of the audible in/out transducer.

FIG. 9D shows an output signal Vout that is generated at the output of an op-amp when the inputs to the op-amp include the audible in/out transducer 32 voltage (e.g., Vin_1 affected by the current variation of the audible in/out transducer 32 due to audio out and the current variation of the audible in/out transducer 32 due to audio in) and the TX reference signal (Vin_2).

The output signal Vout follows the combination of the current variations of FIG. 9C such that Vout includes a representation of the audible input signal and a transmit signal. The output signal Vout requires further signal processing to extract the representation of the audible input signal while taking into account transmit signal delay.

FIG. 10 is a schematic block diagram of an audio in/out device 65 that includes an audible in/out transducer 32, an audio receive/transmit (RX/TX) circuit 35, an audio codec module 80, and an interface module 82. The audible in/out transducer 32 and the audio RX/TX circuit 35 operate similarly to the audio in/out devices 65 of previous Figures. The audio codec module 80 is operable extract a digital Rx signal from the digital Tx/Rx signal while taking into account transmit signal delay, format a digital Rx signal into a desired audio file format, and format an audio file into digital signals for transmitting to the audio RX/TX circuit 35.

An audio file format is a file format for storing digital audio data on a computer system. The three major groups of audio file formats include uncompressed audio format (e.g., waveform audio file format (WAV), audio interchange file format (AIFF), Au file format, etc.), lossless compressed audio format (e.g., free lossless audio codec (FLAC), Monkey's Audio, WavPack, moving picture experts group-4 (MPEG-4), Windows media audio lossless (WMA LossLess), etc.), and lossy compressed audio format (e.g., Opus, moving picture experts group-1 (MP3), Vorbis, Advanced Audio Coding (AAC), etc.).

Digital audio file formats are associated with a sampling rate. According to the Nyquist-Shannon sampling theorem (stating that sampling frequency must be greater than twice the maximum frequency one wishes to reproduce), audio sampling rate should be greater than 40 kHz because the human hearing range is between approximately 20 Hz to 20,000 Hz. For example, MP3 uses a sampling rate of 44.1 kHz. High resolution audio refers to audio files having a higher sampling frequency and/or bit depth than audio file formats at 44.1 kHz/16-bit. For example, WAV and FLAC use a sampling rate of 48 kHz or higher. Based on the desired digital inbound signal 90 formatting, the audio codec module 80 is operable to format (e.g., up-sample, down-sample, encode, compress, etc.) the digital Rx signal component of the digital Tx/Rx signal 88 accordingly.

In addition to audio file formatting, the audio codec module 80 is operable to adjust for transmit signal delays, adjust the magnitude of the digital outbound data 92 (e.g., volume control), and pre-scale the digital outbound signal 92. Pre-scaling reduces a high frequency signal to a lower frequency by integer division.

The interface module 82 includes a software driver and a hardware connector for coupling the audio codec module 80 of the audio in/out device 92 to other modules/devices of a computing device (e.g., a processing module) and/or a communication system. The interface module 82 may include one or more digital filters, a delay circuit, a digital to analog converter (DAC), an analog to digital converter (ADC), a buffer, etc., to coordinate timing of data flow and ensure compatibility of connected devices/components.

The interface module 82 is further operable transmit the digital inbound signal 90 in accordance with one or more inbound communication protocols and receive the digital outbound signal 92 in accordance with one or more outbound communication protocols.

For example, the interface module 82 formats digital inbound data in accordance with one or more wireless communication standards (e.g., GSM, CDMA, WCDMA, HSDPA, HSDPA, WiMAX, EDGE, GPRS, IEEE 802.11, Bluetooth, ZigBee, universal mobile telecommunications system (UMTS), long term evolution (LTE), IEEE 802.16, evolution data optimized (EV-DO), etc.). Such a conversion may include one or more of: digital intermediate frequency to baseband conversion, time to frequency domain conversion, space-time-block decoding, space-frequency-block decoding, demodulation, frequency spread decoding, frequency hopping decoding, beamforming decoding, constellation demapping, deinterleaving, decoding, depuncturing, and/or descrambling.

In an example of operation, the audible in/out transducer 32 is operable to provide an audio RX signal to the audio RX/TX circuit 35 based on a received audible input signal (e.g., sound waves). The audio RX/TX circuit 35 outputs a digital Tx/Rx signal 88 to the audio codec module 80 where the digital Tx/Rx signal 88 includes a representation of the audio RX signal.

The audio codec module 80 processes the digital Tx/Rx signal 88 to extract a digital audio Rx portion of the digital Tx/Rx signal 88 and format it into a desired audio file format to produce a digital inbound signal 90. For example, the audio codec module 80 encodes and compresses a digital audio RX signal into a lossless compressed audio format. The interface module 82 may further process the digital inbound signal 90 (e.g., via digital filtering) and/or control the digital inbound signal 90 (e.g., delay, buffer) such that is transmitted to another module and/or device correctly and/or in accordance with one or more communication protocols.

Likewise, the interface module 82 is operable to receive an audio file for transmission to the audible in/out transducer 32 (e.g., via a processing module, etc.). The interface module 82 may process the audio file (e.g., via digital filtering) to produce a digital outbound signal 92 and/or control the transmission of the digital outbound signal 92 (e.g., delay, buffer) so that is received correctly by the audio codec module 80. The audio codec module 80 is operable to process the digital outbound signal 92 to produce the digital TX signal 92. For example, the audio codec module 80 decodes and decompresses the digital outbound signal 92 having a particular audio file format to produce the digital TX signal 92.

The audio RX/TX circuit 35 receives the digital TX signal 92 from the audio codec module 80 and converts it to an audio TX signal for transmission to the audible in/out transducer 32 for output as sound.

FIG. 11 is a schematic block diagram of an audio in/out device 65 that includes an audible in/out transducer 32, an audio receive/transmit (RX/TX) circuit 35, and an audio codec module 80. The audio RX/TX circuit 35 includes a non-inverting operational amplifier (op-amp) 100, an analog to digital converter (ADC) 102, a digital to analog converter (DAC) module 104, a feedback circuit 106, and a controlled source circuit 108. The audio RX/TX circuit 35 and the audible in/out transducer 32 operate similarly to the audio RX/TX circuit 35 and the audible in/out transducer 32 of previous Figures.

The audio codec module 80 includes a delay circuit 110, a level adjust circuit 114, a summing circuit 115, and an audio file formatting module 116. The delay circuit 110 may be implemented using a timer circuit (e.g., a digital timer circuit using flip flops). The level adjust circuit 114 may be implemented by cascaded and differentially switched complimentary metal-oxide semiconductor (CMOS) transistors, by a non-inverting op-amp level shifter, etc. The delay circuit 110 may also include level adjust functionality to adjust the magnitude of the delayed signal.

The audio file formatting module 116 is operable to format digital signals into a desired audio file format for output and to format received digital audio files into digital signals for transmitting to the audio RX/TX circuit 35. For example, the audio file formatting module 116 is operable to up-sample, down-sample, digital filter, encode/decode, and compress/decompress signals to achieve a desired result. The audio file formatting module 116 is further operable to generate control signals to adjust for transmit signal delays, generate control signals to adjust the magnitude of the digital outbound data (e.g., volume control 120), and pre-scale the digital outbound signal 92. Pre-scaling reduces a high frequency signal to a lower frequency by integer division.

In an example of operation, the audio file formatting module 116 receives a digital outbound signal 92 (e.g., from a processing module via an interface module). The audio file formatting module 116 formats the digital outbound signal 92 into a desired digital transmit signal. The audio file formatting module 116 pre-scales the digital outbound signal 92 to produce the pre-scaled digital TX signal 93. The audio file formatting module 116 communicates a volume control signal 120 to the level adjust circuit 114. The level adjust circuit 114 adjusts the magnitude of the pre-scaled digital TX signal 93 in accordance with the volume control signal 120 to produce the digital TX signal 92. The digital TX signal 92 is provided to the DAC module 104 of the audio RX/TX circuit 35 and processed by the audio TX/RX circuit 35 as discussed with reference to previous Figures.

The audio file formatting module 116 communicates a delay control signal 118 to the delay circuit 110. The delay control signal 118 corresponds to the circuitry lag of the audio RX/TX circuit 35. The circuitry lag can be determined by disconnecting the audible in/out transducer 32 so that there is no audio signal received, applying a digital TX signal, and adjusting the delay circuit so that the output of the summing circuit is approximately zero.

The delay control signal 118 further includes a magnitude scale signal corresponding to an amount the magnitude of the digital TX signal 92 needs to be scaled to match the magnitude of the transmit component of the digital Tx/Rx signal 88. The digital Tx/Rx signal 88 is a digital voltage signal representative of the current changes on the audible in/out transducer 32. Therefore, the digital Tx/Rx signal 88 includes a voltage representation of a transmit current signal as affected by a receive current signal where the voltage representations are affected by the I-to-V gain of the audio RX/TX circuit 35 loop. To determine the magnitude of the transmit component of the digital Tx/Rx signal 88, the impedance of the audio in/out transducer 32 and the gain of the audio RX/TX circuit 35 loop need to be determined. These values can be determined by a calibration process where the gain of the audio RX/TX circuit 35 loop and the impedance of the of the audio in/out transducer 32 are measured while no audio RX signal is received.

The digital TX signal 92 is provided to the delay circuit 110 where the delay circuit 110 delays and magnitude adjusts the digital TX signal in accordance with the delay control signal 118 to produce a delayed digital TX signal 97. For example, the bandwidth of the audio RX/TX circuit 35 is approximately 1 MHz, resulting in an approximately 1 microsecond delay between generating the TX reference signal and transmitting an audio TX signal 94. Thus, the delay circuit 110 holds the digital TX signal 92 for approximately 1 microsecond to correct for the circuitry lag.

The summing circuit 115 receives the digital Tx/Rx signal 88 from the audio RX/TX circuit 35 and subtracts the delayed digital TX signal 97 from the digital Tx/Rx signal 88 to produce a digital RX signal 89. With the delayed and magnitude adjusted digital TX signal 97, the correct transmit signal is subtracted from the digital Tx/Rx signal 88 such that the correct digital Rx signal 89 is produced. The audio file formatting module 116 formats the digital Rx signal 89 into a desired audio file format to produce the digital inbound signal 90.

FIG. 12 is an example of signals of the audio in/out device 65 of FIG. 11. The audio codec module 80 of FIG. 11 outputs a digital TX signal 92 to the audio RX/TX circuit 35. The digital Tx/Rx signal 88 is output from the audio RX/TX circuit 35 at some time after the digital TX signal 92 is received by the audio RX/TX circuit 35 due to circuitry lag (e.g., approximately 1 microsecond). The digital Tx/Rx signal 88 is a digital voltage signal representative of the current changes on the audible in/out transducer 32. Therefore, the digital Tx/Rx signal 88 includes a voltage representation of a transmit current signal (blue) as affected by a receive current signal (red) where the voltage representations are affected by the I-to-V gain of the audio RX/TX circuit 35 loop.

In order to subtract the correct digital TX signal from the digital Tx/Rx signal 88 to produce the digital RX signal 89, the digital TX signal is delayed by the delay circuit by the amount of circuitry lag. In addition to delaying the digital TX signal, the delay circuit adjusts the magnitude of the digital TX signal based on the impedance of the audible in/out transducer and the gain of the audio RX/TX circuit 35 loop such that the magnitude of the delayed digital TX signal matches the magnitude of the transmit component of the digital Tx/Rx signal 88. Thus, subtracting the delayed digital TX signal 97 from the digital Tx/Rx signal 88 produces the correct digital RX signal 89 as shown at the bottom of the Figure.

FIG. 13 is a schematic block diagram of an audio in/out device 65 that includes an audible in/out transducer 32, an audio receive/transmit (RX/TX) circuit 35, and an audio codec module 80. FIG. 13 operates similarly to FIG. 11 except that the audio codec module 80 of FIG. 13 includes a gain stage after the summing circuit 115. The gain stage may be implemented by a non-inverting op-amp with variable resistors where the variable resistors can be adjusted to achieve a desired gain. The gain stage is operable to amplify the digital RX signal 89 to a level desired for input to the audio file formatting module 116.