Display apparatus and control device

Iuchi , et al. April 27, 2

U.S. patent number 10,990,340 [Application Number 16/442,064] was granted by the patent office on 2021-04-27 for display apparatus and control device. This patent grant is currently assigned to Japan Display Inc.. The grantee listed for this patent is Japan Display Inc.. Invention is credited to Tsutomu Harada, Shinya Iuchi, Hayato Kurasawa, Yuji Suzuki, Masahiro Togashi.

View All Diagrams

| United States Patent | 10,990,340 |

| Iuchi , et al. | April 27, 2021 |

Display apparatus and control device

Abstract

A display apparatus includes a plurality of display panels arranged in a matrix, each of the image display panel includes a plurality of drive electrodes extending in a first direction and a plurality of detection electrodes extending in a second direction crossing the first direction, wherein an AC voltage is sequentially applied to the plurality of drive electrodes of a first display panel, and the plurality of detection electrodes of a second display panel adjacent to the first display panel detect a signal output from the plurality of drive electrodes of the first display panel.

| Inventors: | Iuchi; Shinya (Tokyo, JP), Kurasawa; Hayato (Tokyo, JP), Togashi; Masahiro (Tokyo, JP), Harada; Tsutomu (Tokyo, JP), Suzuki; Yuji (Tokyo, JP) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Applicant: |

|

||||||||||

| Assignee: | Japan Display Inc. (Tokyo,

JP) |

||||||||||

| Family ID: | 1000005515714 | ||||||||||

| Appl. No.: | 16/442,064 | ||||||||||

| Filed: | June 14, 2019 |

Prior Publication Data

| Document Identifier | Publication Date | |

|---|---|---|

| US 20190294294 A1 | Sep 26, 2019 | |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | Issue Date | ||

|---|---|---|---|---|---|

| 15243309 | Aug 22, 2016 | 10324559 | |||

Foreign Application Priority Data

| Sep 1, 2015 [JP] | 2015-172141 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G06F 3/1446 (20130101); G06F 3/0445 (20190501); G06F 3/041661 (20190501); G06F 3/0446 (20190501); G09G 2320/0693 (20130101); G09G 2340/0464 (20130101); G06F 2203/04101 (20130101); G09G 2356/00 (20130101) |

| Current International Class: | G06F 3/044 (20060101); G06F 3/14 (20060101); G06F 3/041 (20060101) |

References Cited [Referenced By]

U.S. Patent Documents

| 2005/0231474 | October 2005 | Su et al. |

| 2005/0285811 | December 2005 | Kawase et al. |

| 2006/0077116 | April 2006 | Chen |

| 2007/0247422 | October 2007 | Vertegaal et al. |

| 2011/0267293 | November 2011 | Noguchi |

| 2012/0133674 | May 2012 | Takishita et al. |

| 2012/0218482 | August 2012 | Hwang et al. |

| 2012/0262389 | October 2012 | Kida |

| 2013/0328757 | December 2013 | Matsumoto et al. |

| 2014/0132534 | May 2014 | Kim |

| 2014/0199944 | July 2014 | Ran et al. |

| 2015/0213782 | July 2015 | Yan et al. |

| 2015/0338943 | November 2015 | Donnelly et al. |

| 2005-301131 | Oct 2005 | JP | |||

| 2012-128186 | Jul 2012 | JP | |||

| 2015-097090 | May 2015 | JP | |||

Other References

|

Japanese Office Action dated Dec. 11, 2018 in corresponding Japanese Application No. 2015-172141. cited by applicant. |

Primary Examiner: Elahi; Towfiq

Attorney, Agent or Firm: K&L Gates LLP

Parent Case Text

CROSS-REFERENCE TO RELATED APPLICATION

This application is a continuation of U.S. patent application Ser. No. 15/243,309, filed Aug. 22, 2016, which application claims priority from Japanese Application No. 2015-172141, filed on Sep. 1, 2015, the contents of which is incorporated by reference herein in its entirety.

Claims

What is claimed is:

1. A display apparatus comprising: a plurality of display panels arranged in a matrix, each of the image display panel includes a plurality of drive electrodes extending in a first direction and a plurality of detection electrodes extending in a second direction crossing the first direction, wherein an AC voltage is sequentially applied to the plurality of drive electrodes of a first display panel, and the plurality of detection electrodes of a second display panel adjacent to the first display panel detect a signal output from the plurality of drive electrodes of the first display panel, wherein the detection electrodes of the second display panel detect, as the signal output, electric field generated by the AC voltage applied to the drive electrodes of a first display panel, and wherein the second display panel is a different panel from the first display panel.

2. The display apparatus according to claim 1, wherein the AC voltage is sequentially applied to the drive electrodes of each of the display panels, and the detection electrodes of at least one of the display panels other than the display panel to which the AC voltage is applied, detect the signal output from the drive electrodes of at least one of the display panels to which the AC voltage is applied, in order to confirm an array pattern of the plurality of image display panels, and the AC voltage is not applied to the drive electrodes of the display panel other than the display panel to which the AC voltage is applied, such that the drive electrodes of the display panel other than the display panel to which the AC voltage is applied are not driven.

3. The display apparatus according to claim 1, wherein AC voltage is not applied to the drive electrodes of the second display panel.

4. The display device unit according to claim 2, wherein AC voltage is not applied to the drive electrodes of the second display panel.

5. The display apparatus according to claim 1, wherein the detection electrodes of the second display panel have detection voltages in response to the signal output from the drive electrodes of the first display panel, the detection voltages are converted into signals having amplitudes different for each other.

6. The display apparatus according to claim 1, wherein each of the display panels includes a plurality of pixels each having a pixel electrode and a common electrode to generate an electric field there-between.

7. The display apparatus according to claim 6, wherein one of the drive electrodes function as common electrodes of predetermined number of the pixels.

8. The display apparatus according to claim 7, wherein a capacitance between the detection electrodes and the driving electrodes varies depending on an external approaching object on the image display panel.

9. The display apparatus according to claim 2, further comprising a controller that controls the display panels, wherein the controller detects the array pattern among the display panels based on the detection voltage.

10. The display apparatus according to claim 9, wherein the controller detects a positional relationship between the first display panel and the second display panel in which the detection voltage has been generated and detects the array pattern among the display panels based on the positional relationship.

11. The display apparatus according to claim 10, wherein the controller determines the first display panel and the second display panel in which the detection voltage has been generated as display panels adjacent to each other.

12. The display apparatus according to claim 11, wherein the controller sequentially switches the first display panel to another display panel and sequentially detect the adjacent image display panels so as to detect the array pattern among the display panels.

13. The display apparatus according to claim 12, wherein the controller selects all of the display panels to apply the AC voltage to detect the array pattern among the display panels.

14. The display apparatus according to claim 12, wherein, in a case where the same display panel is determined as the adjacent display panel repeatedly, the controller combines information regarding the display panels adjacent to the same display panel to detect the array pattern among the display panels, and when the detection of the adjacent image display panels has been completed for all of the display panels, the controller cancels the application of the AC voltage to the next display panel to make the total number of the display panels applied with the AC voltage smaller than the total number of all of the display panels.

15. The display apparatus according to claim 11, wherein the controller detects misalignment between the adjacent display panels based on the detection voltage.

16. A control device that causes an image display apparatus to display an image, the image display apparatus including a plurality of display panels arranged in a matrix, each of the image display panel includes a plurality of drive electrodes extending in a first direction and a plurality of detection electrodes extending in a second direction crossing the first direction, wherein an AC voltage is sequentially applied to the plurality of drive electrodes of a first display panel, and the plurality of detection electrodes of a second display panel adjacent to the first display panel detect a signal output from the plurality of drive electrodes of the first display panel, wherein the detection electrodes of the second display panel detect, as the signal output, electric field generated by the AC voltage applied to the drive electrodes of a first display panel, and wherein the second display panel is a different panel from the first display panel.

17. The control device according to claim 16, further comprising a controller that controls the display panels, wherein the controller detects the array pattern among the display panels based on the detection voltage.

18. The control device according to claim 17, wherein the controller detects a positional relationship between the first display panel and the second display panel in which the detection voltage has been generated and detects the array pattern among the display panels based on the positional relationship.

19. The control device according to claim 18, wherein the controller determines the first display panel and the second display panel in which the detection voltage has been generated as display panels adjacent to each other.

20. The control device according to claim 19, wherein the controller sequentially switches the first display panel to another display panel and sequentially detect the adjacent image display panels so as to detect the array pattern among the display panels.

Description

BACKGROUND

1. Technical Field

The present disclosure relates to a display device unit including a plurality of image display panels, a control device, and the image display panel.

2. Description of the Related Art

When it is required to display an image on a large screen, for example, for public viewing, a technique called a tiling display is used. For example, the tiling display is a display device unit in which a plurality of image display panels such as liquid crystal displays is arrayed in a flat surface shape such that the plurality of image display panels displays a single image.

In order to display a proper image on the tiling display, it is necessary to understand an array pattern of the image display panels and transmit video signals to the respective image display panels in accordance with this array pattern. For example, the case of a tiling display in which four image display panels are arranged in two rows and two columns is considered. In this case, the identification of an image display panel arranged at first row and first column is needed to transmit, to that image display panel, a video signal of an image corresponding to an upper left part (first row and first column) of an entire image displayed as a whole. When an image corresponding to an upper right part (first row and second column) of the entire image is displayed on the image display panel arranged at the first row and first column, for example, the intended entire image cannot be properly displayed.

As described above, it is required in the tiling display to recognize the array pattern of the image display panels. However, the recognition of the array pattern of the image display panels is difficult in some cases, for example, when the number of the image display panels increases.

For the foregoing reasons, there is a need to provide a display device unit, a control device, and an image display panel capable of easily recognizing the array pattern of the image display panels.

SUMMARY

According to an aspect, a display device includes a plurality of image display panels in such a manner that display surfaces of the plurality of image display panels are orderly arranged on a flat surface, and configured to display an image using the plurality of display surfaces as a single screen. The image display panel includes a drive electrode unit to which an application voltage is applied and a detection electrode unit at which a detection voltage is generated in accordance with the application voltage, and the application voltage is applied solely to the drive electrode unit included in an application image display panel which is a part of the image display panels.

According to another aspect, a control device causes an image display panel unit to display an image. The image display panel unit includes a plurality of image display panels, each of which includes a drive electrode unit and a detection electrode unit, in such a manner that display surfaces of the plurality of image display panels are orderly arranged in a flat surface shape, and configured to display an image using the plurality of display surfaces as a single screen, the control device is configured to apply an application voltage solely to the drive electrode unit included in an application image display panel which is a part of the image display panels; acquire a detection voltage generated at the detection electrode unit in accordance with the application voltage, the detection electrode unit included in a standby image display panel which is the image display panel other than the application image display panel; and confirm an array pattern among the plurality of image display panels based on the detection voltage.

According to another aspect, an image display panel includes a drive electrode unit to which an application voltage is applied; a detection electrode unit at which a detection voltage is generated in accordance with the application voltage; and a panel controller that controls operation of the drive electrode unit and the detection electrode unit. The panel controller puts the detection electrode unit into a state in which the detection voltage is not generated while applying the application voltage to the drive electrode unit, and puts the detection electrode unit into a state in which the detection voltage is enabled to be generated while not applying the application voltage to the drive electrode unit.

BRIEF DESCRIPTION OF THE DRAWINGS

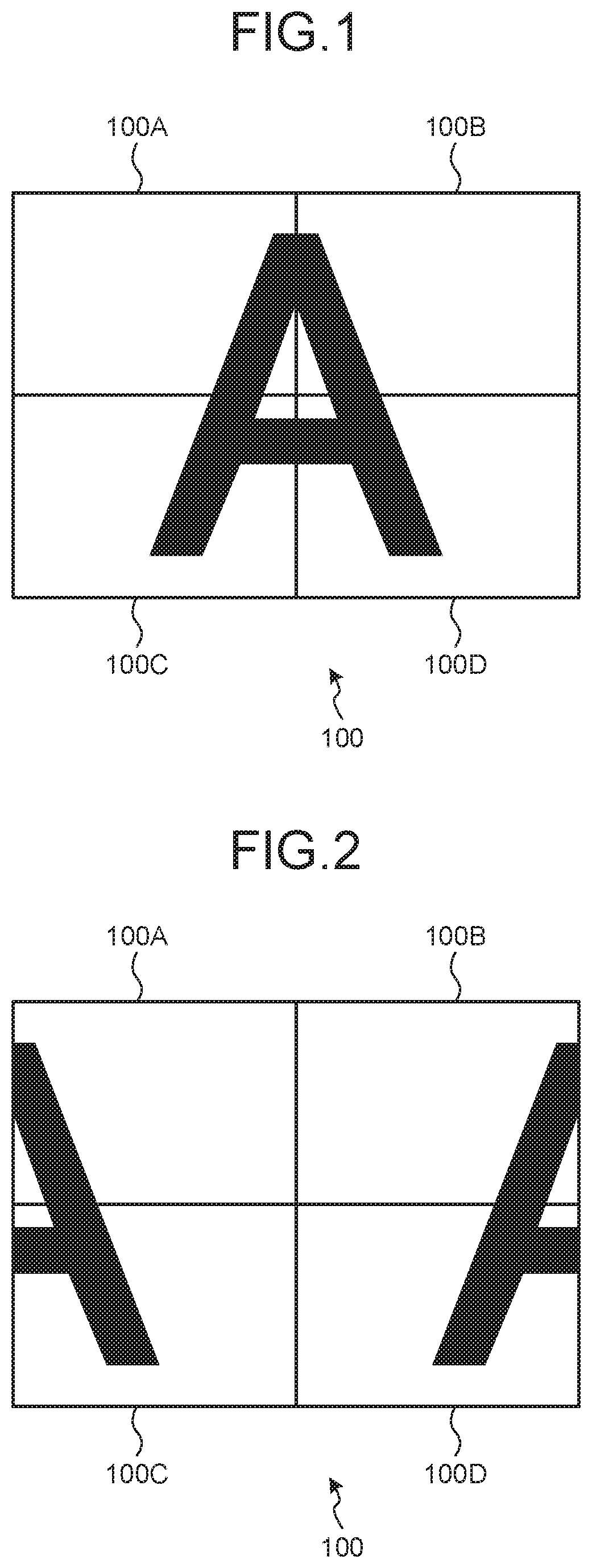

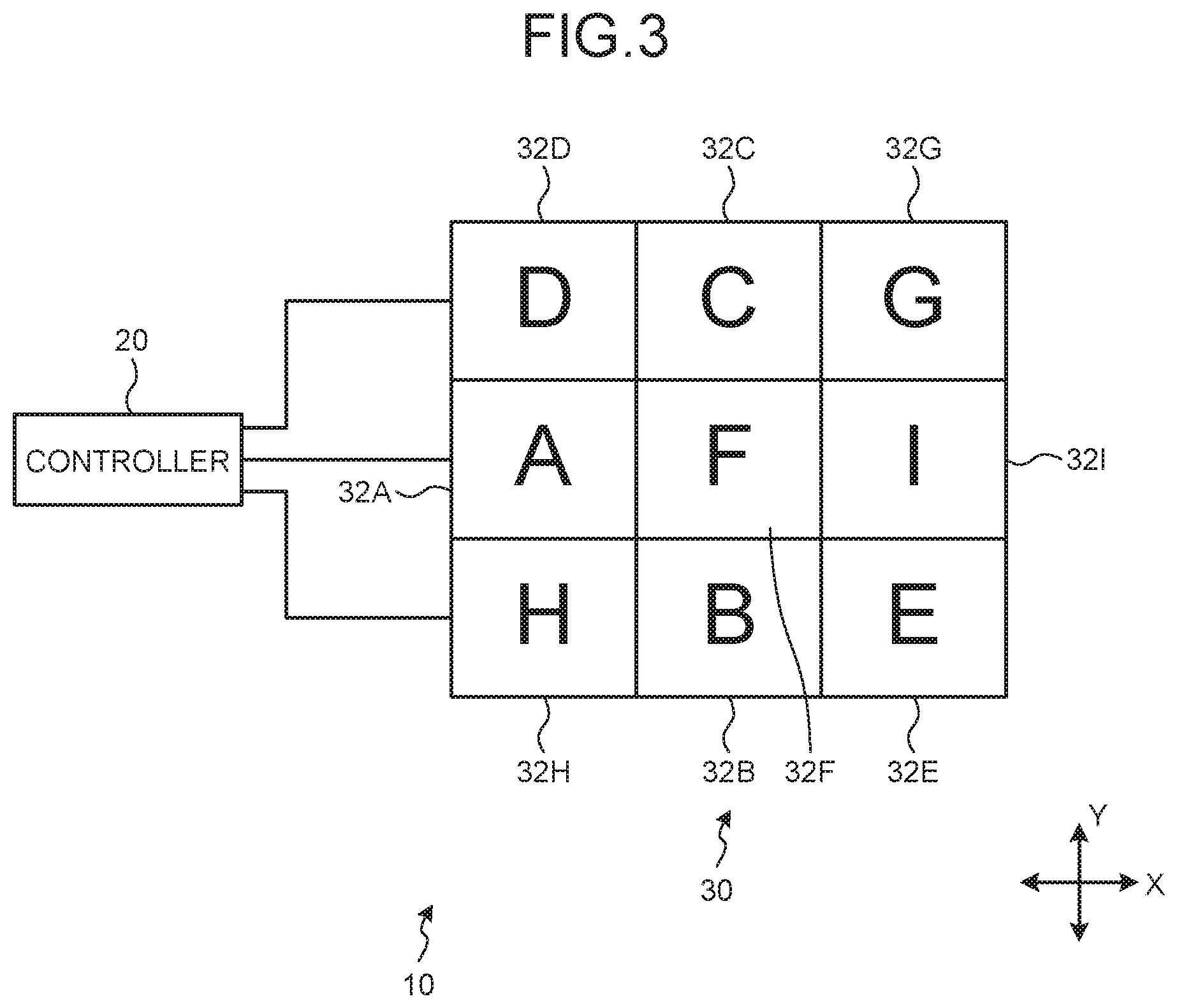

FIG. 1 is an explanatory diagram for explaining a tiling display;

FIG. 2 is an explanatory diagram for explaining the tiling display;

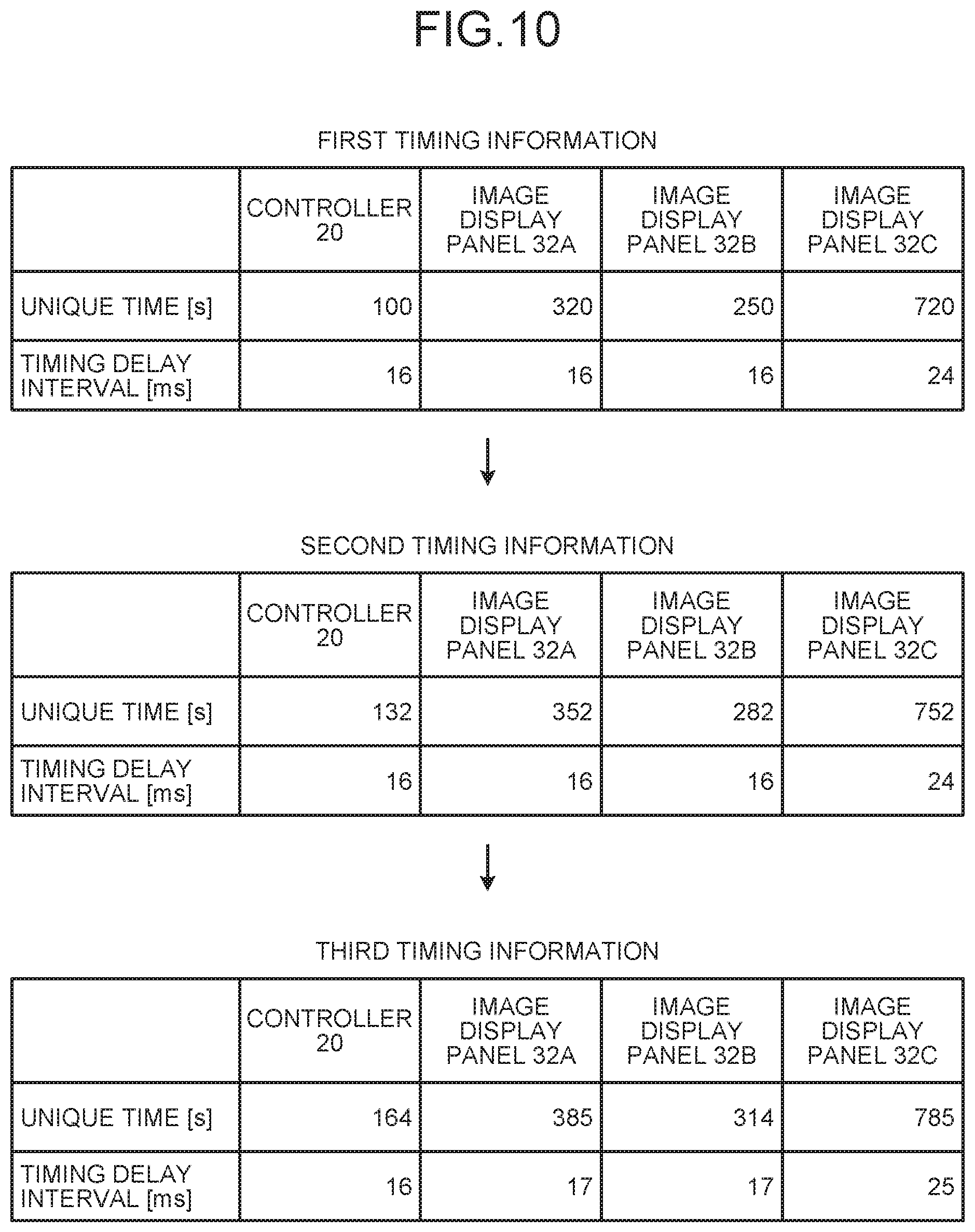

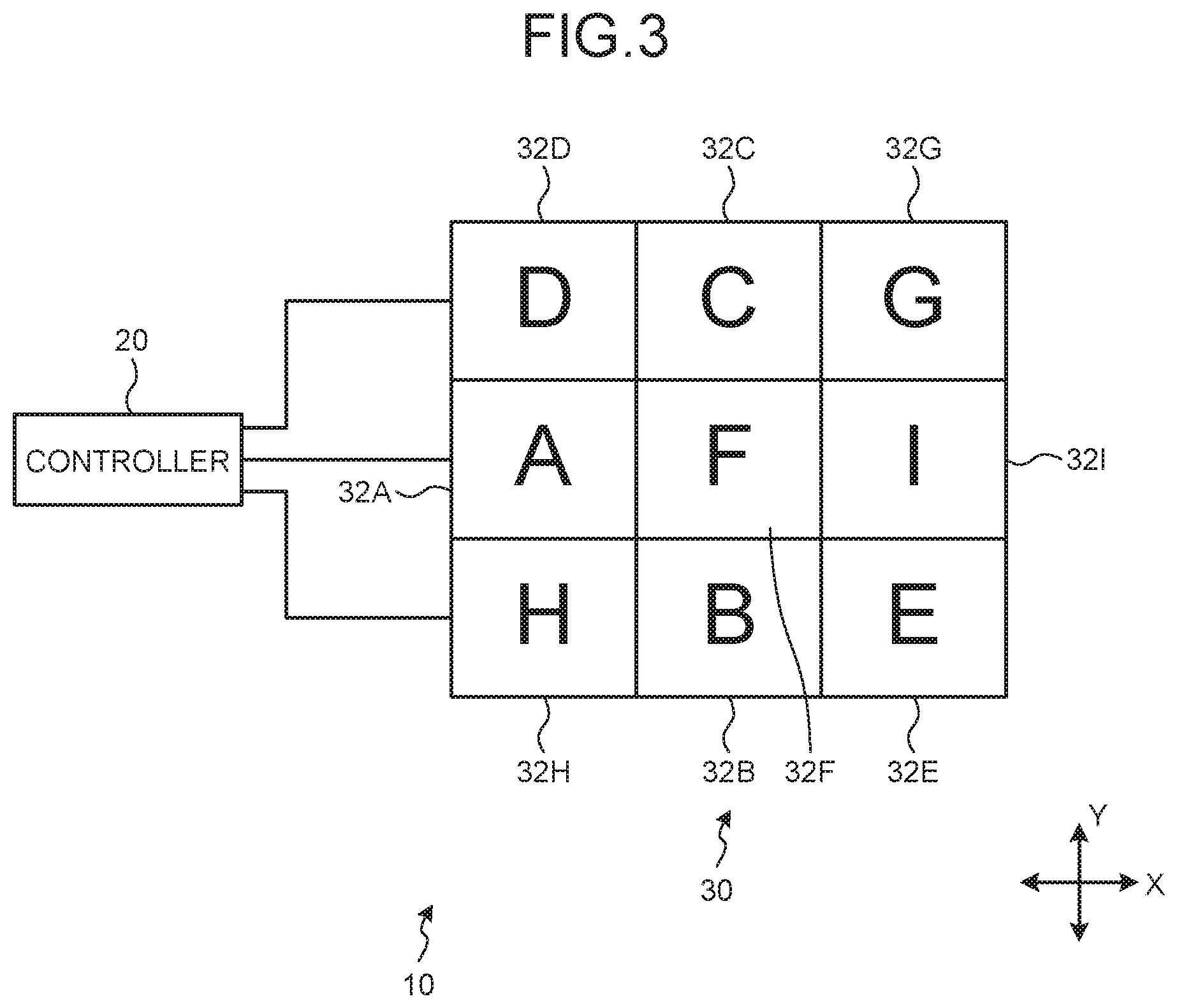

FIG. 3 is a block diagram illustrating a configuration of a display device unit according to a first embodiment;

FIG. 4 is an explanatory diagram for explaining a configuration of an image display panel;

FIG. 5 is a diagram illustrating a layered structure of an image display panel according to the first embodiment;

FIG. 6 is an explanatory diagram for explaining touch detection according to the first embodiment;

FIG. 7 is a block diagram for explaining a configuration of a controller according to the first embodiment;

FIG. 8 is a block diagram for explaining a configuration of a panel controller according to the first embodiment;

FIG. 9 is a flowchart for explaining content of detection processing for an array pattern by the controller;

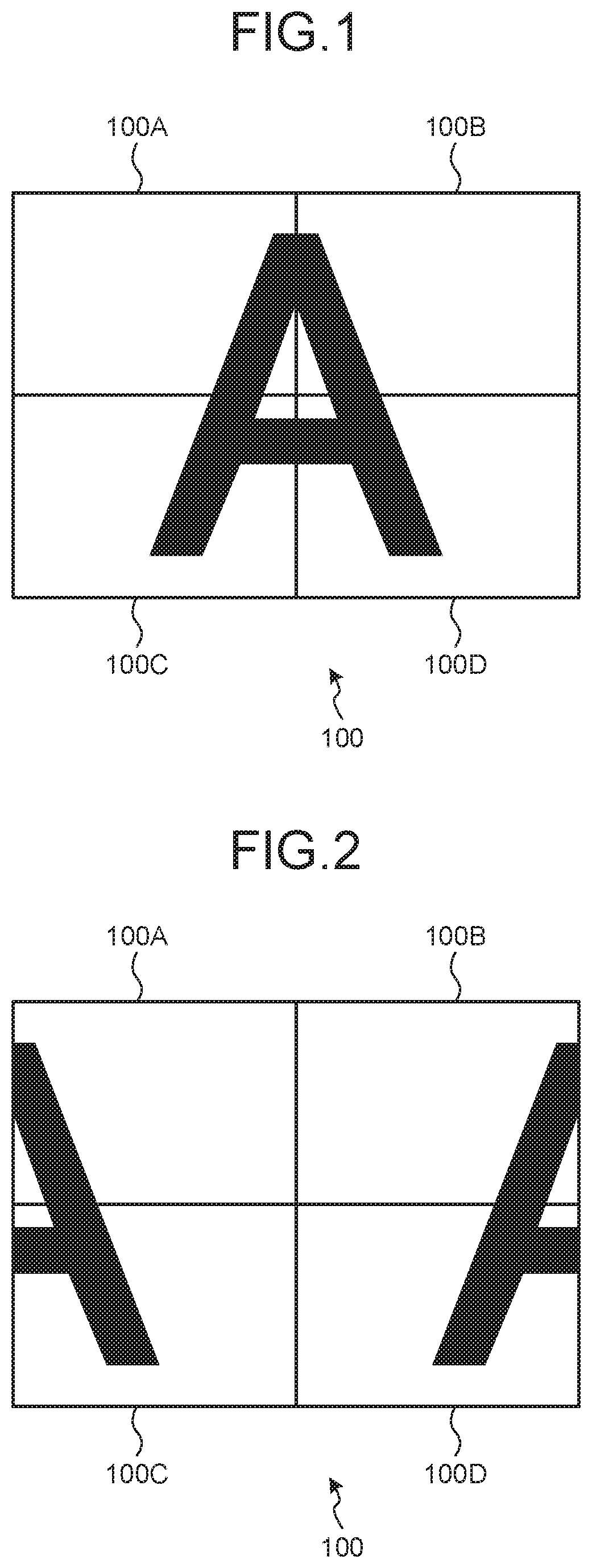

FIG. 10 is a diagram for explaining exemplary timing information;

FIG. 11 is an explanatory diagram for explaining exemplary timing synchronization information;

FIG. 12 is a flowchart for explaining a processing flow of timing synchronization processing;

FIG. 13 is a diagram illustrating an exemplary application voltage and exemplary detection voltages;

FIG. 14 is an explanatory diagram for explaining the generation of the detection voltage when the application voltage is applied;

FIG. 15 is an explanatory diagram for explaining the generation of the detection voltage when the application voltage is applied;

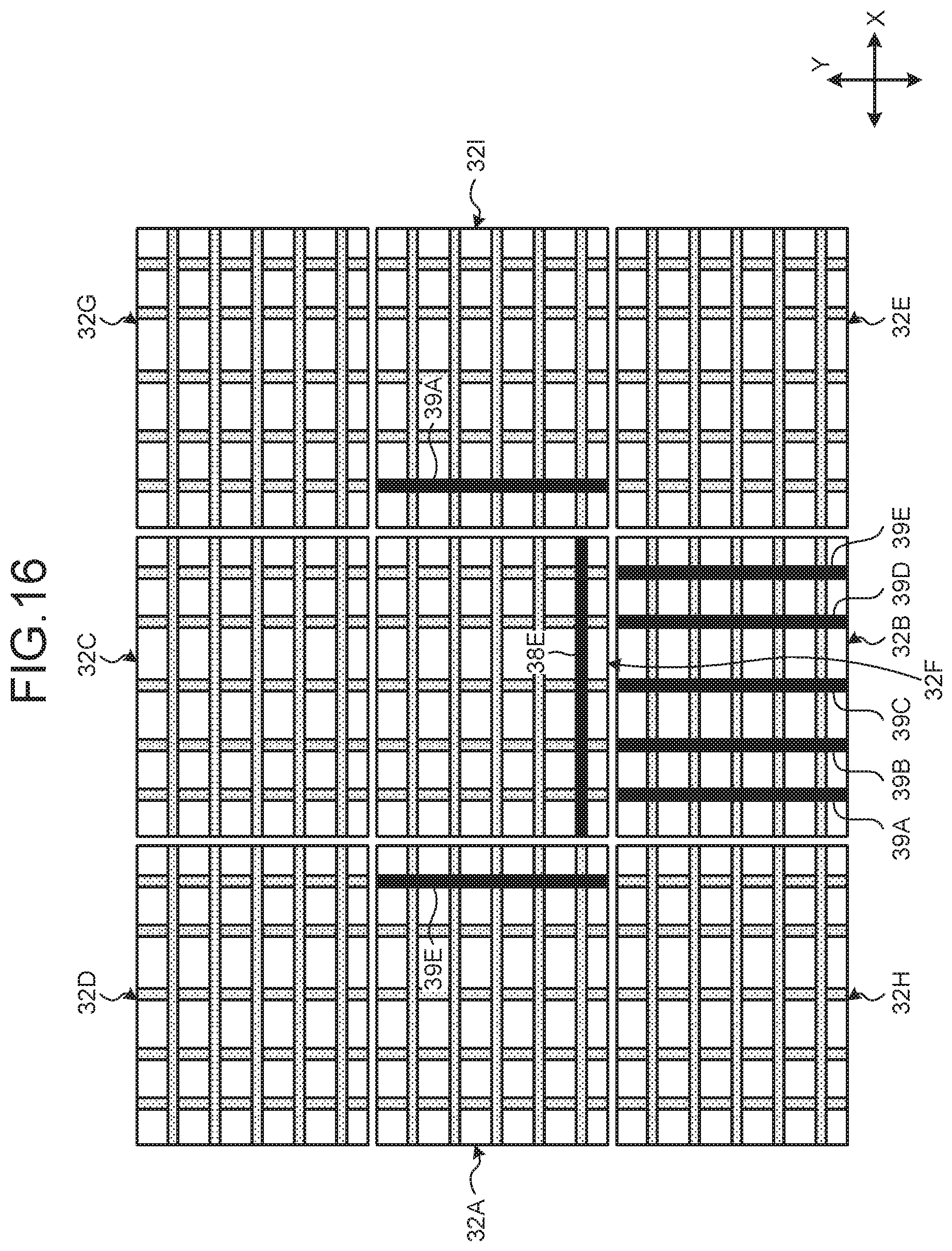

FIG. 16 is an explanatory diagram for explaining the generation of the detection voltage when the application voltage is applied;

FIG. 17 is a flowchart for explaining a processing flow of creation processing for array information;

FIG. 18A is a diagram for explaining exemplary detection processing for misalignment information;

FIG. 18B is a diagram for explaining exemplary detection processing for the misalignment information;

FIG. 18C is a diagram for explaining exemplary detection processing for the misalignment information;

FIG. 18D is a diagram for explaining exemplary detection processing for the misalignment information;

FIG. 19 is a schematic diagram illustrating a configuration of an image display panel unit according to a second embodiment;

FIG. 20 is an explanatory diagram for explaining an exemplary method for creating array information according to the second embodiment;

FIG. 21 is a flowchart illustrating a processing flow of the method for creating the array information according to the second embodiment;

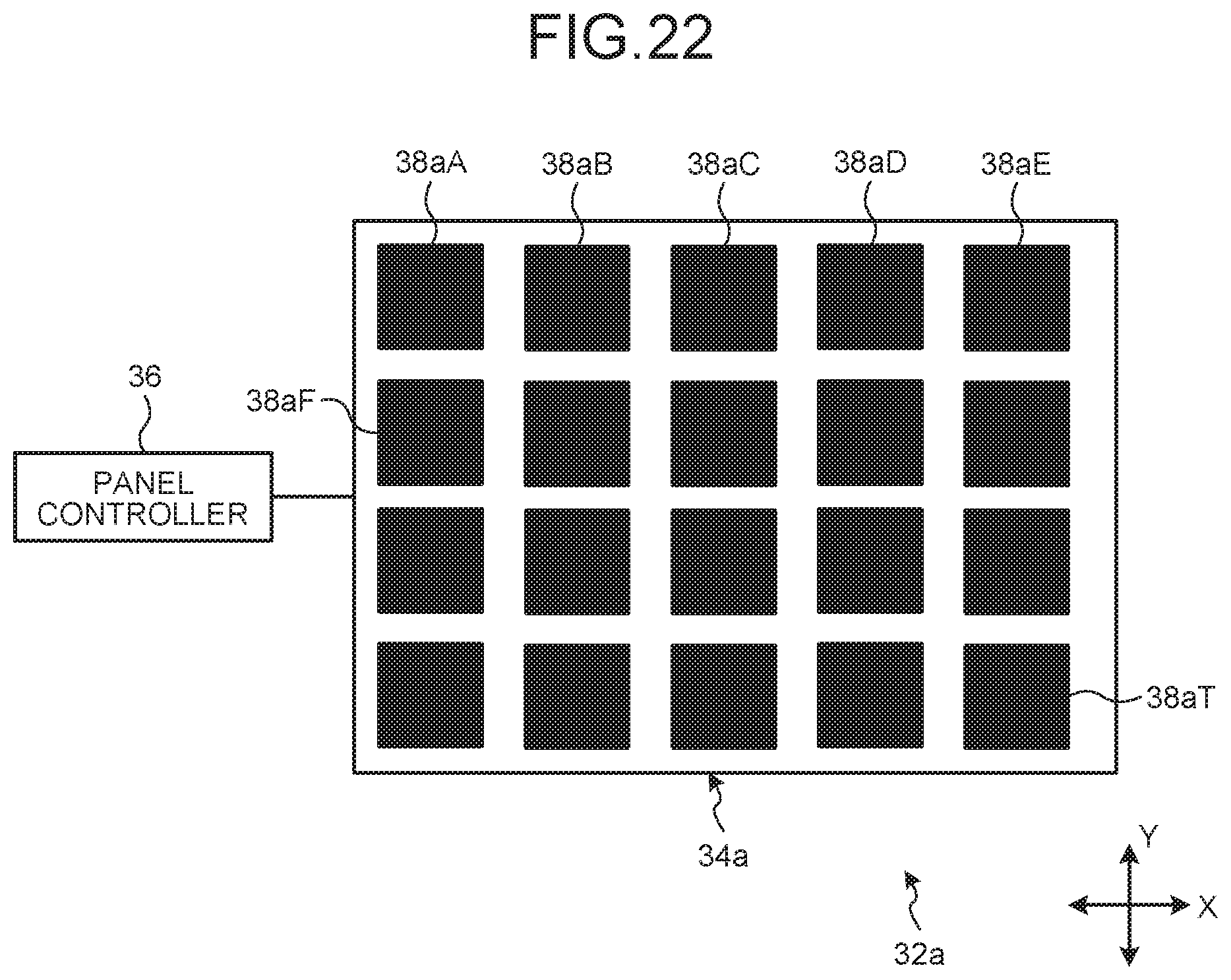

FIG. 22 is an explanatory diagram for explaining a configuration of an image display panel according to a third embodiment;

FIG. 23A is a schematic circuit diagram of a drive detection electrode unit according to the third embodiment;

FIG. 23B is an explanatory diagram for explaining touch detection according to the third embodiment;

FIG. 24 is an explanatory diagram for explaining the generation of the detection voltage according to the third embodiment;

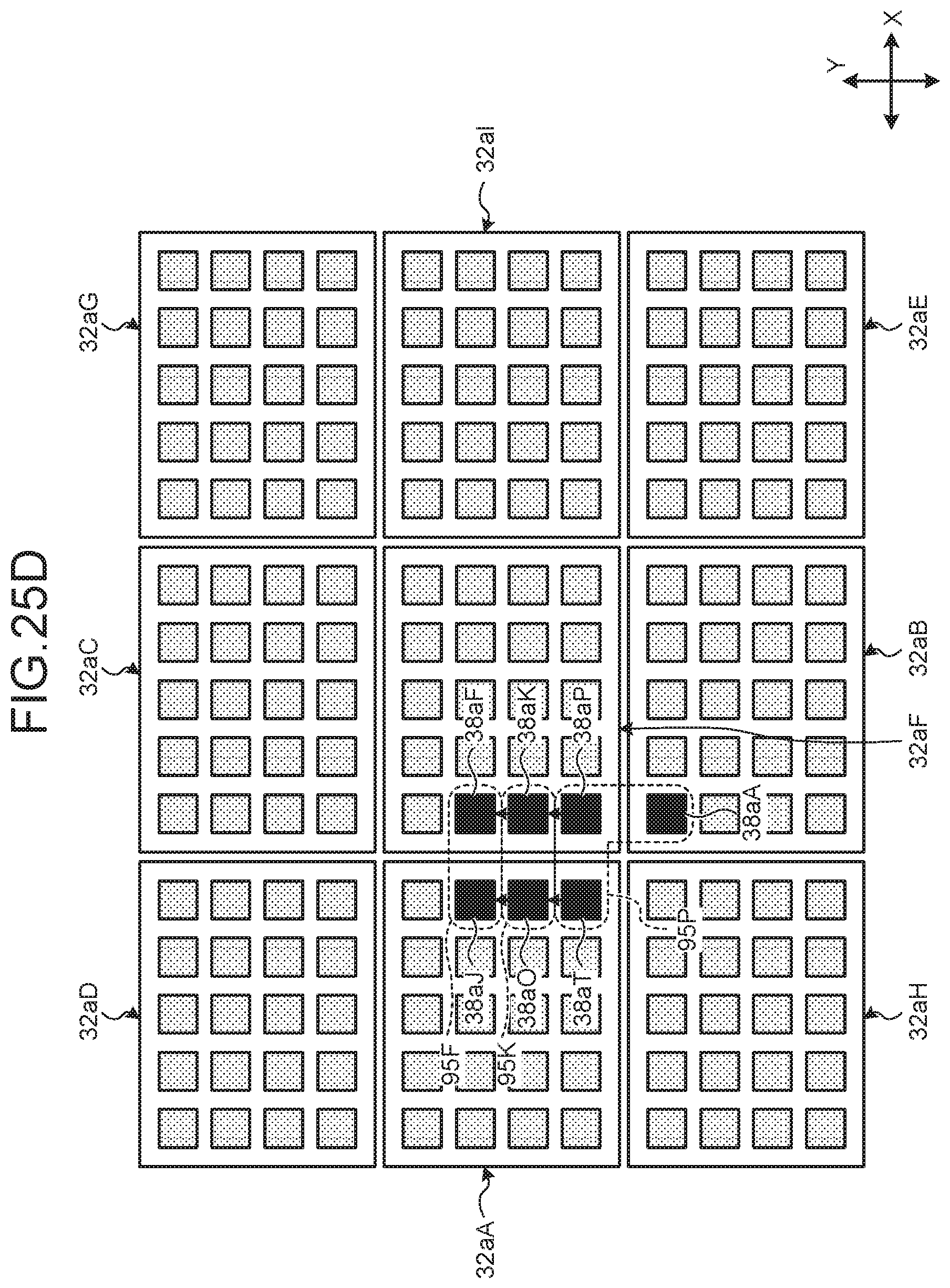

FIG. 25A is an explanatory diagram for explaining the generation of the detection voltage when the application voltage is applied in the third embodiment;

FIG. 25B is an explanatory diagram for explaining the generation of the detection voltage when the application voltage is applied in the third embodiment;

FIG. 25C is an explanatory diagram for explaining the generation of the detection voltage when the application voltage is applied in the third embodiment;

FIG. 25D is an explanatory diagram for explaining the generation of the detection voltage when the application voltage is applied in the third embodiment;

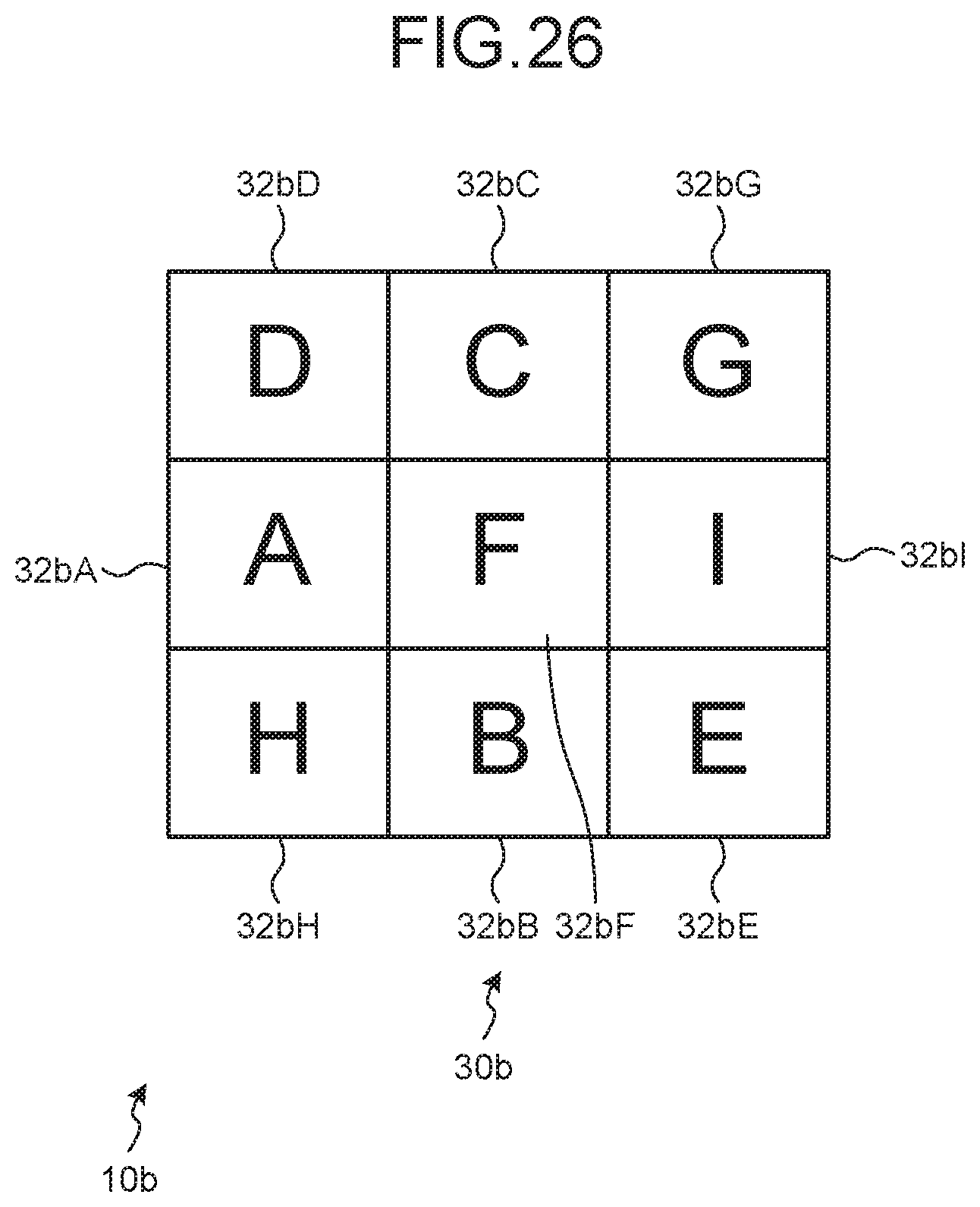

FIG. 26 is a block diagram illustrating a configuration of a display device unit according to a fourth embodiment;

FIG. 27A is a block diagram illustrating a configuration of a panel controller according to the fourth embodiment;

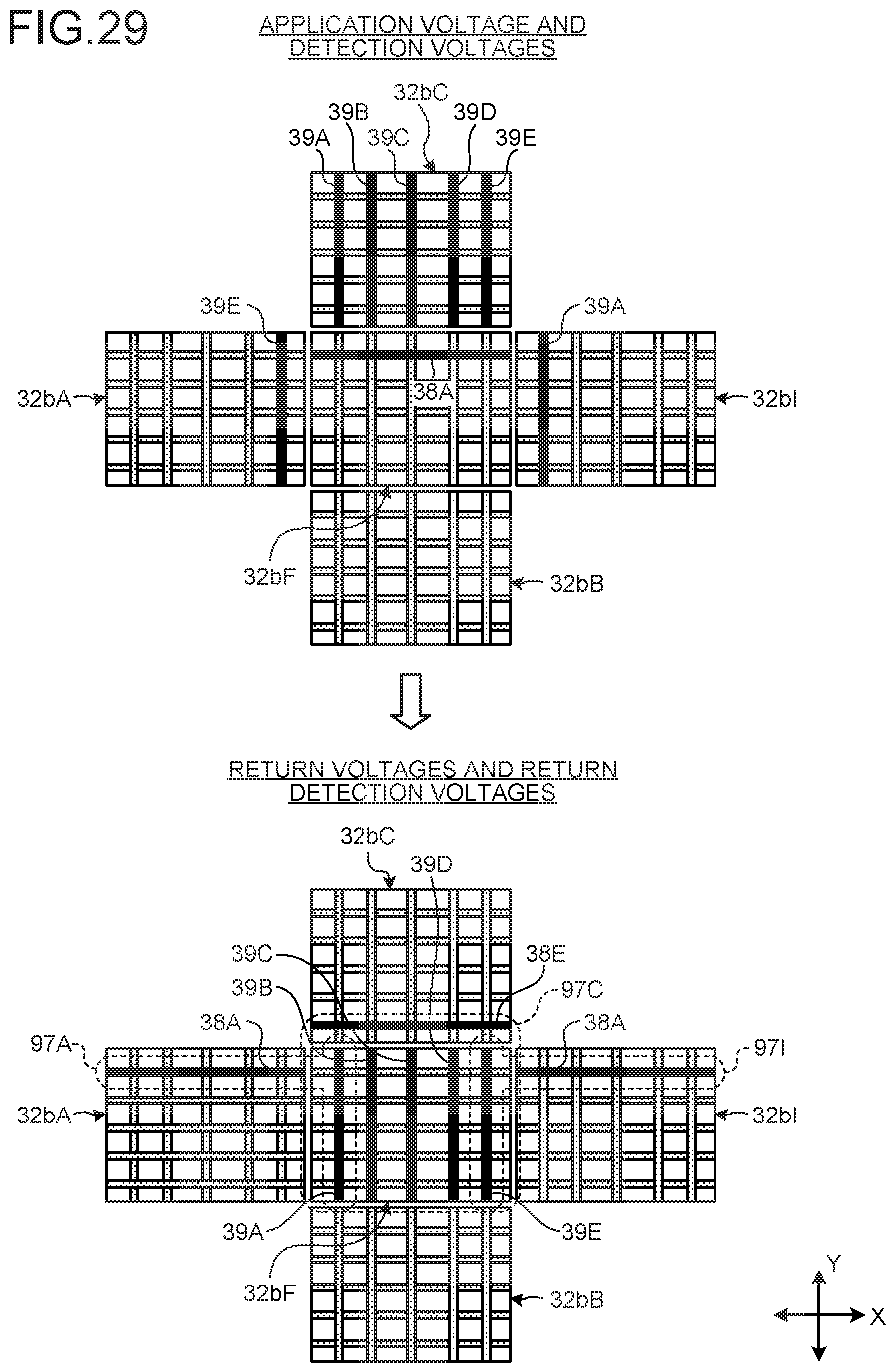

FIG. 27B is a block diagram illustrating a configuration of a controller according to the fourth embodiment;

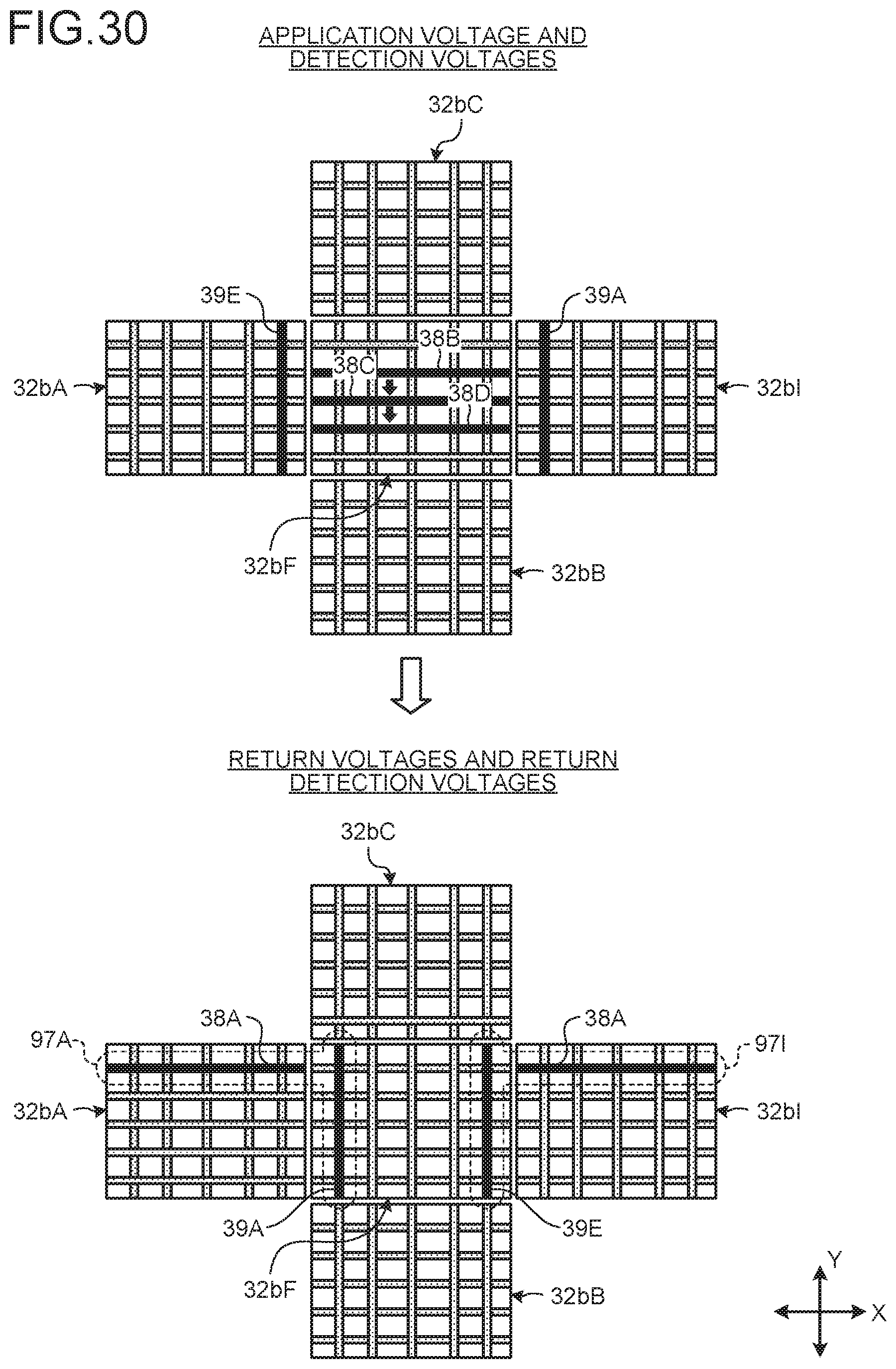

FIG. 28 is an explanatory diagram for explaining a return detection voltage;

FIG. 29 is an explanatory diagram for explaining the application of the application voltage and the generation of the return detection voltage;

FIG. 30 is an explanatory diagram for explaining the application of the application voltage and the generation of the return detection voltage; and

FIG. 31 is an explanatory diagram for explaining the application of the application voltage and the generation of the return detection voltage.

DETAILED DESCRIPTION

Hereinafter, embodiments according to the invention will be described with reference to the drawings. The disclosure simply gives examples. Accordingly, appropriate modifications in accordance with the spirit of the invention are of course included within the scope of the invention as long as those skilled in the art can easily conceive such modifications. For clearer description, the drawings in some cases express widths, thicknesses, shapes, and the like of respective units more schematically than those in the actual modes. Merely serving as examples, the drawings are not construed to limit the interpretation of the invention. In the present specification and the respective drawings, components similar to those described earlier in relation with the drawings that have been already mentioned are denoted by the same reference numerals and detailed description thereof is omitted in some cases as necessary.

(First Embodiment)

First, a first embodiment will be described. A display device unit 10 according to the first embodiment includes an image display panel unit 30 in which a plurality of image display panels is arrayed in a flat surface shape. The display device unit 10 includes the plurality of image display panels 32 in such a manner that display surfaces of the plurality of image display panels 32 are orderly arranged on a flat surface, whereby the display device unit 10 is configured to display an image using the plurality of display surfaces as a single screen. That is, the display device unit 10 is a so-called tiling display.

Hereinafter, an example of a typical tiling display will be described with reference to FIG. 1 and FIG. 2. FIG. 1 and FIG. 2 are explanatory diagrams for explaining the tiling display. Each of FIG. 1 and FIG. 2 illustrates a tiling display 100 in which display surfaces (surfaces on which images are displayed) of image display panels 100A, 100B, 100C, and 100D are arrayed on a flat surface. The image display panel 100A is arranged at the upper left, the image display panel 100B is arranged at the upper right, the image display panel 100C is arranged at the lower left, and the image display panel 100D is arranged at the lower right.

The tiling display 100 displays an image using the respective display surfaces of the image display panels 100A, 100B, 100C, and 100D as a single screen. A case is considered where the tiling display 100 is caused to display a single image of an alphabetical letter "A" as illustrated in FIG. 1. In the case, the tiling display 100 causes the image display panel 100A to display a partial image corresponding to an upper left part of "A". The tiling display 100 causes the image display panel 100B to display a partial image corresponding to an upper right part of "A". The tiling display 100 causes the image display panel 100C to display a partial image corresponding to a lower left part of "A". The tiling display 100 causes the image display panel 100D to display a partial image corresponding to a lower right part of "A".

Meanwhile, when the tiling display 100 cannot recognize an array pattern for each of the image display panels, there is a risk that the tiling display 100 cannot transmit an image signal corresponding to a position at which each of the image display panel is arranged. Accordingly, there is a risk where each of the image display panels cannot display a partial image corresponding to a position at which that image display panel is arranged. In such a case, as illustrated in FIG. 2 as an example, the tiling display 100 can cause the image display panel 100A to display the partial image corresponding to the upper right part of "A". The tiling display 100 can cause the image display panel 100B to display the partial image corresponding to the upper left part of "A". The tiling display 100 can cause the image display panel 100C to display the partial image corresponding to the lower right part of "A". The tiling display 100 can cause the image display panel 100D to display the partial image corresponding to the lower left part of "A".

As described above, the tiling display needs to recognize information regarding at which position each of the image display panels is arranged among all of the image display panels (array pattern) to transmit, to each of the image display panels, an image signal of a partial image corresponding to the position of that image display panel. The display device unit 10 according to the first embodiment is capable of detecting the array pattern for each of the image display panels 32.

(Overall Configuration of Display Device Unit)

FIG. 3 is a block diagram illustrating a configuration of the display device unit according to the first embodiment. As illustrated in FIG. 3, the display device unit 10 includes a controller 20 and the image display panel unit 30. The image display panel unit 30 includes image display panels 32A, 32B, 32C, 32D, 32E, 32F, 32G, 32H, and 32I. Hereinafter, the image display panels 32A, 32B, 32C, 32D, 32E, 32F, 32G, 32H, and 32I are noted as the image display panels 32 when these image display panels are not distinguished from one another. The controller 20 is connected to all of the image display panels 32 and configured to control driving of the respective image display panels 32. Detailed description thereof will be given later.

(Configuration of Image Display Panel Unit)

In the image display panel unit 30, the display surfaces of the plurality of image display panels 32 are orderly arranged on a flat surface, whereby the image display panel unit 30 displays an image using the plurality of display surfaces as a single screen. As illustrated in FIG. 3, the image display panels 32 are arrayed in a two-dimensional matrix form in an X direction and a Y direction in the image display panel unit 30. The X direction represents a row direction, serving as a column direction perpendicularly intersecting with the Y direction. However, the X direction and the Y direction are not limited thereto. In the image display panel unit 30, the plurality of image display panels 32 is arrayed in three rows and three columns, specifically, three columns along the X direction and three rows along the Y direction. In the first embodiment, the image display panel 32A is arranged at second row and first column. The image display panel 32B is arranged at third row and second column. The image display panel 32C is arranged at first row and second column. The image display panel 32D is arranged at first row and first column. The image display panel 32E is arranged at third row and third column. The image display panel 32F is arranged at second row and second column. The image display panel 32G is arranged at first row and third column. The image display panel 32H is arranged at third row and first column. The image display panel 32I is arranged at second row and third column. However, the number of the image display panels 32 is arbitrary in the image display panel unit 30 as long as the plurality of image display panels 32 is arrayed in a flat surface shape. The image display panel unit 30 is not limited to an array such as one illustrated in FIG. 3 as long as the plurality of image display panels 32 are arrayed in a flat surface shape. For example, the plurality of image display panels 32 may be arrayed in one column, or alternatively, arrayed in a step shape.

(Configuration of Image Display Panel)

Next, a configuration of the image display panel 32 will be described. FIG. 4 is an explanatory diagram for explaining the configuration of the image display panel. The image display panel 32 is an image display panel with a touch detection function (so-called touch panel). As illustrated in FIG. 4, the image display panel 32 includes a panel unit 34 and a panel controller 36. The panel unit 34 includes a display surface on which an image is displayed and also detects an object in the proximity to the display surface. The panel controller 36 controls operation of the panel unit 34.

As illustrated in FIG. 4, the panel unit 34 includes drive electrode units 38A, 38B, 38C, 38D, and 38E and detection electrode units 39A, 39B, 39C, 39D, and 39E. The drive electrode units 38A, 38B, 38C, 38D, and 38E, each of which is disposed extending along the Y direction, are electrodes arranged in the X direction in this order. The detection electrode units 39A, 39B, 39C, 39D, and 39E are electrodes provided so as to oppose the drive electrode units 38A, 38B, 38C, 38D, and 38E. The detection electrode units 39A, 39B, 39C, 39D, and 39E, each of which is disposed extending along the X direction, are arranged in the Y direction in this order. Hereinafter, the drive electrode units 38A, 38B, 38C, 38D, and 38E are noted as drive electrode units 38 when these drive electrode units are not distinguished from one another. Likewise, the detection electrode units 39A, 39B, 39C, 39D, and 39E are noted as detection electrode units 39 when these detection electrode units are not distinguished from one another. Shapes, array orders, and the numbers of the drive electrode units 38 and the detection electrode units 39 are not limited to the example in FIG. 4.

An application voltage V.sub.A is applied to the drive electrode units 38 at respective timings when the array pattern among the plurality of image display panels 32 is confirmed. A detection voltage V.sub.D is generated at the detection electrode unit 39 depending on the application voltage V.sub.A at the drive electrode unit 38 in another image display panel 32 (the image display panel other than the image display panel 32 of its own). The drive electrode unit 38 also has a function as a drive electrode in the touch detection that detects a proximity object. Similarly, the detection electrode unit 39 also has a function as an electrode for detecting a touch in the touch detection.

FIG. 5 is a diagram illustrating a layered structure of the image display panel according to the first embodiment. As illustrated in FIG. 5, the panel unit 34 includes a pixel substrate 40A, a counter substrate 40B arranged facing the pixel substrate 40A, and a liquid crystal layer 43 provided between the pixel substrate 40A and the counter substrate 40B. The pixel substrate 40A includes a TFT substrate 41 serving as a circuit substrate and a plurality of pixel electrodes 42 disposed at respective positions in a two-dimensional matrix form on this TFT substrate 41. Wiring (not illustrated) is formed on the TFT substrate 41, including a thin film transistor (TFT) for each of pixels, a pixel signal line SGL that supplies the image signal to the pixel electrode 42, and a scanning signal line GCL that drives each of the TFTs.

The counter substrate 40B includes a glass substrate 44, a color filter 45 formed on one surface of this glass substrate 44, and the plurality of the drive electrode units 38 formed on this color filter 45. The color filter 45 is configured by color filter layers of three colors of, for example, red (R), green (G), and blue (B) cyclically arrayed, where the three colors of R, G, and B are associated with each of display pixels as one set. The drive electrode unit 38 has functions as a common drive electrode when displaying an image, a drive electrode in carrying out the touch detection, and a drive electrode during the confirmation of the array pattern of the image display panels 32. The drive electrode unit 38 is made of, for example, indium tin oxide (ITO). The drive electrode unit 38 is coupled to the TFT substrate 41 using a contact conducting cylinder (not illustrated) such that a voltage such as the application voltage V.sub.A is applied thereto from the TFT substrate 41 through this contact conducting cylinder.

The plurality of detection electrode units 39 is formed on another surface of the glass substrate 44. The detection electrode unit 39 has functions as a detection electrode in carrying out the touch detection and a detection electrode during the confirmation of the array pattern of the image display panels 32. As in the drive electrode unit 38, the detection electrode unit 39 is made of ITO, for example. Additionally, a polarizing plate 46 is disposed on these detection electrode units 39.

The liquid crystal layer 43 is configured to modulate light passing through an electric field depending on a state of the electric field, where liquid crystals in various types of modes are used, including a twisted nematic (TN) mode, a vertical orientation (VA) mode, and an electrically controlled birefringence (ECB) mode. Orientation films are individually disposed between the liquid crystal layer 43 and the pixel substrate 40A and between the liquid crystal layer 43 and the counter substrate 40B, while an incident-side polarizing plate is arranged on a lower surface side of the pixel substrate 40A, but the illustration thereof is omitted on the drawing.

As described above, the drive electrode unit 38 has functions as a drive electrode in carrying out the touch detection and a drive electrode during the confirmation of the array pattern of the image display panels 32. Likewise, the detection electrode unit 39 has functions as a detection electrode in carrying out the touch detection and a detection electrode during the confirmation of the array pattern of the image display panels 32. However, the configuration of the image display panel 32 is not limited to the one described above. The confirmation of the array pattern of the image display panels 32 will be described later and hereinafter, the touch detection is described.

FIG. 6 is an explanatory diagram for explaining the touch detection according to the first embodiment. As illustrated in FIG. 4 and FIG. 5, the drive electrode unit 38 and the detection electrode unit 39 according to the embodiment are separate electrodes provided so as to face each other. The image display panel 32 according to the embodiment is a capacitance type touch panel, in more detail, a mutual capacitance sensing-type touch panel in which the drive electrode unit 38 and the detection electrode unit 39 form a capacitance. Specifically, as illustrate in a graph (A) of FIG. 6, a touch drive signal is applied to the drive electrode unit 38 when the touch detection is carried out. The touch drive signal is an alternating current signal at a predetermined frequency, whose maximum voltage serves as a touch drive voltage V.sub.T0. When the touch drive signal is applied thereto, the detection electrode unit 39 facing thereto generates a touch detection signal corresponding to the touch drive signal. While the proximity object such as a finger 110 is not in the proximity to or in touch with the image display panel 32 or the like, the maximum voltage of the touch detection signal is a touch detection voltage V.sub.T1 corresponding to the touch drive voltage V.sub.T0.

On the other hand, while the proximity object such as the finger 110 is in the proximity to or in touch with the image display panel 32, the proximity object and the detection electrode unit 39 form a capacitive component, in addition to a capacitive component formed by the drive electrode unit 38 and the detection electrode unit 39. This capacitive component formed by the drive electrode unit 38 and the detection electrode unit 39 and this capacitive component formed by the proximity object and the detection electrode unit 39 are in serial in an equivalent circuit. Accordingly, in a case where the proximity object is in the proximity to the image display panel 32, the maximum voltage of the touch detection signal is a touch detection voltage V.sub.T2 whose value is smaller than that of the touch detection voltage V.sub.T1. The embodiment determines that the proximity object such as the finger 110 is in the proximity to or in touch with the image display panel 32 when the maximum voltage of the touch detection signal is smaller than a touch voltage threshold V.sub.T3 serving as a predetermined threshold. The image display panel 32 carries out the touch detection in this manner.

(Configuration of Controller)

Next, a configuration of the controller 20 will be described. The controller 20 constitutes a control device that controls the image display panel 32. FIG. 7 is a block diagram for explaining the configuration of the controller according to the first embodiment. The controller 20 includes a timing synchronization unit 50, an image display controller 52, and an array information unit 54. The timing synchronization unit 50 generates timing synchronization information for synchronizing operation timings between the controller 20 and the image display panel 32. The image display controller 52 is configured to control image display of the respective image display panels 32. The array information unit 54 is configured to generates array information serving as information regarding at which position each of the image display panels 32 is arranged among all of the image display panels 32 (array pattern).

The timing synchronization unit 50 includes an RTC unit 60, a timing signal unit 62, and a timing synchronization information creation unit 64. The RTC unit 60 acts as a real time clock (RTC) for the controller 20 to clock time unique to the controller 20. Although the RTC unit 60 has accuracy of a one-second order, the accuracy of time clocking is arbitrary and a high-accuracy RTC unit having accuracy of a more accurate millisecond order may be employed.

The timing signal unit 62 is configured to output a timing signal to each of the image display panels 32. The timing signal according to the embodiment is a ping.

The timing synchronization information creation unit 64 creates the timing synchronization information based on the timing signal, a return timing signal which is a return signal to the timing signal, and unique time of the controller 20 and unique time of the image display panel 32. The timing synchronization information is information regarding a delay interval until a command issued from the controller 20 reaches each of the image display panels 32. Details of generation processing for the timing synchronization information will be described later.

Based on the timing synchronization information from the timing synchronization unit 50, the array information from the array information unit 54, and the like, the image display controller 52 transmits, to each of the image display panels 32, the image signal for causing each of the image display panels 32 to display a predetermined image.

The array information unit 54 includes an application voltage output instruction unit 70, a detection voltage information creation unit 72, an adjacent information creation unit 74, an array information creation unit 76, and a misalignment information creation unit 78.

The application voltage output instruction unit 70 instructs the image display panel 32 to apply the application voltage V.sub.A to the drive electrode unit 38 of the image display panel 32.

The detection voltage information creation unit 72 acquires the detection voltage V.sub.D generated at another image display panel 32 (the image display panel other than the image display panel 32 of its own) in accordance with the application voltage V.sub.A to create detection voltage information A1. The detection voltage information A1 will be described later.

Based on the detection voltage information A1, the adjacent information creation unit 74 creates adjacent information B serving as information indicating the image display panels 32 adjacent to each other. The adjacent information B will be described later.

Based on the adjacent information B, the array information creation unit 76 creates array information C indicating the array pattern among the plurality of image display panels 32. The array information C will be described later.

Based on the detection voltage information A1, the misalignment information creation unit 78 creates misalignment information D serving as information regarding misalignment among the adjacent image display panels 32. The misalignment information D will be described later.

The controller 20 has the configuration described above.

(Configuration of Panel Controller)

Next, a configuration of the panel controller 36 will be described. FIG. 8 is a block diagram for explaining the configuration of the panel controller according to the first embodiment. As illustrated in FIG. 8, the panel controller 36 includes a panel timing unit 80, a panel display controller 82, a touch controller 83, and an electrode controller 84. The panel timing unit 80 receives the timing signal from the timing synchronization unit 50 of the controller 20 to output the return timing signal. Based on the image signal from the image display controller 52 of the controller 20, the panel display controller 82 causes the panel unit 34 to display an image. The touch controller 83 controls the touch detection on the panel unit 34. The electrode controller 84 applies the application voltage V.sub.A based on the instruction from the application voltage output instruction unit 70 of the controller 20 and outputs the detection voltage V.sub.D to the detection voltage information creation unit 72 of the controller 20.

The panel timing unit 80 includes a panel RTC unit 90 and a panel timing signal unit 92. The panel RTC unit 90 acts as an RTC for the image display panel 32 to clock time unique to the image display panel 32 of its own. Although the panel RTC unit 90 has accuracy of a one-second order, the accuracy of time clocking is arbitrary and a high-accuracy RTC unit having accuracy of a more accurate millisecond order may be employed.

The panel timing signal unit 92 receives the timing signal from the timing signal unit 62 to output the return timing signal to the timing signal unit 62.

The electrode controller 84 includes an application voltage output unit 94 and a detection voltage transmission unit 96. Based on the instruction from the application voltage output instruction unit 70 of the controller 20, the application voltage output unit 94 applies the application voltage V.sub.A to the drive electrode unit 38 of its own. The detection voltage transmission unit 96 transmits, to the detection voltage information creation unit 72 of the controller 20, the detection voltage V.sub.D generated at the detection electrode unit 39 in its own image display panel 32.

The panel controller 36 has the configuration as described above.

(Processing Content)

Next, the content of the processing by the controller 20 for detecting the array pattern of the image display panels 32 will be described. FIG. 9 is a flowchart for explaining the content of the detection processing for the array pattern by the controller. As illustrated in FIG. 9, the controller 20 first carries out timing synchronization processing (step S10) to create the timing synchronization information used for detecting the array pattern. After carrying out the timing synchronization processing, the controller 20 carries out creation processing for the array information indicating the array pattern of the image display panels 32 (step S12). After carrying out the creation processing for the array information, the controller 20 creates the misalignment information serving as information regarding misalignment among the adjacent image display panels 32 (step S14). With this, the processing for detecting the array pattern of the image display panels 32 is completed. Based on a result of this processing, the controller 20 transmits, to each of the image display panels 32, the image signal corresponding to a position at which that image display panel 32 is arranged. The image display panel 32 displays an image corresponding to a position at which that image display panel 32 is arranged based on this proper pixel signal. Hereinafter, details of the processing at respective steps S10, S12, and S14 will be described.

(Timing Synchronization Processing)

First, the timing synchronization processing at step S10 in FIG. 9 will be described. The timing synchronization processing is processing that detects in advance a delay interval until a command issued from the controller 20 reaches each of the image display panels 32. The controller 20 carries out control in consideration of this delay interval during the detection of the array pattern of the image display panels 32 such that the operation among the respective image display panels 32 can be synchronized. As a result, the array pattern can be properly detected.

In the timing synchronization unit 50 of the controller 20, the timing signal unit 62 outputs the timing signals to all of the image display panels 32. The timing synchronization unit 50 also outputs the timing signal to the controller 20 itself.

Upon acquiring the timing signal, in the image display panel 32, the panel timing signal unit 92 generates the return timing signal, namely, the return signal to the timing signal and then outputs the generated return timing signal to the timing synchronization information creation unit 64 of the controller 20. The panel timing signal unit 92 also acquires, from the panel RTC unit 90, unique time information serving as information regarding the unique time at the point of outputting the return timing signal. The panel timing signal unit 92 outputs the unique time information to the timing synchronization information creation unit 64 of the controller 20. Likewise, when the timing synchronization unit 50 of the controller 20 acquires the timing signal to itself, the timing synchronization unit 50 generates the return timing signal to output to the timing synchronization information creation unit 64. The timing synchronization unit 50 also acquires, from the RTC unit 60, unique time information serving as information regarding the unique time at the point of outputting the return timing signal. The timing synchronization unit 50 outputs the unique time information to the timing synchronization information creation unit 64.

The timing synchronization information creation unit 64 detects a timing delay interval based on the unique time of the controller 20 at the point of outputting the timing signal and the unique time of the controller 20 at the point of acquiring the return timing signal. Because the return timing signal is output from each of the image display panels 32, the timing delay interval is detected for each of the image display panels 32. The timing delay interval represents a difference between the time at the point of outputting the timing signal and the time at the point of acquiring the return timing signal. The timing delay interval corresponds to a delay interval until a command issued from the controller 20 reaches each of the image display panels 32. Because the return timing signal is also output from the controller 20 itself, the timing delay interval is also detected for the controller 20 itself. The timing delay interval for the controller 20 itself represents a delay interval within the controller 20 in controlling. The timing synchronization information creation unit 64 acquires the unique time information of the respective image display panels 32 at the point of outputting the return timing signal and the unique time information of the controller 20 at the point of outputting the return timing signal.

The timing synchronization information creation unit 64 stores, as timing information, the timing signal delay intervals for the respective image display panels 32 and the controller 20, and the unique time information of the respective image display panels 32 and the controller 20. The timing synchronization unit 50 of the controller 20 repeats this creation processing for the timing information a plurality of times to create a plurality of sets of the timing information.

FIG. 10 is a diagram for explaining exemplary timing information. FIG. 10 illustrates first timing information indicating an initial timing, second timing information serving as the subsequent timing information, and third timing information serving as the further subsequent timing information. According to the first timing information in FIG. 10, the unique time of the controller 20 at the point of outputting the return timing signal is 100 (s). Similarly, the unique time of the image display panel 32A is 320 (s), the unique time of the image display panel 32B is 250 (s), and the unique time of the image display panel 32C is 720 (s). This information indicates the time of the respective units at the same timing, representing that, for example, when the controller 20 is at the time of 100 (s), the image display panel 32A is at the time of 320 (s).

According to the first timing information in FIG. 10, the timing delay interval for the controller 20 itself is 16 (ms). The timing delay interval for the image display panel 32A is 16 (ms), the timing delay interval for the image display panel 32B is 16 (ms), and the timing delay interval for the image display panel 32C is 24 (ms). This information indicates that, for example, the delay interval when the controller 20 issues a command to itself is 16 (ms), while the delay interval when the controller 20 issues a command to the image display panel 32A is also 16 (ms).

As illustrated in FIG. 10, the timing synchronization information creation unit 64 acquires the above-described first timing information, along with the second timing information and the third timing information serving as the subsequent timing information. For example, the second timing information represents processing carried out 32 seconds after the first timing information. Accordingly, the unique time of the controller 20 in the second timing information is 132 (s). Although FIG. 10 simply illustrates information regarding the image display panels 32A, 32B, and 32C out of the image display panels 32, the actual timing information contains information regarding all of the image display panels 32.

Based on the plurality of sets of timing information created as described above, the timing synchronization information creation unit 64 creates the timing synchronization information. The timing synchronization information contains time synchronization information and delay interval information. The time synchronization information is served as information regarding a corresponding relationship between the unique time of the controller 20 and the unique time of each of the image display panels 32. The delay interval information is an interval until a command issued from the controller 20 reaches each of the image display panels 32. The timing synchronization information creation unit 64 creates the time synchronization information based on a difference between the unique time of the controller 20 and the unique time of each of the image display panels 32. The timing synchronization information creation unit 64 also creates the delay interval information based on information regarding the delay interval for each of the image display panels 32. The timing synchronization information creation unit 64 may create the timing synchronization information based on at least one set of the timing information.

FIG. 11 is an explanatory diagram for explaining exemplary timing synchronization information. FIG. 11 illustrates timing synchronization information created based on the first timing information, the second timing information, and the third timing information in FIG. 10. According to FIG. 11, the time synchronization information indicates that the unique time of the image display panel 32A is 220 (s) ahead of the unique time of the controller 20. Likewise, the unique time of the image display panel 32B is 150 (s) ahead of the unique time of the controller 20, whereas the unique time of the image display panel 32C is 620 (s) ahead of the unique time of the controller 20. This time synchronization information represents a value of a difference between the unique time of the controller 20 and the unique time of each of the image display panels 32 in each set of the timing information.

According to FIG. 11, the delay interval information indicates that the delay interval for the image display panel 32A, that is, an interval until a command from the controller 20 reaches the image display panel 32A (an interval for one direction) is 8.16 (ms). This delay interval information represents a value obtained by dividing an average value of the timing delay intervals for the image display panel 32A in the first timing information, the second timing information, and the third timing information by two. Likewise, the delay interval for the image display panel 32B is 8.16 (ms), whereas the delay interval for the image display panel 32C is 12.16 (ms). However, the delay interval information may be a value obtained by dividing a maximum value of the timing delay intervals for the image display panel 32A in the first timing information, the second timing information, and the third timing information by two.

The timing synchronization information creation unit 64 creates the timing synchronization information as described above. Based on this timing synchronization information, the controller 20 controls, for example, creation of array pattern information later. For example, based on the time synchronization information, the controller 20 can control each of the image display panels 32 by specifying the unique time thereof. When causing the image display panel 32 to carry out processing at predetermined unique time, the controller 20 outputs a command earlier than that unique time at least by an amount equivalent to the delay interval, thereby making it possible to cause the image display panel 32 to carry out the processing without being late for that predetermined unique time.

A processing flow of the above-described timing synchronization processing will be described with reference to a flowchart. FIG. 12 is a flowchart for explaining a processing flow of the timing synchronization processing. First, as illustrated in FIG. 12, the controller 20 uses the timing signal unit 62 to output the timing signals to the controller 20 and the respective image display panels 32 (step S20). After outputting the timing signals, the controller 20 uses the timing synchronization information creation unit 64 to acquire the return timing signals and the unique time information from the controller 20 and the respective image display panels 32 (step S22).

After acquiring the return timing signals and the unique time information, the controller 20 uses the timing synchronization information creation unit 64 to create the timing information (step S24). The timing information is information containing the timing signal delay intervals for the respective image display panels 32 and the controller 20, and the unique time information of the respective image display panels 32 and the controller 20. After creating the timing information, the controller 20 uses the timing synchronization information creation unit 64 to create the timing synchronization information (step S26). The timing synchronization information is information containing the time synchronization information serving as information regarding a corresponding relationship between the unique time of the controller 20 and the unique time of each of the image display panels 32, and delay interval information until a command issued from the controller 20 reaches each of the image display panels 32. In the embodiment, the timing synchronization information creation unit 64 creates the timing synchronization information based on the plurality of sets of timing information. This processing is terminated at step S26 at which the timing synchronization information is created.

(Creation Processing for Array Information)

Next, the creation processing for the array information at step S12 in FIG. 9 will be described. The controller 20 does not display images on the image display panels 32 during the creation processing for the array information described below. First, in the array information unit 54 of the controller 20, the application voltage output instruction unit 70 selects, as an application image display panel, one of the image display panels 32A, 32B, 32C, 32D, 32E, 32F, 32G, 32H, and 32I. The application voltage output instruction unit 70 instructs this application image display panel to apply the application voltage V.sub.A to the drive electrode unit 38 of its own. The application voltage output instruction unit 70 then instructs standby image display panels which are all of the image display panels 32 other than the application image display panel to put the detection electrode units 39 into a standby state. The standby state is a state in which the application voltage V.sub.A can be detected to generate the detection voltage V.sub.D.

For example, in a case where the image display panel 32F is selected as the application image display panel, the application voltage output instruction unit 70 outputs an instruction to the application voltage output unit 94 included in the panel controller 36 of the image display panel 32F to apply the application voltage V.sub.A. The application voltage output instruction unit 70 may select the image display panel 32 other than the image display panel 32F as the application image display panel or alternatively, may select the plurality of image display panels 32 simultaneously as the application image display panels. However, the array information unit 54 selects, as the application image display panel, solely part of the image display panels 32 from all of the image display panels 32 at the same timing.

The application voltage output unit 94 of the image display panel 32F selected as the application image display panel applies the application voltage V.sub.A to the drive electrode unit 38 of its own based on the instruction from the application voltage output instruction unit 70. The application voltage output unit 94 sequentially applies the application voltage V.sub.A to the respective drive electrode units 38 in the order of the drive electrode units 38A, 38B, 38C, 38D, and 38E. The application voltage output unit 94 applies the application voltage V.sub.A to one drive electrode unit 38 only at the same time and accordingly, the voltage is not applied to the other drive electrode units 38 in this state. The order in which the application voltage output unit 94 applies the application voltage V.sub.A is not limited thereto. The application voltage output unit 94 of the image display panel 32F selected as the application image display panel puts the detection electrode units 39 of its own into a baseline drive mode. The baseline drive mode is a mode in which the application voltage V.sub.A is not detected (the detection voltage V.sub.D is not generated).

When the application voltage V.sub.A is applied to the drive electrode unit 38 of the image display panel 32F selected as the application image display panel, the detection voltage V.sub.D corresponding to that application voltage V.sub.A is generated at the detection electrode unit 39 in at least part of the standby image display panels which are the image display panels 32 other than the application image display panel. In a case where the detection electrode unit 39 of the standby image display panel is located at a position where that detection electrode unit 39 and the drive electrode unit 38 of the application image display panel constitute the capacitive component, the detection voltage V.sub.D is generated. Specifically, the detection electrode unit 39 of part of the standby image display panels forms a capacitor by acting as a pair of electrodes with the drive electrode unit 38 of the application image display panel. Therefore, the detection voltage V.sub.D is generated at this detection electrode unit 39 due to the application voltage V.sub.A to the drive electrode unit 38 acting as the other electrode. In the embodiment, the detection voltage V.sub.D is generated at the detection electrode unit 39 in the standby image display panel adjacent to the application image display panel in the X direction or the Y direction, of which details will be described later.

FIG. 13 is a diagram illustrating an exemplary application voltage and exemplary detection voltages. As illustrated in a graph (A) in FIG. 13, the application voltage V.sub.A is a voltage signal at a predetermined frequency having a maximum voltage value V.sub.A1. Likewise, as illustrated in a graph (B) in FIG. 13, the detection voltage V.sub.D is a voltage signal at a frequency corresponding (similar) to the application voltage V.sub.A, having a maximum voltage value V.sub.D1. In the embodiment, the detection voltage V.sub.D is generated at the detection electrode unit 39 included in the standby image display panel adjacent to the application image display panel in the X direction or the Y direction, as long as that detection electrode unit 39 is positioned on the application image display panel side. In other words, according to the embodiment, the detection voltage V.sub.D is generated at the detection electrode unit 39 adjacent to, in the X direction or the Y direction, the drive electrode unit 38 to which the application voltage V.sub.A is applied. The voltage generated at the detection electrode unit 39 due to the application voltage V.sub.A attenuates gradually as a distance between the detection electrode unit 39 and the drive electrode unit 38 to which the application voltage V.sub.A is applied increases. According to the embodiment, a case is considered where of the detection electrode unit 39 not adjacent to, in the X direction or the Y direction, the drive electrode unit 38 to which the application voltage V.sub.A is applied. In this case, the voltage is not generated at the detection electrode unit 39 as illustrated in graph (C) in FIG. 13, from a reason that a distance from the drive electrode unit 38 is larger than the case of the detection electrode unit 39 that has generated the detection voltage V.sub.D.

However, even in the case of the detection electrode unit 39 not adjacent to, in the X direction or the Y direction, the drive electrode unit 38 to which the application voltage V.sub.A is applied, when this detection electrode unit 39 is located at a position where the capacitive component is constituted by this detection electrode unit 39 and the drive electrode unit 38 to which the application voltage V.sub.A is applied, a low detection voltage V.sub.L (maximum voltage value V.sub.L1) is generated in some cases as illustrated in a graph (D) in FIG. 13. The low detection voltage V.sub.L is a voltage of which the maximum voltage value is smaller than that of the detection voltage V.sub.D. The low detection voltage V.sub.L is generated at the detection electrode unit 39 when that detection electrode unit 39 is located at a position more away from the drive electrode unit 38 to which the application voltage V.sub.A is applied than the detection electrode unit 39 that generates the detection voltage V.sub.D and at the same time, located at a position where the capacitive component is constituted by that detection electrode unit 39 and the drive electrode unit 38 to which the application voltage V.sub.A is applied. In this case, the controller 20 stores a detection voltage threshold V.sub.TH having a predetermined threshold in advance. The controller 20 then determines a voltage signal having a maximum voltage value larger than the detection voltage threshold V.sub.TH as the detection voltage V.sub.D. The controller 20 determines a voltage signal having a maximum voltage value smaller than the detection voltage threshold V.sub.TH as the low detection voltage V.sub.L. As described above, the voltage generated at the detection electrode unit 39 attenuates gradually as a distance between the detection electrode unit 39 and the standby image display panel increases. When the plurality of detection voltage thresholds V.sub.TH is provided, the controller 20 can detect positions of the image display panels 32 located farther.

Hereinafter, the generation of the detection voltage V.sub.D when the application voltage V.sub.A is sequentially applied to the drive electrode units 38 of the image display panel 32F will be described. FIG. 14 to FIG. 16 are explanatory diagrams for explaining the generation of the detection voltage when the application voltage is applied. As described above, the image display panel 32F serving as the application image display panel sequentially applies the application voltage V.sub.A to the drive electrode units 38A, 38B, 38C, 38D, and 38E. FIG. 14 illustrates the detection electrode units 39 at which the detection voltages V.sub.D are generated at a timing when the application voltage V.sub.A is applied to the drive electrode unit 38A of the image display panel 32F. FIG. 15 illustrates the detection electrode units 39 at which the detection voltages V.sub.D are generated at a timing when the application voltage V.sub.A is sequentially applied to the drive electrode units 38B, 38C, and 38D of the image display panel 32F. FIG. 16 illustrates the detection electrode units 39 at which the detection voltages VD are generated at a timing when the application voltage V.sub.A is applied to the drive electrode unit 38E of the image display panel 32F.

As illustrated in FIG. 14, when the application voltage V.sub.A is applied to the drive electrode unit 38A of the image display panel 32F, the detection voltages V.sub.D are generated at the detection electrode units 39 adjacent to the drive electrode unit 38A of the image display panel 32F in the X direction or the Y direction. Specifically, in the image display panel 32A, the detection voltage V.sub.D is generated at the detection electrode unit 39E adjacent to the drive electrode unit 38A of the image display panel 32F on a left side in the X direction. In the image display panel 32I, the detection voltage V.sub.D is generated at the detection electrode unit 39A adjacent to the drive electrode unit 38A of the image display panel 32F on a right side in the X direction. In the image display panel 32C, the detection voltages V.sub.D are generated at the detection electrode units 39A, 39B, 39C, 39D, and 39E adjacent to the drive electrode unit 38A of the image display panel 32F on an upper side in the Y direction. The detection electrode units 39 other than the aforementioned detection electrode units 39 are not adjacent to the drive electrode unit 38A of the image display panel 32F and thus, the detection voltage V.sub.D is not generated therein at this timing.

As illustrated in FIG. 15, when the application voltage V.sub.A is applied to the drive electrode units 38B, 38C, and 38D of the image display panel 32F, the detection voltages V.sub.D are generated at the detection electrode units 39 adjacent to the drive electrode units 38B, 38C, and 38D of the image display panel 32F in the X direction or the Y direction. Specifically, in the image display panel 32A, the detection voltage V.sub.D is generated at the detection electrode unit 39E adjacent to the drive electrode units 38B, 38C, and 38D of the image display panel 32F on the left side in the X direction. In the image display panel 32I, the detection voltage V.sub.D is generated at the detection electrode unit 39A adjacent to the drive electrode units 38B, 38C, and 38D of the image display panel 32F on the right side in the X direction. The detection electrode units 39 other than the aforementioned detection electrode units 39 are not adjacent to the drive electrode units 38B, 38C, and 38D of the image display panel 32F and thus, the detection voltage V.sub.D is not generated therein at this timing.

As illustrated in FIG. 16, when the application voltage V.sub.A is applied to the drive electrode unit 38E of the image display panel 32F, the detection voltages V.sub.D are generated at the detection electrode units 39 adjacent to the drive electrode unit 38E of the image display panel 32F in the X direction or the Y direction. Specifically, in the image display panel 32A, the detection voltage V.sub.D is generated at the detection electrode unit 39E adjacent to the drive electrode unit 38E of the image display panel 32F on the left side in the X direction. In the image display panel 32I, the detection voltage V.sub.D is generated at the detection electrode unit 39A adjacent to the drive electrode unit 38E of the image display panel 32F on the right side in the X direction. In the image display panel 32B, the detection voltages V.sub.D are generated at the detection electrode units 39A, 39B, 39C, 39D, and 39E adjacent to the drive electrode unit 38F of the image display panel 32F on a lower side in the Y direction. The detection electrode units 39 other than the aforementioned detection electrode units 39 are not adjacent to the drive electrode unit 38E of the image display panel 32F and thus, the detection voltage V.sub.D is not generated therein at this timing. In any states described in FIG. 14 to FIG. 16, the detection electrode units 39 of the image display panel 32F serving as the application image display panel have been put into the baseline drive mode and thus, the detection voltage V.sub.D is not generated.

As described above, the detection electrode units 39 at which the detection voltages V.sub.D are generated vary depending on the drive electrode unit 38 in the application image display panel to be applied to. The detection voltage transmission unit 96 of the standby image display panel successively outputs, to the detection voltage information creation unit 72 of the controller 20, the detection voltage V.sub.D generated at the detection electrode unit 39 of its own. The detection voltage information creation unit 72 of the controller 20 creates the detection voltage information A1 containing panel type information A2, detection electrode type information A3, detection electrode timing information A4 based on these detection voltages V.sub.D. The panel type information A2 is information indicating which image display panel 32 is the standby image display panel that has transmitted the detection voltage V.sub.D. The detection electrode type information A3 is information indicating at which detection electrode unit 39 the detection voltage V.sub.D has been generated, among all of the detection electrode units 39 included in the image display panel 32 that has transmitted the detection voltage V.sub.D. The detection electrode timing information A4 is information indicating at which timing the detection voltage V.sub.D has been generated at that detection electrode unit 39, among the timings when the application voltage V.sub.A has been sequentially applied. In other words, accordingly, the detection voltage information A1 is information indicating to which drive electrode unit 38 the application voltage V.sub.A has been applied among the plurality of drive electrode units 38 and at that time, and at which detection electrode unit 39 the detection voltage V.sub.D has been generated. The detection voltage transmission unit 96 may output the detection voltage V.sub.D to the panel controller 36 such that the panel controller 36 outputs the detection voltage V.sub.D to the detection voltage information creation unit 72 of the controller 20.

The detection voltage information creation unit 72 acquires the panel type information A2 using different network codes assigned to the respective image display panels 32 by the controller 20. However, for example, the detection voltage information creation unit 72 can acquire the panel type information A2 when the detection voltage transmission unit 96 of each of the image display panels 32 outputs the detection voltage V.sub.D coded for the identification of the respective image display panels 32. For example, the detection voltage transmission unit 96 outputs, to the controller 20, a signal obtained by adding a signal at a specific frequency to a signal of the detection voltage V.sub.D. As a result, an amplitude waveform of this signal becomes different for each of the image display panels 32. By analyzing this signal of the detection voltage V.sub.D, the detection voltage transmission unit 96 can recognize from which image display panel 32 this detection voltage information A1 is output.

The adjacent information creation unit 74 of the controller 20 creates the adjacent information B based on the detection voltage information A1. The adjacent information B is information indicating which image display panel 32 is the standby image display panel adjacent to the application image display panel in the X direction and which image display panel 32 is the standby image display panel adjacent to the application image display panel in the Y direction. Hereinafter, a method for creating the adjacent information B will be described.

First, a method for detecting the image display panel 32 adjacent in the X direction will be described. The standby image display panel adjacent to the image display panel 32F serving as the application image display panel on the left side in the X direction is the image display panel 32A. In the image display panel 32A as illustrated in FIG. 14 to FIG. 16, at all timings when the application voltage V.sub.A is sequentially applied to the drive electrode units 38A, 38B, 38C, 38D, and 38E of the image display panel 32F, the detection voltage V.sub.D is generated at the detection electrode unit 39E. The detection electrode unit 39E in the image display panel 32A is adjacent to the image display panel 32F in the X direction. The adjacent information creation unit 74 of the controller 20 detects the image display panel 32 in which the detection voltage V.sub.D has been generated at the detection electrode unit 39E which is a detection electrode located rightmost therein at all timings when the application voltage V.sub.A has been sequentially applied. Then the adjacent information creation unit 74 recognizes the detected image display panel 32 as the image display panel 32 adjacent to the application image display panel on the left side in the X direction.

The standby image display panel adjacent to the image display panel 32F serving as the application image display panel on the right side in the X direction is the image display panel 32I. In the image display panel 32I as illustrated in FIG. 14 to FIG. 16, at all timings when the application voltage V.sub.A is sequentially applied to the drive electrode units 38A, 38B, 38C, 38D, and 38E of the image display panel 32F, the detection voltage V.sub.D is generated at the detection electrode unit 39A. The detection electrode unit 39A in the image display panel 32I is adjacent to the image display panel 32F in the X direction. The adjacent information creation unit 74 of the controller 20 detects the image display panel 32 in which the detection voltage V.sub.D has been generated at the detection electrode unit 39A which is a detection electrode located leftmost therein at all timings when the application voltage V.sub.A has been sequentially applied. Then the adjacent information creation unit 74 recognizes the detected image display panel 32 as the image display panel 32 adjacent to the application image display panel on the right side in the X direction.

Next, a method for detecting the image display panel 32 adjacent in the Y direction will be described. The standby image display panel adjacent to the image display panel 32F serving as the application image display panel on the upper side in the Y direction is the image display panel 32C. In the image display panel 32C as illustrated in FIG. 14 to FIG. 16, at a timing when the application voltage V.sub.A is applied to the drive electrode unit 38A of the image display panel 32F, the detection voltages V.sub.D are generated at the detection electrode units 39A, 39B, 39C, 39D, and 39E. The detection electrode units 39A, 39B, 39C, 39D, and 39E in the image display panel 32C are adjacent to the image display panel 32F in the Y direction. The adjacent information creation unit 74 of the controller 20 detects the image display panel 32 in which the detection voltages V.sub.D have been generated at all of the detection electrode units 39 at a timing when the application voltage V.sub.A has been applied to the drive electrode unit 38A. Then the adjacent information creation unit 74 recognizes the detected image display panel 32 as the image display panel 32 adjacent to the application image display panel on the upper side in the Y direction.

The standby image display panel adjacent to the image display panel 32F serving as the application image display panel on the lower side in the Y direction is the image display panel 32B. In the image display panel 32B as illustrated in FIG. 14 to FIG. 16, at a timing when the application voltage V.sub.A is applied to the drive electrode unit 38E of the image display panel 32F, the detection voltages V.sub.D are generated at the detection electrode units 39A, 39B, 39C, 39D, and 39E. The detection electrode units 39A, 39B, 39C, 39D, and 39E in the image display panel 32B are adjacent to the image display panel 32F in the Y direction. The adjacent information creation unit 74 of the controller 20 detects the image display panel 32 in which the detection voltages V.sub.D have been generated at all of the detection electrode units 39 at a timing when the application voltage V.sub.A has been applied to the drive electrode unit 38E. Then adjacent information creation unit 74 recognizes the detected image display panel 32 as the image display panel 32 adjacent to the application image display panel on the lower side in the Y direction.

The adjacent information creation unit 74 of the controller 20 uses the above-described methods to create, based on the detection voltage information A1, the adjacent information B indicating which image display panel is the image display panel 32 adjacent to the application image display panel in the X direction or the Y direction.

After creating the adjacent information B, in the controller 20, the application voltage output instruction unit 70 selects, as the application image display panel, another image display panel different from the one that has been already selected from among the image display panels 32A, 32B, 32C, 32D, 32E, 32F, 32G, 32H, and 32I. The application voltage output instruction unit 70 then continues to create the adjacent information B by repeating the similar processing. For example, the controller 20 selects the image display panel 32G as the application image display panel subsequently to the image display panel 32F. The controller 20 repeats the similar processing, thereby creating the adjacent information B indicating which image display panel is the image display panel 32 adjacent to the image display panel 32G in the X direction or the Y direction. The controller 20 repeats the similar processing until all of the image display panels 32 have been selected as the application image display panel to create the adjacent information B of each of the image display panels 32 serving as information regarding the image display panel 32 adjacent to that image display panel 32.