Monolithic dual band antenna

Iancu , et al. A

U.S. patent number 10,381,725 [Application Number 15/141,011] was granted by the patent office on 2019-08-13 for monolithic dual band antenna. This patent grant is currently assigned to OPTIMUM SEMICONDUCTOR TECHNOLOGIES INC.. The grantee listed for this patent is Optimum Semiconductor Technologies, Inc.. Invention is credited to Surducan Emanoil, Sabin Daniel Iancu, Surducan Vasile.

View All Diagrams

| United States Patent | 10,381,725 |

| Iancu , et al. | August 13, 2019 |

Monolithic dual band antenna

Abstract

A monolithic dual band antenna is provided. The monolithic dual band antenna includes a first layer comprising a high frequency band antenna. The monolithic dual band antenna further includes a second layer underlying the first layer. The second layer includes a low frequency band antenna. The geometry of the high frequency antenna relative to the low frequency antenna causes resulting electric fields of the high frequency band antenna to be orthogonal to the resulting electric fields of the low frequency band antenna.

| Inventors: | Iancu; Sabin Daniel (Pleasantville, NY), Emanoil; Surducan (Cluj-Napoca, RO), Vasile; Surducan (Cluj-Napoca, RO) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Applicant: |

|

||||||||||

| Assignee: | OPTIMUM SEMICONDUCTOR TECHNOLOGIES

INC. (Tarrytown, NY) |

||||||||||

| Family ID: | 57834619 | ||||||||||

| Appl. No.: | 15/141,011 | ||||||||||

| Filed: | April 28, 2016 |

Prior Publication Data

| Document Identifier | Publication Date | |

|---|---|---|

| US 20170025757 A1 | Jan 26, 2017 | |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | Issue Date | ||

|---|---|---|---|---|---|

| 62194552 | Jul 20, 2015 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01Q 3/36 (20130101); H01Q 3/38 (20130101); H01Q 21/065 (20130101); H01Q 5/30 (20150115); H01Q 21/0093 (20130101); H01Q 5/40 (20150115); H01Q 9/0407 (20130101); H01Q 9/0414 (20130101); H01Q 21/28 (20130101); H01Q 23/00 (20130101); H01Q 1/243 (20130101) |

| Current International Class: | H01Q 5/30 (20150101); H01Q 21/00 (20060101); H01Q 3/38 (20060101); H01Q 3/36 (20060101); H01Q 21/06 (20060101); H01Q 1/24 (20060101); H01Q 9/04 (20060101); H01Q 23/00 (20060101); H01Q 5/40 (20150101); H01Q 21/28 (20060101) |

| Field of Search: | ;342/372,700 ;343/700 |

References Cited [Referenced By]

U.S. Patent Documents

| 5055852 | October 1991 | Dusseux |

| 5087922 | February 1992 | Tang |

| 6771221 | August 2004 | Rawnick |

| 6995720 | February 2006 | Shikata |

| 7746276 | June 2010 | Surducan |

| 7995000 | August 2011 | Manasson |

| 8059049 | November 2011 | Quan |

| 8269676 | September 2012 | Lin |

| 8294622 | October 2012 | Amari |

| 9379440 | June 2016 | Onaka |

| 9379449 | June 2016 | Cetiner |

| 9484631 | November 2016 | Napoles |

| 2002/0113737 | August 2002 | Brachat |

| 2004/0145526 | July 2004 | Puente Baliarda |

| 2009/0231226 | September 2009 | Quan |

| 2009/0322611 | December 2009 | Manasson et al. |

| 2010/0171674 | July 2010 | Henderson |

| 2014/0176082 | June 2014 | Visser |

| 2014/0368395 | December 2014 | Dauguet |

| 2016/0134004 | May 2016 | Haluba |

Other References

|

International Search Report and Written Opinion dated Jul. 19, 2016 for PCT/US16/42911. cited by applicant . Extended European Search Report, EP Appl No. 16828402.4; PCT/US2016/042911; dated Mar. 19, 2019. cited by applicant. |

Primary Examiner: Nguyen; Chuong P

Attorney, Agent or Firm: Zhong Law, LLC

Parent Case Text

CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of U.S. provisional patent application No. 62/194,552 filed Jul. 20, 2015, the disclosure of which is incorporated herein by reference in its entirety.

Claims

What is claimed is:

1. A monolithic dual band antenna, comprising: a first layer comprising a high frequency band antenna to generate a first electric field, wherein the high frequency band antenna comprises an array of patch antennas, each patch antenna being associated with a beam phase-tuned using a corresponding tunable phase shifter integrated circuit based on an input voltage, and wherein each beam associated with the corresponding patch antennas is characterized by a respective mini-lobe for composing a single lobe of the high frequency band antenna; and a second layer underlying the first layer, the second layer comprising a low frequency band antenna to generate a second electric field, wherein a geometry of the high frequency antenna relative to the low frequency antenna causes the first electric field generated by the high frequency band antenna to be orthogonal to the second electric field generated by the low frequency band antenna.

2. The antenna of claim 1, wherein the high frequency band is in a range of 18 GHz to 20 GHz and the low frequency band is in a range of 2.2 GHz to 2.8 GHz, and wherein the low frequency band antenna acts as a ground for the high frequency band antenna.

3. The antenna of claim 1, wherein the first layer comprises the array of patch antennas capable of beam forming.

4. The antenna of claim 1, wherein the first layer further comprises an antenna feeder distribution line.

5. The antenna of claim 1, wherein the tunable phase shifter integrated circuits are to form a beam of the array of patch antennas of the high frequency band antenna.

6. The antenna of claim 1, wherein the second layer comprises a single micro-strip patch for the low frequency band antenna.

7. The antenna of claim 6, wherein the second layer further comprises: a metallized copper foil layer; a dielectric layer of FR4 material underlying the metallized copper foil layer; and a metallized bottom layer underlying the dielectric layer forming the ground plane for the low frequency band antenna.

8. The antenna of claim 7, wherein the metallized copper foil layer is about 30 microns in thickness.

9. The antenna of claim 7, wherein, the dielectric layer is about 1 mm in thickness and has a dielectric relative permittivity of about 3.8.

10. The antenna of claim 1, further comprising a third layer underlying the second layer, the third layer comprising a control circuit for the high frequency band antenna.

11. The antenna of claim 10, wherein the control circuit is coupled to an array of tunable phase shifter integrated circuits located in the first layer, wherein the array of phase shifter integrated circuits are coupled to corresponding ones of the array of patch antennas of the high frequency band antenna.

12. The antenna of claim 10, wherein the third layer further comprises: a glue layer; a dielectric layer of FR4 material underlying the glue layer; and a layer underlying the dielectric layer comprising the control circuit.

13. The antenna of claim 12, wherein the glue layer is about 0.1 mm in thickness and has a dielectric relative permittivity of about 3.8.

14. The antenna of claim 12, wherein the layer comprising the control circuit is a conductive layer of about 0.1 mm thickness.

15. The antenna of claim 1, wherein the first layer further comprises: a conductive layer; a dielectric layer for the array of patch antennas of the high frequency band antenna, the dielectric layer underlying the conductive layer; and a glue layer underlying the dielectric layer.

16. The antenna of claim 15, wherein the glue layer comprises two layers of glue of about 0.1 mm thickness each and the dielectric layer is a layer of FR4 material about 0.5 mm thick with a relative dielectric permittivity of about 3.8.

17. The antenna of claim 1, wherein the first layer, the second layer, and a third layer are electrochemically deposited on a dielectric material.

18. A method, comprising: providing a monolithic dual band antenna] comprising: a first layer comprising a high frequency band antenna to generate a first electric field, wherein the high frequency band antenna comprises an array of patch antennas, each patch antenna being associated with a beam phase-tuned using a corresponding tunable phase shifter integrated circuit based on an input voltage, and wherein each beam associated with the corresponding patch antennas is characterized by a respective mini-lobe for composing a single lobe of the high frequency band antenna; and a second layer underlying the first layer, the second layer comprising a low frequency band antenna to generate a second electric field, wherein a geometry of the high frequency band antenna relative to the low frequency band antenna to cause the first electric field generated by the high frequency band antenna to be orthogonal to the second electric field generated by the low frequency band antenna.

19. The method of claim 18, wherein the high frequency band antenna comprises the array of patch antennas, and wherein providing the monolithic dual band antenna further comprises providing an array of tunable phase shifter integrated circuits coupled to corresponding ones of the array of patch antennas of the high frequency band antenna, and further comprising: forming, using the tunable phase shifter integrated circuits, a beam using the array of patch antennas of the high frequency band antenna.

Description

TECHNICAL FIELD

Embodiments of the present disclosure relate to antennas for digital wireless communications, and in particular, to a vertically stacked dual band antenna servicing a low frequency (LOW) band and a high frequency (HI) band.

BACKGROUND

Single band antennas typically take up significant real estate in a receiver/transmitter enclosure. With present day wireless mobile devices, there is a need to fit multiple antennas in approximately the same space previously occupied by a single antenna. Where two different frequency bands, and therefore two antennas are needed, if a difference in the center frequencies of two antennas is more than an octave (the higher frequency is twice the lower frequency), there is a need for two separate antennas, one for each receiver/transmitter. This will increase even more the space requirement in an enclosure. Unfortunately, related art antenna structures for mobile devices cannot fit two antennas operating in different frequency bands in the same enclosure.

SUMMARY

The above-described problems are addressed and a technical solution is achieved in the art by providing a monolithic dual band antenna. The monolithic dual band antenna includes a first layer comprising a high frequency band antenna. The monolithic dual band antenna further includes a second layer underlying the first layer. The second layer includes a low frequency band antenna. The geometry of the high frequency antenna relative to the low frequency antenna causes resulting electric fields of the high frequency band antenna to be orthogonal to the resulting electric fields of the low frequency band antenna. The low frequency band antenna may act as a ground for the high frequency band antenna.

The first layer may comprise a micro-strip array of patches capable of beam forming. The first layer may further include an array of tunable phase shifter integrated circuits coupled to corresponding ones of the micro-strip array of patches of the high frequency band antenna. The array of tunable phase shifter integrated circuits may be operable to form a beam using the micro-strip array of patches of the high frequency band antenna.

The second layer underlying the first layer may include a single micro-strip patch for the low frequency band antenna.

A third layer underlying the second layer may include a control circuit coupled to the array of tunable phase shifter located in the first layer. The array of phase shifters may be coupled to corresponding ones of the micro-strip array of patches of the high frequency band antenna.

BRIEF DESCRIPTION OF THE DRAWINGS

The present invention may be more readily understood from the detailed description of an exemplary embodiment presented below considered in conjunction with the following drawings:

FIG. 1 shows a perspective three-dimensional view of one example of a dual band antenna.

FIG. 2 shows a cross-sectional view of the dual band antenna of FIG. 1 arranged as a monolithic stack of layers.

FIG. 3 shows how the array of patches of the high frequency band antenna may be tuned by the tunable phase shifter integrated circuits to form a beam.

FIG. 4 shows a plot of S11--reflection loss versus frequency for the High frequency band antenna of FIGS. 1 and 2.

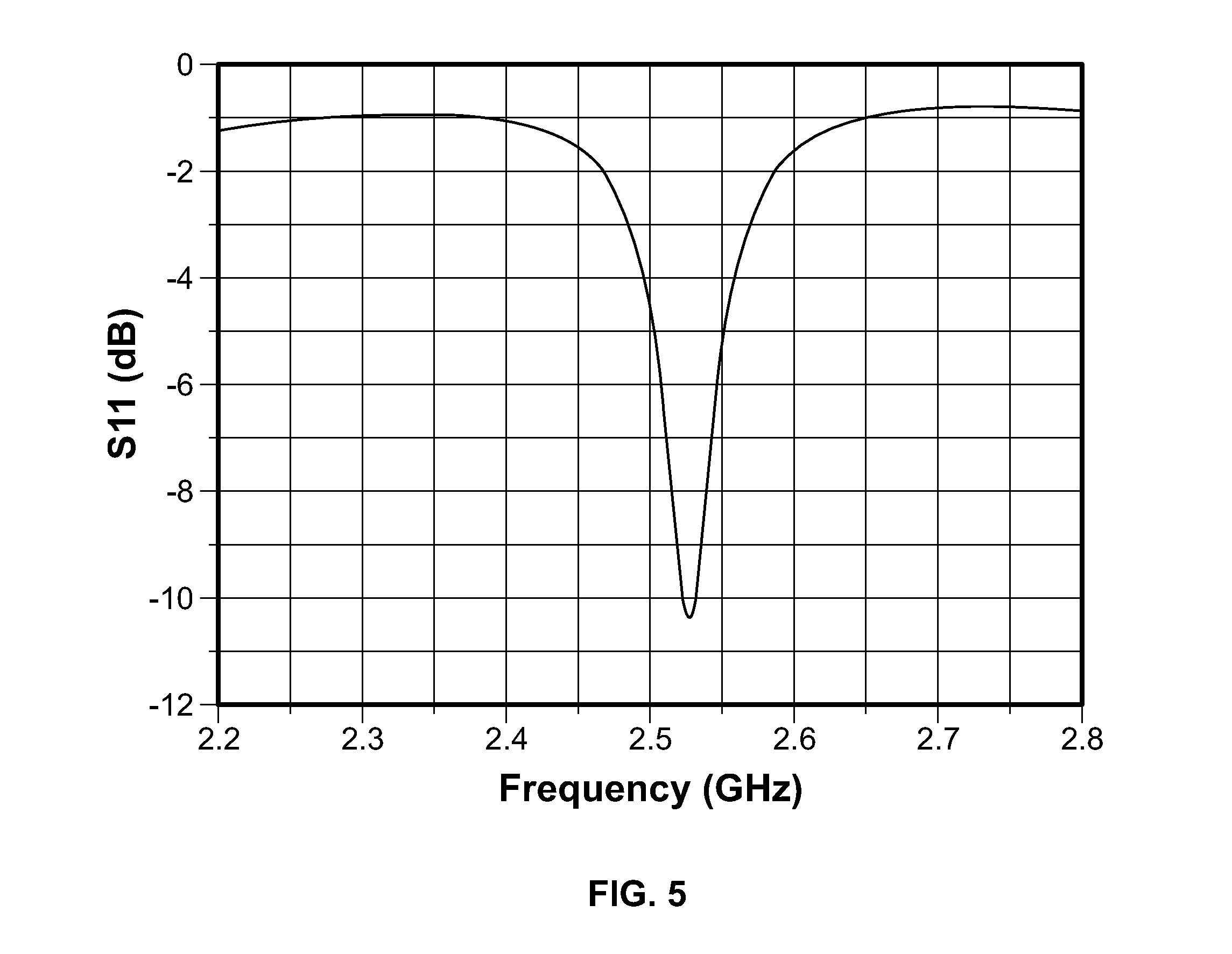

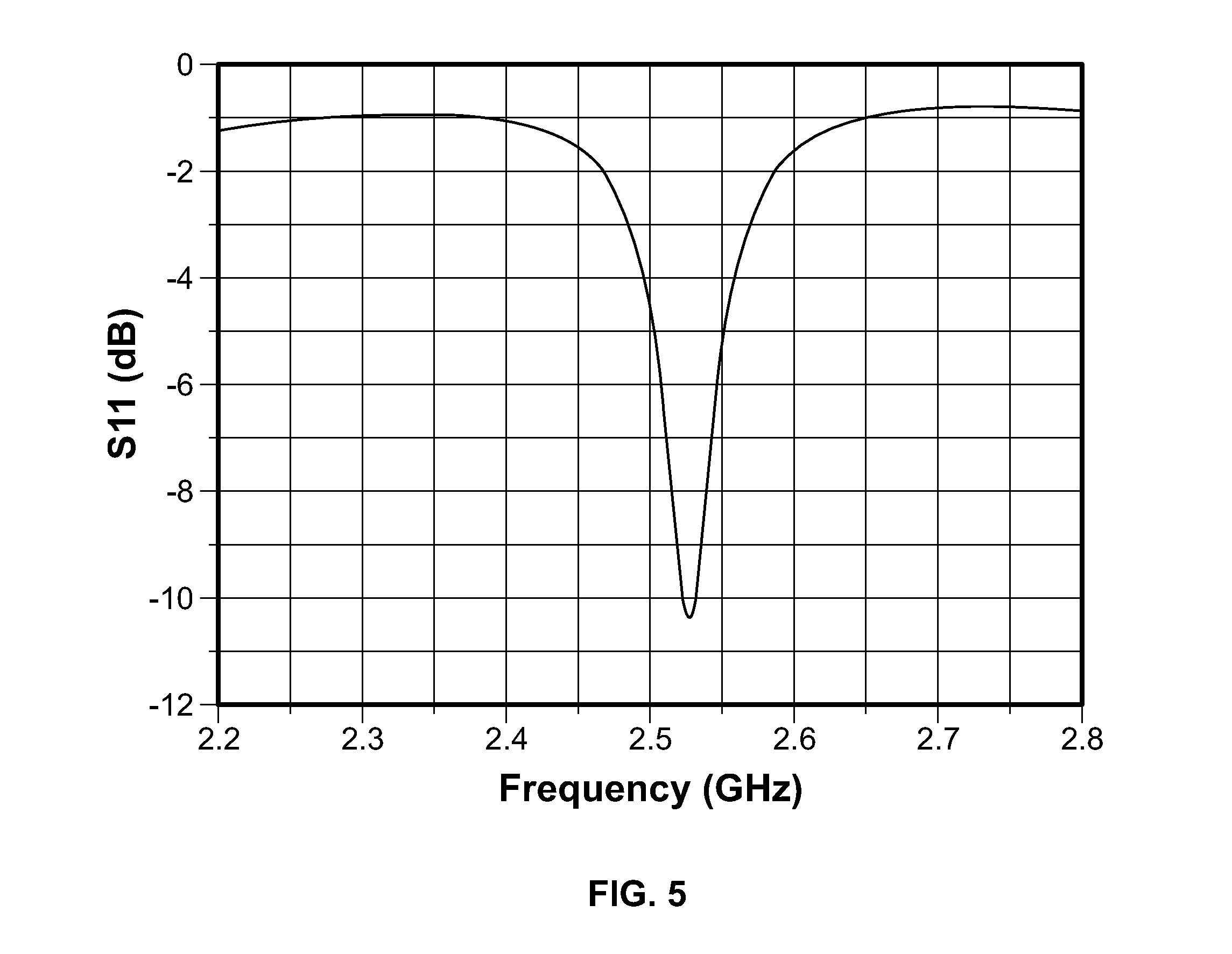

FIG. 5 shows a plot of S11--reflection loss versus frequency for the low frequency band antenna of FIGS. 1 and 2.

FIG. 6 is a plot of S12 reverse gain versus frequency between the high frequency band antenna and the low frequency band antenna.

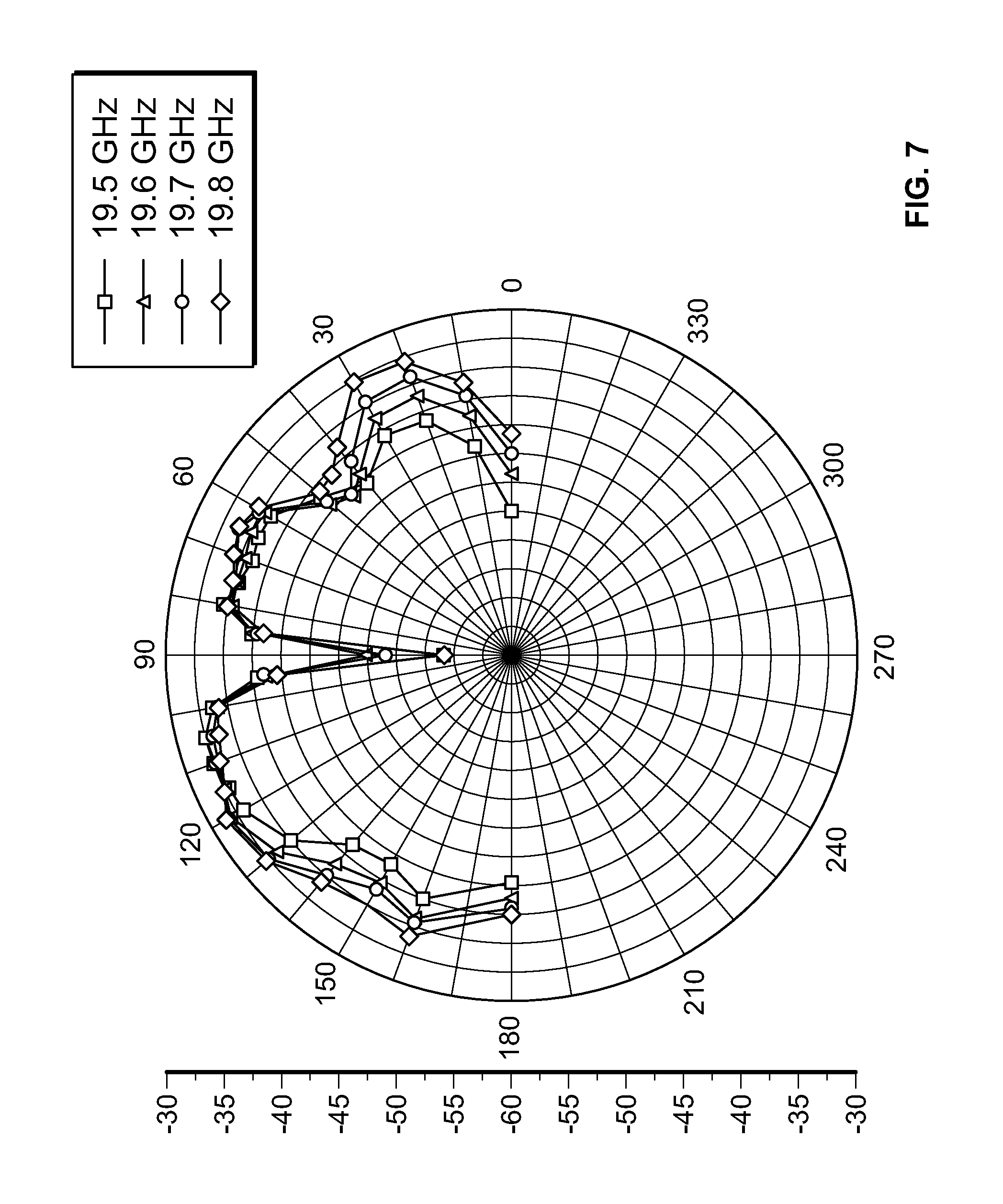

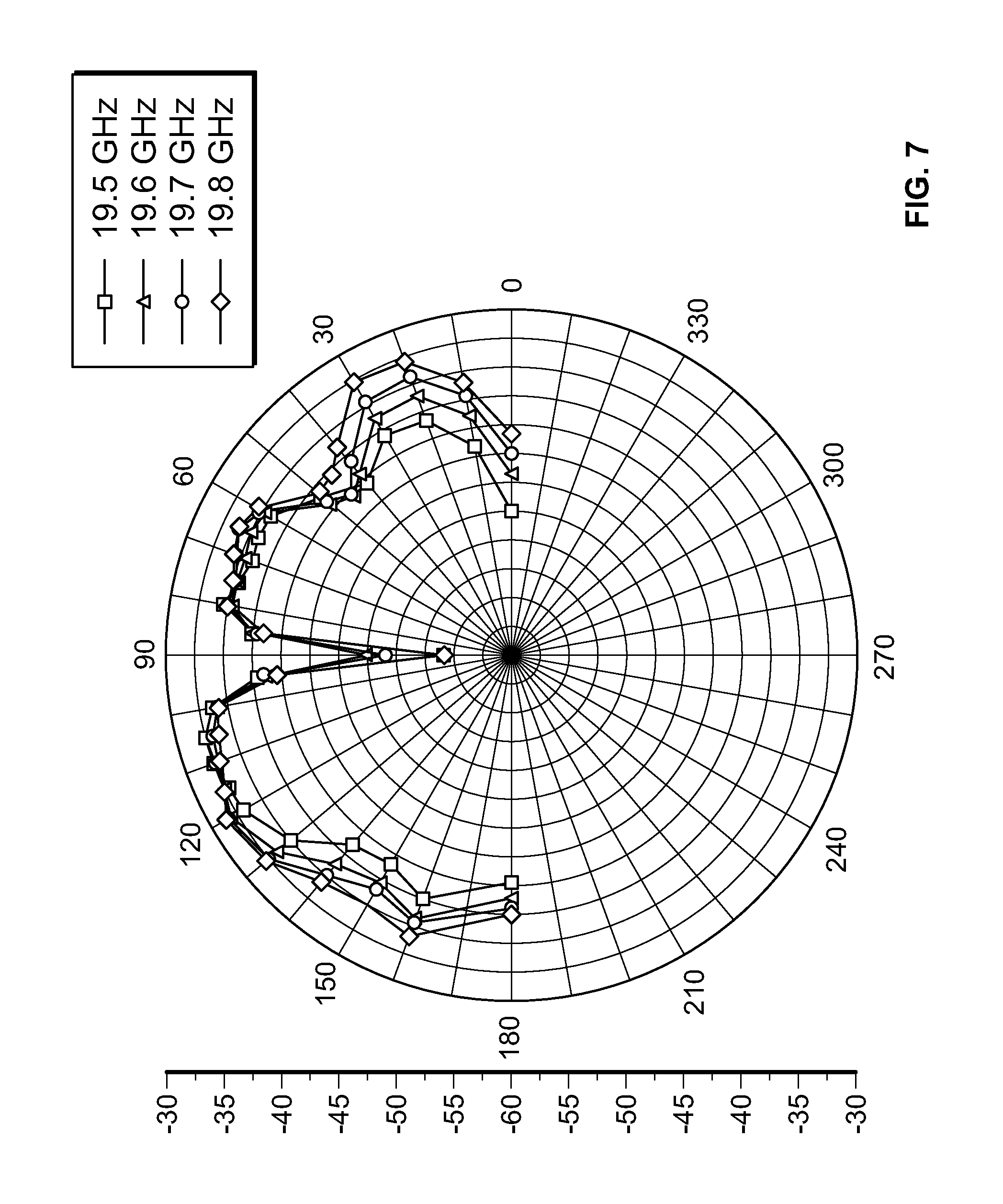

FIG. 7 is a transmission polar diagram for four different frequencies in the antenna passband.

FIG. 8 show a plot illustrating an example of beam control at 19 GHz, .DELTA..PHI..about.10.degree..

FIG. 9 is a schematic block diagram of the phase shifters control circuit of FIGS. 1 and 2.

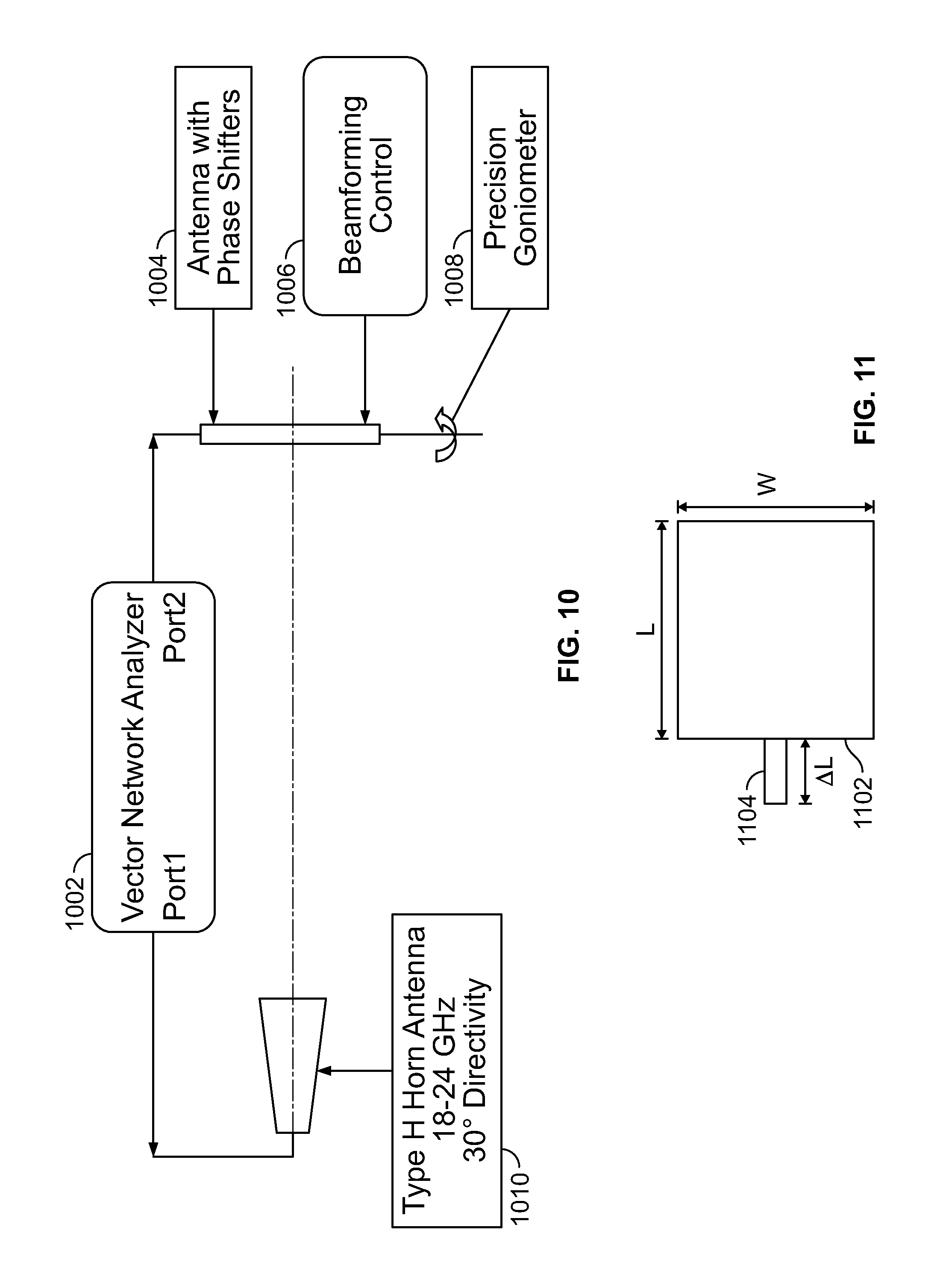

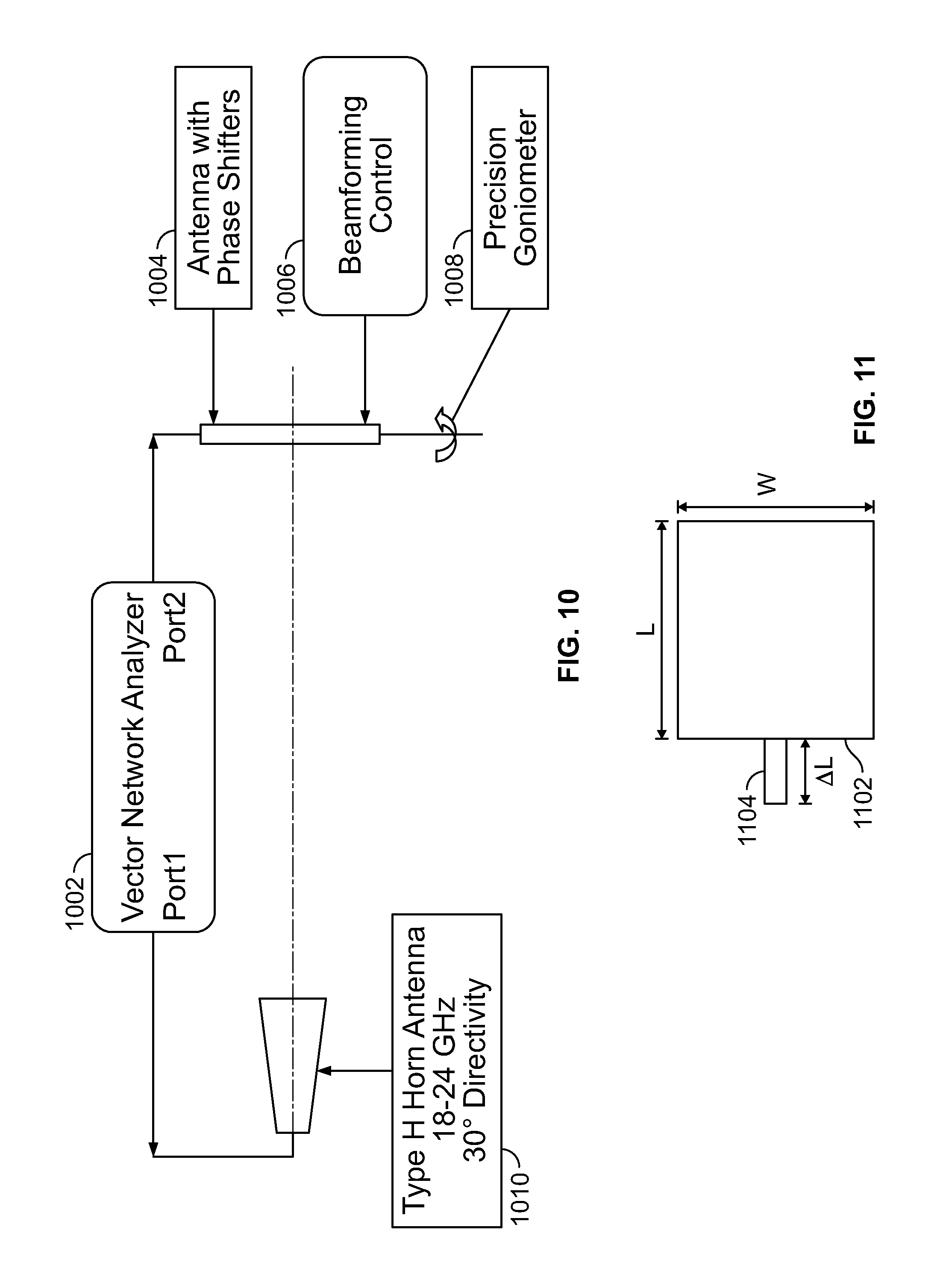

FIG. 10 is a schematic block diagram of an apparatus for measuring S parameters.

FIG. 11 shows a diagram illustrating how to calculate desired dimension of length L and width W of the single patch low frequency band antenna of FIG. 1.

DETAILED DESCRIPTION

Embodiments of the present disclosure describe a vertically stacked dual band antenna servicing a low frequency (LOW) band (e.g., 2.45 GHz) and a high frequency (HI) band (e.g., 20 GHz). The low frequency antenna may be a single micro strip patch. The high frequency antenna may be a multi-patch micro strip array capable of beam forming. The beam forming/direction of arrival may be effected by a voltage controlled phase shifter.

FIG. 1 shows a perspective three-dimensional view of one example of a dual band antenna 100 (a layer with a control circuit is not shown). The dual band antenna 100 may include a low frequency input terminal 102, an array of tunable phase shifter integrated circuits 104, a corresponding array of a patches (e.g., 8 patches) of a high frequency band antenna 106, a low frequency band antenna 108, a feeder distribution line 110 for the array of the multi-patch high frequency band antenna 106, and a high frequency input terminal 112. The physical dimensions of the dual band antenna 100 may be selected to be 3.5 mm.times.7 mm for each of the high frequency patches (at 20 GHz) and 27 mm.times.40 mm for the low frequency patch (at 2.45 GHz).

FIG. 2 shows a cross-sectional view of the dual band antenna 100 of FIG. 1 arranged as a monolithic stack of layers. The top group of layers 202-206 may comprise the high frequency band antenna 106. The top layer (TOP) 202 may include the array of patches (e.g., 8 patches) of the high frequency band antenna 106. Layer 202 may also include the antenna feeder distribution line 110 and the tunable phase shifter integrated circuits 104 coupled to corresponding ones of the array of patches (e.g., 8 patches) for the high frequency band antenna 106. The tunable phase shifter integrated circuits 104 are responsible for beam forming with the array of patches (e.g., 8 patches) high frequency band antenna 106. Layer 202 may be a conductive layer.

Layer 204 may be a first dielectric layer for the array of patches (e.g., 8 patches) high frequency band antenna 106. In one example, the dielectric layer 204 may be a layer of FR4 material about 0.5 mm thick with a relative dielectric permittivity of about 3.8 (the antenna frequency band and the size of the patch depend on this constant). The layer 206 is a glue layer comprising two layers of glue of about 0.1 mm thickness each.

The middle group of layers 208-212 may be the layers comprising the low frequency band antenna substantially underlying the layers 202-206 comprising the high frequency band antenna 106. The layer 208 may hold the single patch for the low frequency band antenna 108. The layer 208 may also function as the ground layer for the array of patches (e.g., 8 patches) high frequency band antenna 106. The layer 208 may be metallized and may comprise a copper foil of about 30 microns thickness (the metallized foils of all such layers in the dual band antenna 100 may comprise copper foils of about 30 microns thickness). The layer 210 may be a second dielectric layer of FR4 material of about 1 mm thickness and may also have a dielectric relative permittivity of about 3.8. The bottom layer 212 may be metallized and may represent the ground plane for the low frequency band antenna 108.

The last group of layers 214-218 may hold a control circuit for the high frequency band antenna 106. The last group of layers 214-218 substantially underlays the middle group of layers 208-212 comprising the low frequency band antenna 108. The layer 214 is a glue layer of about 0.1 mm thickness. The layer 216 may be a third dielectric layer of FR4 material of about 1 mm thickness and may also have a dielectric relative permittivity of about 3.8. The bottom layer 218 may hold the electronic devices and the interconnections. The control circuit may connected to the phase shifters on the TOP layer 202 through vias (not shown). The layer 218 may be a conductive layer of about 0.1 mm thickness.

More particularly, all conductive layers are electrochemically deposited on the dielectric material. The glue layer 206 may be applied between the group of layers 202-204 and the group of layers 208-212. The glue layer 214 may be applied between group of layers 208-212 and the group of layers 216-218. The layer 206 may two-layers of glue while the layer 214 is one single layer. Each layer may be 0.1 mm thick.

In order to decouple the high frequency band antenna 106 from the low frequency band antenna 108, the geometry was selected such that the resulting electric fields of the high frequency band antenna 106 from the low frequency band antenna 108 may be orthogonal to each other as shown in FIG. 1.

The multiply-layer antenna configuration 100 saves significant real estate in a receiver/transmitter enclosure. The high frequency band antenna 106 may be configured to overly the low frequency band antenna 108, the latter acting as ground for the high frequency band antenna 106.

FIG. 3 shows how the array of patches of the high frequency band antenna 106 may be tuned by the tunable phase shifter integrated circuits 104 to form a beam. The inputs 1, 2, 3, 4 shown in FIG. 3 are the control line inputs for a respective first half of the phase shifters of the voltage-controlled phase shifter integrated circuits 104, while the inputs 5, 6, 7, 8 shown in FIG. 3 are the control line inputs for a corresponding second half of the phase shifters of the voltage-controlled phase shifter integrated circuits 104 (See FIG. 9). The phase shift for each patch is depicted in Table 1 of FIG. 3. Table 1 shows the value of the angle .PHI.o depends on each specific value of individual mini-patch phases.

Applying different voltages on the inputs phase shifter integrated circuits 104 result different phase shifts per patch antenna. For a certain combination of phase shifts, the high frequency band antenna 106 may transmit maximum power or receive maximum power in a particular direction.

The high frequency band antenna 106 may be composed of 8 mini patch antennas. Each one of the mini patch antennas may be fed via a phase shifter connected through a micro-strip. These 8 antennas may behave as a single antenna having one single radiating lobe (8 mini-lobes composed in one single larger lobe). If the microwave phase on each of mini antennas is different from the others, the resulting lobe may be bent by an angle .PHI.o depending on the microwave phase value .DELTA..PHI.i on each of the mini-patches.

FIGS. 4 and 5 show plots of two-port system S-parameters. More particularly, FIG. 4 shows a plot of S11--reflection loss versus frequency for the high frequency band antenna 106, while FIG. 5 shows a plot of S11--reflection loss versus frequency for the low frequency band antenna 108. (S.sub.11 is the input port voltage reflection coefficient; S.sub.12 is the reverse voltage gain; S.sub.21 is the forward voltage gain; and S.sub.22 is the output port voltage reflection coefficient).

FIG. 6 is a plot of S12 reverse gain versus frequency between the high frequency band antenna 106 and the low frequency band antenna 108. FIG. 6 illustrates the relative decoupling of the high frequency band antenna 106 and the low frequency band antenna 108. FIG. 6 shows that the decoupling may be better than -20 dB.

FIG. 7 is a transmission polar diagram for four different frequencies in the antenna passband (S12 as a function of angle for uncontrolled phase shifters). FIG. 8 show a plot illustrating an example of beam control at 19 GHz, .DELTA..PHI..about.10.degree.. FIG. 8 further shows one example of directivity shift with 10 degrees.

FIG. 9 is a schematic block diagram of the phase shifters control circuit 900. The phase shifters control circuit 900 may include a pair of digital-to-analog voltage converters 902, 906 (e.g., MCP4728, I2C, operating at 1 MHz), an array of analog voltage-controlled phase shifters 904 (e.g., MCP933LP4E, operating at 18-24 GHz) coupled to the corresponding array of patches 916 of the high frequency band antenna 106, a connector for serial digital input control of the digital-to-analog voltage converters 902, a +5V DC voltage supply 910 for powering the digital-to-analog voltage converters 902, 906 and the array of analog voltage-controlled phase shifters 904, an input terminal 912 coupled to the low frequency band antenna 108, 918 and a HI input terminal 914 coupled to the high frequency band antenna 106, 916.

As noted above, the phase shifters control circuit 900 may include two programmable serial interface digital to analog (D to A) converters 902, 906, respectively, having four analog outputs each (3, 4, 5, 6 and respectively 1, 2, 7, 8). The control logic may include a serial data input (SDA), a serial clock input (SCLK) and a load (LD) input coupled to a microcontroller/processor (not shown) through the connector 908. The D to A converters 902, 906 may be supplied with 5 V from a low noise power supply 910 and may share the same serial (I2C) control bus.

In operation, serialized digital values corresponding to phase shift voltages are input over the I2C bus by the microprocessor through the connector 908 to the D to A converters 902, 906, the latter applying corresponding voltages representing corresponding phase shifts to be applied to the corresponding voltage-controlled phase shifters 904 to control the beam forming of the patches of the high frequency band antenna 106.

FIG. 10 is a schematic block diagram of an apparatus for measuring S parameters. measurement block diagram. To measure the S parameters, the key instrument is a vector network analyzer (VNA) 1002 operating over the desired frequency bands. In the measurement block diagram of FIG. 10, the test antenna (antenna with phase shifters) 1004 is connected to the Port 2 of the VNA 1002. The test antenna 1004 is mounted on a precision goniometer 1008. The phase shifter control circuit is connected to a programmed computer (not shown) via a digital interface. Port 1 of the VNA 1002 is connected to an H type horn antenna 1010 with the following parameters: frequencies band 18-24 GHz, directivity 30.degree.. The distance between the horn antenna 1010 and the test antenna 1004 is 22 cm. The VNA 1002 measures the transmission between antennas 1004, 1010 (S12 and S21, S12=S21 in this case) and the reflection from the antenna 1004 on each port (S11, S22). To measure beam forming capability of the antenna 1004, the following procedure was used.

The test antenna 1004 is the emitter, while the horn antenna 1010 is the receiver. The transmission coefficient S21 from the emitter 1004 to the receiver 1010 is measured and saved on the VNA screen. Without control, S21 represents a reference (.PHI.o=0). The beam forming control unit 1006 sets the phase shifters values and the precision goniometer 1008 rotates the test antenna 1004 until a maximum is detected. This is how the FIG. 8 diagram is obtained.

FIG. 11 shows a diagram illustrating how to calculate desired dimension of length L and width W of the single patch low frequency band antenna 108 of FIG. 1. The micro-strip patch antenna dimensions calculation steps are as follows:

Step 1: Calculation of the Width (W)--

.times..times..times. ##EQU00001##

Step 2: Calculation of the Effective Dielectric Constant. This is based on the height, dielectric constant of the dielectric and the calculated width of the patch antenna.

.function..times. ##EQU00002##

Step 3: Calculation of the Effective Length

.times..times. ##EQU00003##

Step 4: Calculation of the Length Extension .DELTA.L (1104)

.DELTA..times..times..times..times..times..times..times. ##EQU00004##

Step 5: Calculation of Actual Length of the Patch L=L.sub.eff-2.DELTA.L

where the following parameters are used: f.sub.0 is the resonance frequency W is the width of the patch L is the length of the patch h is the thickness .epsilon..sub.r is the relative permittivity of the dielectric substrate c is the Speed of light: 3.times.10.sup.8

In the foregoing description, numerous details are set forth. It will be apparent, however, to one of ordinary skill in the art having the benefit of this disclosure, that the present disclosure may be practiced without these specific details. In some instances, well-known structures and devices are shown in block diagram form, rather than in detail, in order to avoid obscuring the present disclosure.

Some portions of the detailed description have been presented in terms of algorithms and symbolic representations of operations on data bits within a computer memory. These algorithmic descriptions and representations are the means used by those skilled in the data processing arts to most effectively convey the substance of their work to others skilled in the art. An algorithm is here, and generally, conceived to be a self-consistent sequence of steps leading to a desired result. The steps are those requiring physical manipulations of physical quantities. Usually, though not necessarily, these quantities take the form of electrical or magnetic signals capable of being stored, transferred, combined, compared, and otherwise manipulated. It has proven convenient at times, principally for reasons of common usage, to refer to these signals as bits, values, elements, symbols, characters, terms, numbers, or the like.

It should be borne in mind, however, that all of these and similar terms are to be associated with the appropriate physical quantities and are merely convenient labels applied to these quantities. Unless specifically stated otherwise as apparent from the following discussion, it is appreciated that throughout the description, discussions utilizing terms such as "segmenting", "analyzing", "determining", "enabling", "identifying," "modifying" or the like, refer to the actions and processes of a computer system, or similar electronic computing device, that manipulates and transforms data represented as physical (e.g., electronic) quantities within the computer system's registers and memories into other data similarly represented as physical quantities within the computer system memories or registers or other such information storage, transmission or display devices.

The disclosure also relates to an apparatus for performing the operations herein. This apparatus may be specially constructed for the required purposes, or it may include a general purpose computer selectively activated or reconfigured by a computer program stored in the computer. Such a computer program may be stored in a computer readable storage medium, such as, but not limited to, any type of disk including floppy disks, optical disks, CD-ROMs, and magnetic-optical disks, read-only memories (ROMs), random access memories (RAMs), EPROMs, EEPROMs, magnetic or optical cards, or any type of media suitable for storing electronic instructions.

The words "example" or "exemplary" are used herein to mean serving as an example, instance, or illustration. Any aspect or design described herein as "example` or "exemplary" is not necessarily to be construed as preferred or advantageous over other aspects or designs. Rather, use of the words "example" or "exemplary" is intended to present concepts in a concrete fashion. As used in this application, the term "or" is intended to mean an inclusive "or" rather than an exclusive "or". That is, unless specified otherwise, or clear from context, "X includes A or B" is intended to mean any of the natural inclusive permutations. That is, if X includes A; X includes B; or X includes both A and B, then "X includes A or B" is satisfied under any of the foregoing instances. In addition, the articles "a" and "an" as used in this application and the appended claims should generally be construed to mean "one or more" unless specified otherwise or clear from context to be directed to a singular form. Moreover, use of the term "an embodiment" or "one embodiment" or "an implementation" or "one implementation" throughout is not intended to mean the same embodiment or implementation unless described as such.

Reference throughout this specification to "one embodiment" or "an embodiment" means that a particular feature, structure, or characteristic described in connection with the embodiment is included in at least one embodiment. Thus, the appearances of the phrase "in one embodiment" or "in an embodiment" in various places throughout this specification are not necessarily all referring to the same embodiment. In addition, the term "or" is intended to mean an inclusive "or" rather than an exclusive "or."

Whereas many alterations and modifications of the disclosure will no doubt become apparent to a person of ordinary skill in the art after having read the foregoing description, it is to be understood that any particular embodiment shown and described by way of illustration is in no way intended to be considered limiting. Therefore, references to details of various embodiments are not intended to limit the scope of the claims, which in themselves recite only those features regarded as the disclosure.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

M00001

M00002

M00003

M00004

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.