Array substrate having partially oxidized source electrode, drain electrode and data line

Choi , et al.

U.S. patent number 10,338,438 [Application Number 14/436,066] was granted by the patent office on 2019-07-02 for array substrate having partially oxidized source electrode, drain electrode and data line. This patent grant is currently assigned to BOE TECHNOLOGY GROUP CO., LTD.. The grantee listed for this patent is BOE TECHNOLOGY GROUP CO., LTD.. Invention is credited to Seungjin Choi, Heecheol Kim, Youngsuk Song, Seongyeol Yoo.

| United States Patent | 10,338,438 |

| Choi , et al. | July 2, 2019 |

Array substrate having partially oxidized source electrode, drain electrode and data line

Abstract

The embodiments of the invention disclose an array substrate, a manufacturing method thereof and a display device. Due to the fact that the surfaces of a source electrode, a drain electrode and a data line which are arranged on the same layer are provided with an oxide film which is formed after annealing treatment is conducted on the source electrode, the drain electrode and the data line, in the process that the pattern of a pixel electrode is formed on the source electrode, the drain electrode and the data line by the adoption of a composition technology, the oxide film can protect the source electrode and the data line under the oxide film from being corroded by an etching agent when the pattern of the pixel electrode is formed by etching, and the display quality of a display panel will not be affected.

| Inventors: | Choi; Seungjin (Beijing, CN), Kim; Heecheol (Beijing, CN), Song; Youngsuk (Beijing, CN), Yoo; Seongyeol (Beijing, CN) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Applicant: |

|

||||||||||

| Assignee: | BOE TECHNOLOGY GROUP CO., LTD.

(Beijing, CN) |

||||||||||

| Family ID: | 51041017 | ||||||||||

| Appl. No.: | 14/436,066 | ||||||||||

| Filed: | July 11, 2014 | ||||||||||

| PCT Filed: | July 11, 2014 | ||||||||||

| PCT No.: | PCT/CN2014/082023 | ||||||||||

| 371(c)(1),(2),(4) Date: | April 15, 2015 | ||||||||||

| PCT Pub. No.: | WO2015/143796 | ||||||||||

| PCT Pub. Date: | October 01, 2015 |

Prior Publication Data

| Document Identifier | Publication Date | |

|---|---|---|

| US 20170003553 A1 | Jan 5, 2017 | |

Foreign Application Priority Data

| Mar 28, 2014 [CN] | 2014 1 0130729 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G02F 1/136286 (20130101); G02F 1/134309 (20130101); H01L 27/124 (20130101); G02F 1/13439 (20130101); G02F 1/133345 (20130101); H01L 27/1259 (20130101); H01L 21/02244 (20130101); H01L 21/02255 (20130101); G02F 2001/134318 (20130101); G02F 2201/123 (20130101); G02F 2001/136295 (20130101); G02F 2201/121 (20130101); G02F 1/136227 (20130101); G02F 2001/134372 (20130101); G02F 1/134363 (20130101) |

| Current International Class: | H01L 21/77 (20170101); H01L 21/02 (20060101); G02F 1/1362 (20060101); G02F 1/1343 (20060101); G02F 1/1333 (20060101); H01L 27/12 (20060101) |

References Cited [Referenced By]

U.S. Patent Documents

| 2006/0102907 | May 2006 | Lee |

| 2008/0227243 | September 2008 | Yang |

| 2009/0101903 | April 2009 | Chen |

| 2010/0099205 | April 2010 | Kim |

| 2010/0155733 | June 2010 | Moon |

| 2011/0227085 | September 2011 | Nakamura |

| 2013/0063675 | March 2013 | Misaki |

| 2013/0140556 | June 2013 | Park |

| 2013/0207103 | August 2013 | Lee |

| 2014/0078438 | March 2014 | Suzuki |

| 2014/0085577 | March 2014 | Zhou |

| 2015/0153600 | June 2015 | Won |

| 1710721 | Dec 2005 | CN | |||

| 101132011 | Feb 2008 | CN | |||

| 102227761 | Oct 2011 | CN | |||

| 102799038 | Nov 2012 | CN | |||

| 103337522 | Oct 2013 | CN | |||

| 103915452 | Jul 2014 | CN | |||

| 203760478 | Aug 2014 | CN | |||

Other References

|

Chinese Office Action with English Language Translation, dated Jan. 13, 2016, Chinese Application No. 201410130729.0. cited by applicant . International Search Report (PCT/CN2014/082023) dated Dec. 31, 2014, 13 pages. cited by applicant . "Extended European Search Report," EP Application No. 14861185.8 (dated Dec. 21, 2017). cited by applicant. |

Primary Examiner: Parendo; Kevin

Attorney, Agent or Firm: Womble Bond Dickinson (US) LLP

Claims

The invention claimed is:

1. An array substrate comprising: an underlay substrate; a source electrode, a drain electrode and a data line arranged in the same layer on the underlay substrate; a pixel electrode arranged in the same layer of the source electrode, the drain electrode and the data line; an oxide film converted from a surface portion of the source electrode, the drain electrode and the data line by partially oxidizing the source electrode, the drain electrode and the data line with an annealing treatment; a first via hole arranged over the drain electrode and penetrating through the oxide film; a connecting portion electrically connecting the drain electrode with the pixel electrode through the first via hole; a passivation layer extending over the drain electrode; the pixel electrode being arranged at a top of the passivation layer; and a common electrode arranged at a bottom of the passivation layer and opposite to the pixel electrode; and wherein patterns of the common electrode and the drain electrode do not overlap; the connecting portion and the pixel electrode are arranged in the same layer, and the first via hole also penetrates through the passivation layer.

2. The array substrate according to claim 1, wherein the material of the source electrode, the drain electrode and the data line is copper, the material of the oxide film is copper oxide.

3. The array substrate according to claim 1, wherein the array substrate further comprises: an active layer electrically connected with the source electrode and the drain electrode and arranged below the source electrode and the drain electrode; a gate electrode insulated with the active layer and arranged opposite the active layer.

4. The array substrate according to claim 1, wherein the thickness of the oxide film is 10 nm to 100 nm.

5. A display device comprising the array substrate according to claim 1.

6. The display device according to claim 5, wherein the material of the source electrode, the drain electrode and the data line is copper, the material of the oxide film is copper oxide.

7. The display device according to claim 5, wherein the array substrate further comprises: an active layer electrically connected with the source electrode and the drain electrode and arranged below the source electrode and the drain electrode; a gate electrode insulated with the active layer and arranged opposite the active layer.

8. The display device according to claim 5, wherein the thickness of the oxide film is 10 nm to 100 nm.

Description

FIELD OF THE INVENTION

The present invention relates to the field of display, in particular to an array substrate, a manufacturing method thereof and a display device.

BACKGROUND OF THE INVENTION

Liquid crystal display is mainly composed of an opposite substrate, an array substrate, and a liquid crystal layer located between the two substrates. Generally, patterns such as gate lines, data lines, thin film transistors (TFT) and pixel electrodes are arranged on one side of the array substrate. A TFT specifically comprises: a gate electrode and an active layer mutually insulated; a source electrode and a drain electrode electrically connected to the active layer respectively; wherein the gate electrode is electrically connected to the gate line, the source electrode is electrically connected to the data line, the drain electrode is electrically connected to the pixel electrode. Patterns such as black matrix and color films are arranged on one side of a color film substrate.

At present, in the existing manufacturing process of the array substrate, usually a one-time composition process is adopted to form the patterns of a gate electrode 102 and a gate line 103 on an underlay substrate 101, as shown in FIG. 1a; then a gate insulating layer is formed on the underlay substrate 101; a pattern of an active layer 104 is formed on a region of the gate insulating layer corresponding to the pattern of the gate electrode 102, as shown in FIG. 1b; then a pattern of a etching barrier layer 105 is formed, as shown in FIG. 1c; a one-time composition process is adopted to form the patterns of a source electrode 106, a drain electrode 107 and a data line 108, as shown in FIG. 1d; finally, a pattern of a pixel electrode 109 electrically connected with the drain electrode 107 is formed, as shown in FIG. 1e. After the pattern of the pixel electrode 109 is formed, patterns of an insulating layer and common electrodes 110 are typically formed, as shown in FIG. 1f.

After the patterns of the source electrode, drain electrode and data line are formed, a pattern of the pixel electrode is typically formed with a photolithography process, i.e., an indium tin oxides (ITO) film and a photoresist film are formed in sequence by stacking on the patterns of the source electrode, drain electrode and data line; then the photoresist film is treated with exposure and development processes; an etching process is performed with etching agent for the ITO film on which the photoresist does not cover, wherein the region treated by the etching process comprises the ITO film covering over the source electrode and the data line; finally, the remaining photoresist is peeled off to obtain the pattern of the pixel electrode.

In the specific implementation, metals such as copper are commonly used for the patterns of the source electrode, the drain electrode and the data line; in such a manner, during the etching process for the ITO film covering over the patterns of the source electrode and the data line, etching agent will be in direct contact with the source electrode and the data line, resulting in corrosion of the source electrode and the data line; moreover, the high temperature environment during the subsequent forming of insulating layer will accelerate the corrosion process, which will affect the display quality of the liquid crystal display.

Therefore, how to avoid the source electrode and the data line being corroded by the etching agent is a technical problem to be solved by those skilled in the art.

SUMMARY OF THE INVENTION

In view of this, embodiments of the invention provide an array substrate, a manufacturing method thereof and a display device, to solve the problem of the source electrode and the data line being corroded by the etching agent in the prior art.

Therefore, an embodiment of the present invention provides an array substrate, the array substrate comprises: an underlay substrate; a source electrode, a drain electrode and a data line, which are arranged in the same layer on the underlay substrate; and a pixel electrode arranged on the layer, in which the source electrode, the drain electrode and the data line are arranged; the array substrate further comprises: a connecting portion;

an oxide film which is formed on the surfaces of the source electrode, the drain electrode and the data line after annealing treatment is conducted on the source electrode, the drain electrode and the data line;

a first via hole arranged over the drain electrode and penetrating through the oxide film; the connecting portion electrically connects the drain electrode with the pixel electrode through the first via hole.

In the array substrate provided by the embodiment of the present invention, due to the fact that the surfaces of a source electrode, a drain electrode and a data line which are arranged on the same layer are provided with an oxide film which is formed after annealing treatment is conducted on the source electrode, the drain electrode and the data line, in the process that a pattern of a pixel electrode is formed on the source electrode, the drain electrode and the data line by the adoption of a composition technology, the oxide film can protect the source electrode and the data line under the oxide film from being corroded by an etching agent when the pattern of the pixel electrode is formed by etching, and the display quality of a display panel will not be affected; meanwhile, a connecting portion enables the drain electrode to be electrically connected with the pixel electrode through a first via hole arranged over the drain electrode and penetrating through the oxide film, therefore the normal display function of the display panel can be ensured.

In particular, when the array substrate provided by the embodiment of the present invention is applied in an advanced super dimensional field switch type liquid crystal display, the array substrate can further comprise: a passivation layer and a common electrode arranged sequentially over the pixel electrode; the passivation layer extends over the drain electrode;

the connecting portion and the common electrode are arranged in the same layer and are mutually insulated, and the first via hole also penetrates through the passivation layer;

patterns of the pixel electrode, the source electrode, the drain electrode and the data line do not overlap mutually;

a second via hole arranged over the pixel electrode and penetrating through the passivation layer, the connecting portion is electrically connected with the pixel electrode through the second via hole.

Or, in particular, when the array substrate provided by the embodiment of the present invention is applied in an advanced super dimensional field switch type liquid crystal display, the array substrate can further comprise: a common electrode arranged between the pixel electrode and the layer in which the source electrode, the drain electrode and the data line are arranged; and a passivation layer arranged between the pixel electrode and the common electrode, the passivation layer extends over the drain electrode;

patterns of the common electrode and the drain electrode do not overlap mutually;

the connecting portion and the pixel electrode are arranged in the same layer, and the first via hole also penetrates through the passivation layer.

Preferably, to decrease the resistance of the source electrode, the drain electrode and the data line, in the array substrate provided by the embodiment of the present invention, the material of the source electrode, the drain electrode and the data line is copper, the material of the oxide film is copper oxide.

The array substrate provided by the embodiment of the present invention can further comprise:

an active layer electrically connected with the source electrode and the drain electrode and arranged below the source electrode and the drain electrode;

a gate electrode insulated with the active layer and arranged opposite the active layer.

Preferably, in the array substrate provided by the embodiment of the present invention, the thickness of the oxide film is 10 nm to 100 nm. In this way, the formed oxide film can protect the source electrode and the data line from being corroded by the etching agent; the normal transmission of the carrier between the source electrode and the drain electrode can also be ensured.

An embodiment of the present invention further provides a manufacturing method of an array substrate; the method comprises:

forming patterns of a source electrode, a drain electrode and a data line on an underlay substrate with a one-time composition process;

performing an annealing process to the underlay substrate, on which the patterns of the source electrode, the drain electrode and the data line are formed; forming an oxide film on the patterns of the source electrode, the drain electrode and the data line;

forming patterns of a pixel electrode and a connecting portion on the underlay substrate after the annealing process; wherein

the connecting portion electrically connects the drain electrode with the pixel electrode through a first via hole, which is arranged over the drain electrode and penetrates through the oxide film.

In the manufacturing method of an array substrate provided by the embodiment of the present invention, after forming patterns of a source electrode, a drain electrode and a data line on an underlay substrate with a one-time composition process, an annealing process is performed on the underlay substrate to form an oxide film on the patterns of the source electrode, the drain electrode and the data line, then the patterns of a pixel electrode and a connecting portion are formed; in this way, the oxide film can protect the source electrode and the data line under the oxide film from being corroded by an etching agent when the pattern of the pixel electrode is formed by etching, and the display quality of a display panel will not be affected; meanwhile, a connecting portion enables the drain electrode to be electrically connected with the pixel electrode through a first via hole arranged over the drain electrode and penetrating through the oxide film, therefore the normal display function of the display panel can be ensured.

In particular, in the manufacturing method provided by the embodiment of the invention, the step of forming a pattern of a pixel electrode on the underlay substrate comprises:

forming a pattern of a pixel electrode on the underlay substrate, the pattern of the pixel electrode does not mutually overlap with the patterns of the source electrode, the drain electrode and the data line;

when the array substrate manufactured with the manufacturing method provided by the embodiment of the present invention is applied in an advanced super dimensional field switch type liquid crystal display, the method further comprises:

forming a passivation layer film on the underlay substrate, on which underlay substrate the pattern of the pixel electrode is formed; forming a first via hole in the oxide film and the passivation layer film over the drain electrode with an etching process; forming a second via hole in the passivation layer film over the pixel electrode when the first via hole is formed;

forming mutually insulated patterns of a common electrode and a connecting portion on the pattern of the passivation layer; the connecting portion is electrically connected with the drain electrode through the first via hole, and is electrically connected with the pixel electrode through the second via hole.

Or, in particular, when the array substrate manufactured with the manufacturing method provided by the embodiment of the present invention is applied in an advanced super dimensional field switch type liquid crystal display, before the step of forming patterns of a pixel electrode and a connecting portion on the underlay substrate, the method further comprises:

forming a pattern of a common electrode on the underlay substrate, the pattern of the common electrode does not mutually overlap with the pattern of the drain electrode;

forming a passivation layer film on the underlay substrate, on which underlay substrate the pattern of the common electrode is formed; forming a first via hole in the oxide film and the passivation layer film over the drain electrode with an etching process.

In particular, the step of forming patterns of a pixel electrode and a connecting portion on the underlay substrate after the annealing process comprises:

forming electrically connected patterns of a pixel electrode and a connecting portion on the pattern of the passivation layer; the connecting portion is electrically connected with the drain electrode through the first via hole.

Preferably, to ensure a moderate thickness of the formed oxide film, in the manufacturing method provided by the embodiment of the invention, the step of performing an annealing process to the underlay substrate comprises:

performing a heating process to the underlay substrate in oxygen condition, the heating temperature is 150.degree. C. to 200.degree. C., the heating time is 10 min to 1 h.

Further, in the manufacturing method provided by the embodiment of the invention, before the step of forming patterns of a source electrode, a drain electrode and a data line on an underlay substrate, the method further comprises:

forming patterns of a gate electrode and a gate line on the underlay substrate with a one-time composition process;

forming a gate insulating layer on the underlay substrate with the patterns of the gate electrode and the gate line;

forming a pattern of an active layer on the gate insulating layer corresponding to the region of the gate electrode;

forming a pattern of an etching barrier layer on the underlay substrate with the pattern of the active layer.

An embodiment of the present invention further provides a display device comprising the array substrate according to the embodiments of the present invention.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1a-FIG. 1f are respectively structural schematic diagrams of the steps in a manufacturing method of an array substrate in the prior art;

FIG. 2 is a structural schematic diagram of the array substrate provided by an embodiment of the present invention, which array substrate is applied in a TN type liquid crystal display;

FIG. 3a and FIG. 3b are structural schematic diagrams of the array substrates provided by the embodiments of the present invention, which array substrates are applied in an ADS type liquid crystal display;

FIG. 4 is a flow diagram of the manufacturing method of an array substrate provided by the embodiment of the present invention;

FIG. 5a-FIG. 5c are respectively top views showing the formed products of the steps in a manufacturing method of an array substrate provided by the first embodiment of the present invention;

FIG. 6a and FIG. 6b are respectively side views showing the products corresponding to FIG. 5a and FIG. 5b;

FIG. 7a-FIG. 7c are respectively top views showing the formed products of the steps in a manufacturing method of an array substrate provided by the second embodiment of the present invention; and

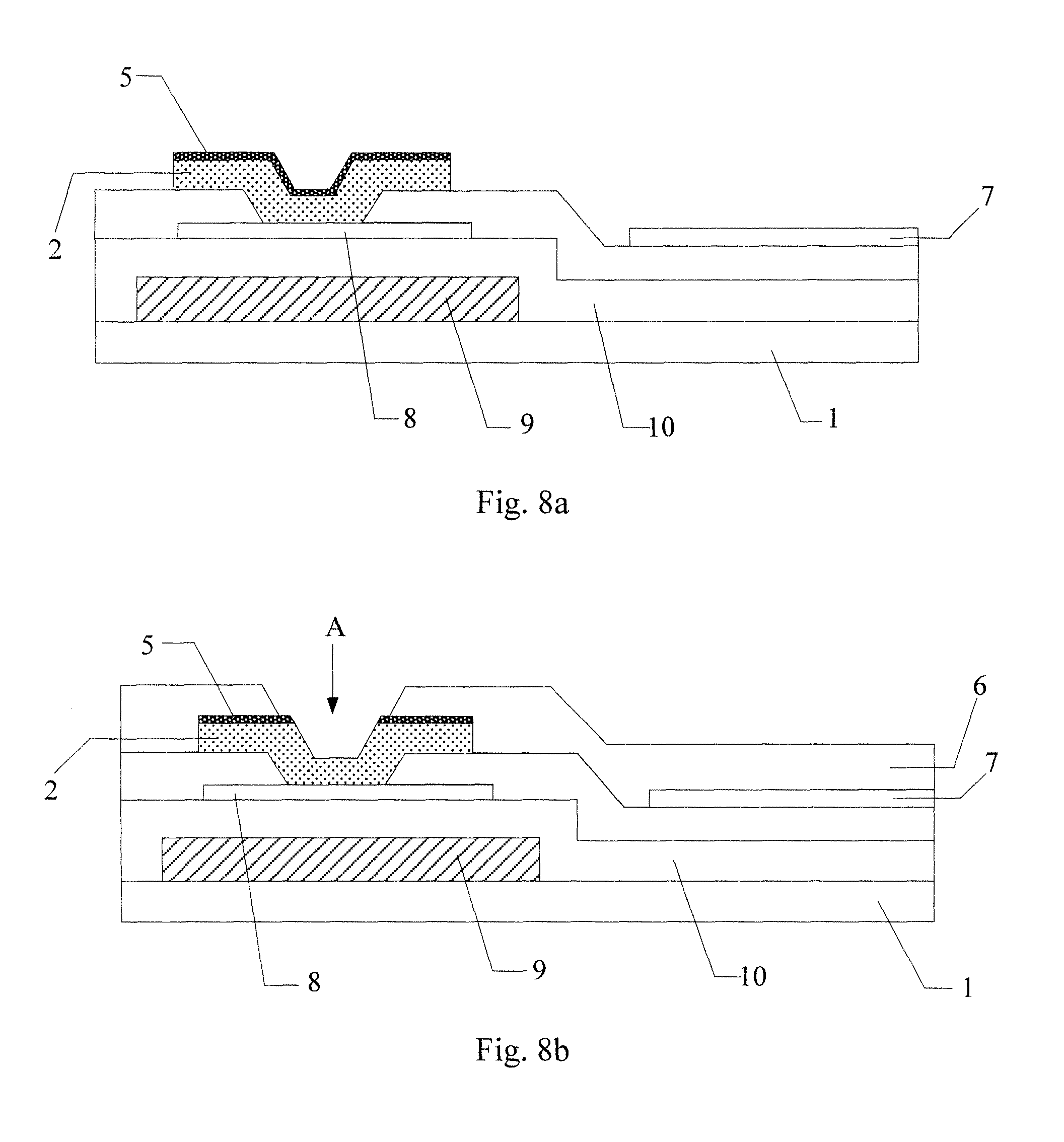

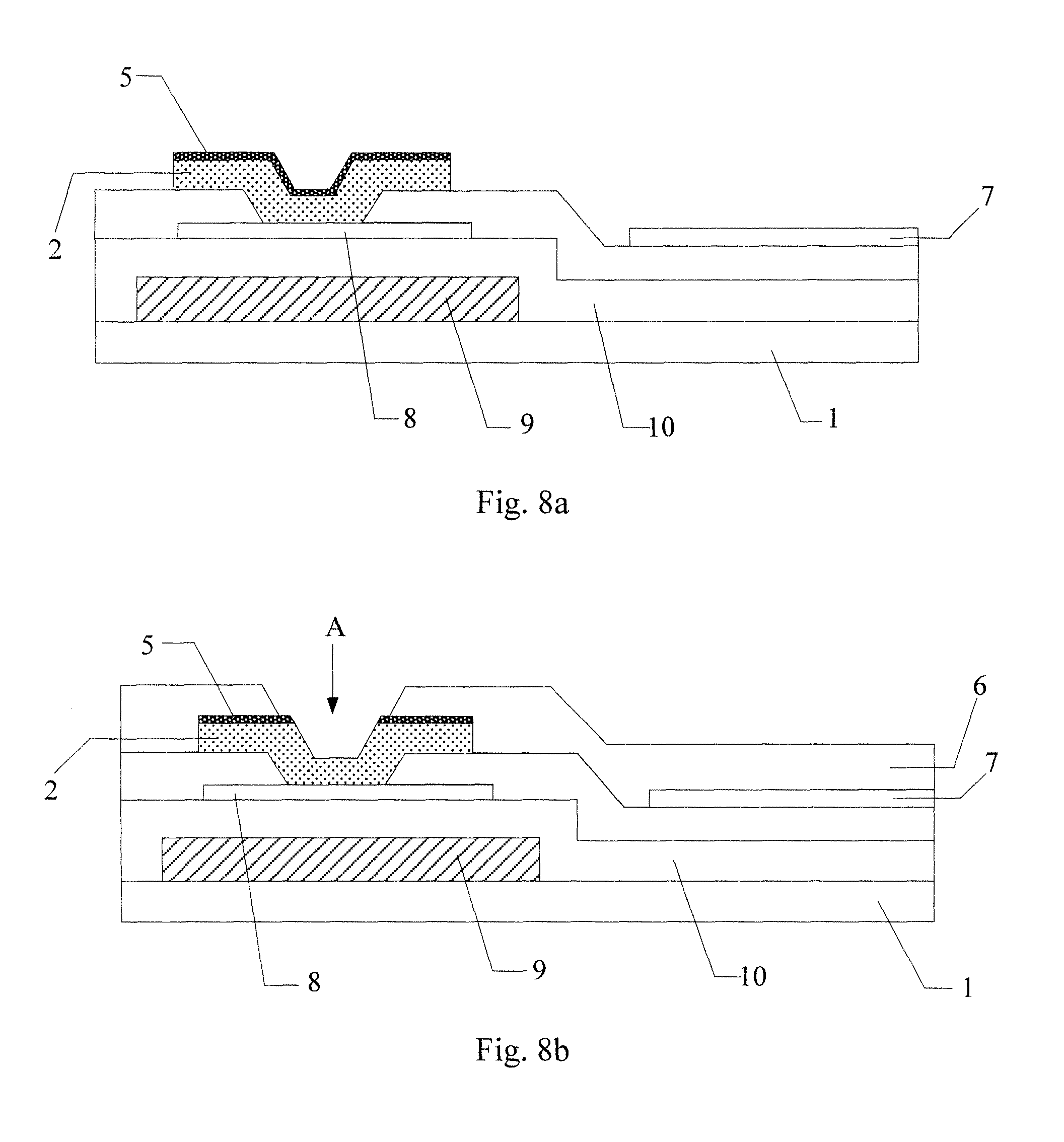

FIG. 8a and FIG. 8b are respectively side views showing the products corresponding to FIG. 7a and FIG. 7b.

DETAILED DESCRIPTION OF THE INVENTION

The present invention will be described below in more detail in combination with the drawings and the embodiments. The following embodiments are used for explanation of the present invention, not for limitation of the scope of the present invention.

In the drawings, the shape and thickness of each layer do not reflect the real scale of the array substrate, but illustrate the present invention.

As shown in FIG. 2, an embodiment of the present invention provides an array substrate, the array substrate comprises: an underlay substrate 1; a source electrode, a drain electrode 2 and a data line, which are arranged in the same layer on the underlay substrate 1; and a pixel electrode 3 arranged on the layer, in which the source electrode, the drain electrode 2 and the data line are arranged; the array substrate further comprises: a connecting portion 4;

an oxide film 5 which is formed on the surfaces of the source electrode, the drain electrode 2 and the data line after annealing treatment is conducted on the source electrode, the drain electrode 2 and the data line;

a first via hole A arranged over the drain electrode 2 and penetrating through the oxide film 5; the connecting portion 4 electrically connects the drain electrode 2 with the pixel electrode 3 through the first via hole A.

In the array substrate provided by the embodiment of the present invention, due to the fact that the surfaces of a source electrode, a drain electrode 2 and a data line which are arranged on the same layer are provided with an oxide film 5 which is formed after annealing treatment is conducted on the source electrode, the drain electrode 2 and the data line, in the process that the pattern of the pixel electrode 3 is formed on the source electrode, the drain electrode 2 and the data line by the adoption of a composition technology, the oxide film 5 can protect the source electrode and the data line under the oxide film 5 from being corroded by an etching agent when the pattern of the pixel electrode 3 is formed by etching, and the display quality of a display panel will not be affected; meanwhile, a connecting portion 4 enables the drain electrode 2 to be electrically connected with the pixel electrode 3 through a first via hole A arranged over the drain electrode 2 and penetrating through the oxide film 5, therefore the normal display function of the display panel can be ensured.

In particular, since the oxide film 5 is formed on the surfaces of the source electrode, the drain electrode 2 and the data line after annealing treatment is conducted on the source electrode, the drain electrode 2 and the data line, it is unnecessary to produce the oxide film 5 with a single composition process; compared with the prior art, during the actual manufacturing process of the array substrate provided by the embodiment of the present invention, the number of masks will not be increased.

In the specific implementation, the step of performing an annealing process to the underlay substrate 1 with the formed source electrode, the drain electrode 2 and the data line generally comprises: performing a heating process to the underlay substrate 1 with the formed source electrode, the drain electrode 2 and the data line in oxygen condition; the heating temperature is controlled in the range of 150.degree. C. to 200.degree. C., and the heating time is controlled in the range of 10 min to 1 h.

Preferably, in the array substrate provided by the embodiment of the present invention, the thickness of the oxide film 5 is controlled in the range of 10 nm to 100 nm. In this way, the formed oxide film 5 can protect the source electrode and the data line from being corroded by the etching agent; the normal transmission of the carrier between the source electrode and the drain electrode 2 can also be ensured.

Preferably, to decrease the resistance of the source electrode, the drain electrode 2 and the data line, generally the patterns of the source electrode, the drain electrode 2 and the data line is formed with metallic copper; after the annealing process, the oxide film formed on the surfaces of the source electrode, the drain electrode 2 and the data line is a film of copper oxide.

Certainly, in an implementation, other metal can also be applied to form the source electrode, the drain electrode 2 and the data line, which is not limited herein.

In an implementation, the array substrate provided by the embodiment of the present invention can be applied in a TN (Twisted Nematic) type liquid crystal display, as shown in FIG. 2; or, the array substrate provided by the embodiment of the present invention can also be applied in an ADS (Advanced Super Dimension Switch) type liquid crystal display, which is not limited herein.

When the array substrate provided by the embodiment of the present invention is applied in an ADS type liquid crystal display, as shown in FIG. 3a, the array substrate can further comprise: a passivation layer 6 and a common electrode 7 arranged sequentially over the pixel electrode 3; the passivation layer 6 extends over the drain electrode 2; the connecting portion 4 and the common electrode 7 are arranged in the same layer and are mutually insulated, and the first via hole A also penetrates through the passivation layer 6 (i.e., the first via hole A penetrates through the oxide film 5 and the passivation layer 6); patterns of the pixel electrode 3, the source electrode, the drain electrode 2 and the data line do not overlap mutually; a second via hole B arranged over the pixel electrode 3 and penetrating through the passivation layer 6, the connecting portion 4 is electrically connected with the pixel electrode 3 through the second via hole B. Moreover, the connecting portion 4 is electrically connected with the drain electrode 2 through the first via hole A, which is arranged over the drain electrode 2 and penetrating through the oxide film 5 and the passivation layer 6; in this way, the drain electrode 2 is electrically connected with the pixel electrode 3 by means of the connecting portion 4.

Or, when the array substrate provided by the embodiment of the present invention is applied in an ADS type liquid crystal display, as shown in FIG. 3b, the array substrate can further comprise: a common electrode 7 arranged between the pixel electrode 3 and the layer in which the source electrode, the drain electrode 2 and the data line are arranged; and a passivation layer 6 arranged between the pixel electrode 3 and the common electrode 7, the passivation layer 6 extends over the drain electrode 2; patterns of the common electrode 7 and the drain electrode 2 do not overlap mutually; the connecting portion 4 and the pixel electrode 3 are arranged in the same layer, and the first via hole A also penetrates through the passivation layer 6 (i.e., the first via hole A penetrates through the oxide film 5 and the passivation layer 6). The connecting portion 4 is electrically connected with the drain electrode 2 through the first via hole A, which is arranged over the drain electrode 2 and penetrating through the oxide film 5 and the passivation layer 6; in this way, the drain electrode 2 is electrically connected with the pixel electrode 3 by means of the connecting portion 4.

In an implementation of the array substrate provided by the embodiment of the invention, the thin film transistor in the array substrate can have a bottom gate structure, as shown in FIG. 2, FIG. 3a and FIG. 3b. The array substrate can further comprise: an active layer 8 electrically connected with the source electrode and the drain electrode 2 and arranged below the source electrode and the drain electrode 2; and a gate electrode 9 insulated with the active layer 8 and arranged opposite the active layer 8.

Certainly, the thin film transistor in the array substrate can have a top gate structure, i.e., the array substrate can then further comprise: an active layer 8 electrically connected with the source electrode and the drain electrode 2 and arranged over the source electrode and the drain electrode 2; and a gate electrode 9 insulated with the active layer 8 and arranged opposite the active layer 8, which is not limited herein.

Based on the same inventive concept, an embodiment of the present invention further provides a manufacturing method of an array substrate; as shown in FIG. 4, the method specifically comprises:

S401, forming patterns of a source electrode, a drain electrode and a data line on an underlay substrate with a one-time composition process;

in particular, to decrease the resistance of the source electrode, the drain electrode and the data line, generally the patterns of the source electrode, the drain electrode and the data line is formed with metallic copper by means of a one-time composition process. Certainly, other metal can also be applied to form the patterns of the source electrode, the drain electrode and the data line, which is not limited herein;

S402, performing an annealing process to the underlay substrate, on which the patterns of the source electrode, the drain electrode and the data line are formed; forming an oxide film on the patterns of the source electrode, the drain electrode and the data line;

in particular, since the oxide film is formed on the surfaces of the source electrode, the drain electrode and the data line after annealing treatment is conducted on the source electrode, the drain electrode and the data line, it is unnecessary to produce the oxide film with a single composition process; compared with the prior art, during the actual manufacturing process of the array substrate provided by the embodiment of the present invention, the number of masks will not be increased;

moreover, the oxide film is formed on the patterns of the source electrode, the drain electrode and the data line by performing an annealing process to the underlay substrate with the formed source electrode, the drain electrode and the data line in oxygen condition. For example, the source electrode, the drain electrode and the data line is made of metallic copper; after the annealing process, a film of copper oxide is formed on the surfaces of the source electrode, the drain electrode and the data line;

S403, forming patterns of a pixel electrode and a connecting portion on the underlay substrate after the annealing process; wherein

the connecting portion electrically connects the drain electrode with the pixel electrode through a first via hole, which is arranged over the drain electrode and penetrates through the oxide film.

In the manufacturing method of an array substrate provided by the embodiment of the present invention, after forming patterns of a source electrode, a drain electrode and a data line on an underlay substrate with a one-time composition process, an annealing process is performed on the underlay substrate to form an oxide film on the patterns of the source electrode, the drain electrode and the data line, then the patterns of a pixel electrode and a connecting portion are formed; in this way, the oxide film can protect the source electrode and the data line under the oxide film from being corroded by an etching agent when the pattern of the pixel electrode is formed by etching, and the display quality of a display panel will not be affected; meanwhile, a connecting portion enables the drain electrode to be electrically connected with the pixel electrode through a first via hole arranged over the drain electrode and penetrating through the oxide film, therefore the normal display function of the display panel can be ensured.

In particular, in the manufacturing method provided by the embodiment of the invention, the step S403 of forming a pattern of a pixel electrode on the underlay substrate can comprise:

forming a pattern of a pixel electrode on the underlay substrate, the pattern of the pixel electrode does not mutually overlap with the patterns of the source electrode, the drain electrode and the data line;

furthermore, when the array substrate manufactured with the manufacturing method provided by the embodiment of the present invention is applied in an ADS type liquid crystal display, the method can further comprise:

firstly, forming a passivation layer film on the underlay substrate, on which underlay substrate the pattern of the pixel electrode is formed; forming a first via hole in the oxide film and the passivation layer film over the drain electrode with an etching process; forming a second via hole in the passivation layer film over the pixel electrode when the first via hole is formed;

secondly, forming mutually insulated patterns of a common electrode and a connecting portion on the pattern of the passivation layer; the connecting portion is electrically connected with the drain electrode through the first via hole, and is electrically connected with the pixel electrode through the second via hole.

Or, when the array substrate manufactured with the manufacturing method provided by the embodiment of the present invention is applied in an ADS type liquid crystal display, before the step S403 of forming patterns of a pixel electrode and a connecting portion on the underlay substrate, the method can further comprise:

firstly, forming a pattern of a common electrode on the underlay substrate, the pattern of the common electrode does not mutually overlap with the pattern of the drain electrode;

secondly, forming a passivation layer film on the underlay substrate, on which underlay substrate the pattern of the common electrode is formed; forming a first via hole in the oxide film and the passivation layer film over the drain electrode with an etching process.

In particular, the step S403 of forming patterns of a pixel electrode and a connecting portion on the underlay substrate after the annealing process can comprise: forming electrically connected patterns of a pixel electrode and a connecting portion on the pattern of the passivation layer; the connecting portion is electrically connected with the drain electrode through the first via hole.

Preferably, to ensure a moderate thickness of the formed oxide film, in the manufacturing method provided by the embodiment of the invention, the step S402 of performing an annealing process to the underlay substrate can comprise: performing a heating process to the underlay substrate in oxygen condition, the heating temperature is controlled in the range of 150.degree. C. to 200.degree. C., the heating time is controlled in the range of 10 min to 1 h.

In an implementation, taking manufacturing an array substrate having a thin film transistor with a bottom gate structure for example, in the manufacturing method provided by the embodiment of the invention, before the step S401 of forming patterns of a source electrode, a drain electrode and a data line on an underlay substrate, the method can further comprise:

firstly, forming patterns of a gate electrode and a gate line on the underlay substrate with a one-time composition process;

secondly, forming a gate insulating layer on the underlay substrate with the patterns of the gate electrode and the gate line;

then, forming a pattern of an active layer on the gate insulating layer corresponding to the region of the gate electrode;

finally, forming a pattern of an etching barrier layer on the underlay substrate with the pattern of the active layer.

The implementations of above mentioned two structures (i.e., the connecting portion and the common electrode being arranged in the same layer; or the connecting portion and the pixel electrode being arranged in the same layer) of the array substrates are respectively illustrated with two examples, in which the array substrates are applied in the ADS type liquid crystal display.

Example one: a manufacturing method of an array substrate in which the connecting portion and the common electrode is arranged in the same layer can specifically comprise:

1. forming patterns of a gate electrode, a gate line on an underlay substrate with a one-time composition process;

2. forming a gate insulating layer on the underlay substrate with the patterns of the gate electrode and the gate line;

3. forming a pattern of an active layer on the gate insulating layer corresponding to the region of the gate electrode;

4. forming a pattern of an etching barrier layer on the underlay substrate with the pattern of the active layer;

5. forming patterns of a source electrode, a drain electrode and a data line on an underlay substrate with a one-time composition process;

the above mentioned steps 1-5 are not improved by the manufacturing method of an array substrate provided by the embodiment of the present invention; the embodiments of the above mentioned steps 1-5 are same with the prior art, which will not be repeated herein;

6. performing an annealing process to the underlay substrate, on which the patterns of the source electrode, the drain electrode and the data line are formed; forming an oxide film on the patterns of the source electrode, the drain electrode and the data line;

7. forming a pattern of a pixel electrode 3 on the underlay substrate 1, the pattern of the pixel electrode 3 does not mutually overlap with the patterns of the source electrode (not shown in FIG. 6a), the drain electrode 2 and the data line 12 (not shown in FIG. 6a), as shown in FIG. 5a and FIG. 6a;

8. forming a passivation layer 6 (not shown in FIG. 5b) film on the underlay substrate 1, on which underlay substrate the pattern of the pixel electrode 3 is formed; forming a first via hole A in the oxide film 5 (not shown in FIG. 5b) and the passivation layer 6 film over the drain electrode 2 with an etching process; forming a second via hole B in the passivation layer 6 film over the pixel electrode 3 when the first via hole is formed, as shown in FIG. 5b and FIG. 6b;

9. forming mutually insulated patterns of a common electrode 7 and a connecting portion 4 on the pattern of the passivation layer 6 (not shown in FIG. 5c); the connecting portion 4 is electrically connected with the drain electrode 2 through the first via hole A, and is electrically connected with the pixel electrode 3 through the second via hole B, as shown in FIG. 5c and FIG. 3a.

Example two: a manufacturing method of an array substrate in which the connecting portion and the pixel electrode is arranged in the same layer can specifically comprise:

1. forming patterns of a gate electrode, a gate line on an underlay substrate with a one-time composition process;

2. forming a gate insulating layer on the underlay substrate with the patterns of the gate electrode and the gate line;

3. forming a pattern of an active layer on the gate insulating layer corresponding to the region of the gate electrode;

4. forming a pattern of an etching barrier layer on the underlay substrate with the pattern of the active layer;

5. forming patterns of a source electrode, a drain electrode and a data line on an underlay substrate with a one-time composition process;

the above mentioned steps 1-5 are not improved by the manufacturing method of an array substrate provided by the embodiment of the present invention; the embodiments of the above mentioned steps 1-5 are same with the prior art, which will not be repeated herein;

6. performing an annealing process to the underlay substrate, on which the patterns of the source electrode, the drain electrode and the data line are formed; forming an oxide film on the patterns of the source electrode, the drain electrode and the data line;

7. forming a pattern of a common electrode 7 on the underlay substrate 1, the pattern of the common electrode 7 does not mutually overlap with the patterns of the source electrode 11 (not shown in FIG. 8a), the drain electrode 2 and the data line 12 (not shown in FIG. 8a), as shown in FIG. 7a and FIG. 8a;

8. forming a passivation layer 6 (not shown in FIG. 7b) film on the underlay substrate 1, on which underlay substrate the pattern of the common electrode 7 is formed; forming a first via hole A in the oxide film 5 (not shown in FIG. 7b) and the passivation layer 6 film over the drain electrode 2 with an etching process, as shown in FIG. 7b and FIG. 8b;

9. forming electrically connected patterns of a pixel electrode 3 and a connecting portion 4 on the pattern of the passivation layer 6 (not shown in FIG. 7c); the connecting portion 4 is electrically connected with the drain electrode 2 through the first via hole A, as shown in FIG. 7c and FIG. 3b.

Based on the same inventive concept, an embodiment of the present invention also provides a display device, which comprises the array substrate according to the embodiment of the present invention. The display device can be any product or component with display function, such as mobile phone, tablet computer, TV, monitor, notebook computer, digital photo frame, navigator. The implementation of the display device can refer to the embodiments of the array substrate, and will not be repeated herein.

The embodiments of the invention disclose an array substrate, a manufacturing method thereof and a display device. Due to the fact that the surfaces of a source electrode, a drain electrode and a data line which are arranged on the same layer are provided with an oxide film which is formed after annealing treatment is conducted on the source electrode, the drain electrode and the data line, in the process that the pattern of a pixel electrode is formed on the source electrode, the drain electrode and the data line by the adoption of a composition technology, the oxide film can protect the source electrode and the data line under the oxide film from being corroded by an etching agent when the pattern of the pixel electrode is formed by etching, and the display quality of a display panel will not be affected; meanwhile, a connecting portion enables the drain electrode to be electrically connected with the pixel electrode through a first via hole arranged over the drain electrode and penetrating through the oxide film, therefore the normal display function of the display panel can be ensured.

Apparently, the person skilled in the art may make various alterations and variations to the invention without departing the spirit and scope of the invention. As such, provided that these modifications and variations of the invention pertain to the scope of the claims of the invention and their equivalents, the invention is intended to embrace these alterations and variations.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.