# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2020/0258761 A1 Pearson et al.

# Aug. 13, 2020 (43) **Pub. Date:**

## (54) PRINTING COMPONENT ARRAYS WITH DIFFERENT ORIENTATIONS

(71) Applicant: **X-Celeprint Limited**, Cork (IE)

(72) Inventors: Andrew Tyler Pearson, Durham, NC (US); Erich Radauscher, Raleigh, NC

(US); Christopher Michael Verreen, Raleigh, NC (US); Matthew Alexander Meitl, Durham, NC (US); Christopher Andrew Bower, Raleigh, NC (US); Ronald S. Cok, Rochester, NY (US)

(21) Appl. No.: 16/274,969

(22) Filed: Feb. 13, 2019

### **Publication Classification**

(51) Int. Cl. (2006.01)H01L 21/67 (2006.01)H01L 25/075 H01L 33/62 (2006.01)B65G 47/90 (2006.01)B41F 16/00 (2006.01)

### (52) U.S. Cl.

CPC .... H01L 21/67144 (2013.01); H01L 25/0753 (2013.01); H01L 2933/0066 (2013.01); B65G 47/90 (2013.01); B41F 16/006 (2013.01); H01L 33/62 (2013.01)

### (57)ABSTRACT

A method of micro-transfer printing comprises providing a component source wafer and components disposed in, on, or over the component source wafer. A destination substrate and a stamp for transferring the components from the component source wafer to the destination substrate is provided. The component source wafer has an attribute or structure that varies across the component source wafer that affects the structure, operation, appearance, or performance of the components. A first array of components is transferred from the component source wafer to the destination substrate with a first orientation. A second array of components is transferred from the component source wafer to the destination substrate with a second orientation different from the first orientation. Components can be transferred by micro-transfer printing and different orientations can be a different rotation, overlap, interlacing, or offset.

FIG. 13A

# FIG. 15A

2

\*\*4

7

40

N

**S**

ST

3

4

ST

ω)

ന

# PRINTING COMPONENT ARRAYS WITH DIFFERENT ORIENTATIONS

## TECHNICAL FIELD

[0001] The present disclosure relates generally to structures and methods for transferring (e.g., micro-transfer printing) multiple arrays of micro-components onto a substrate.

#### BACKGROUND

[0002] Substrates with electronically active components distributed over the extent of the substrate may be used in a variety of electronic systems, for example, in flat-panel display devices such as flat-panel liquid crystal or organic light emitting diode (OLED) displays, in imaging sensors, and in flat-panel solar cells. The electronically active components are typically either assembled on the substrate, for example using individually packaged surface-mount integrated-circuit devices and pick-and-place tools, or by sputtering or spin coating a layer of semiconductor material on the substrate and then photolithographically processing the semiconductor material to form thin-film circuits on the substrate. Individually packaged integrated-circuit devices typically have smaller transistors with higher performance than thin-film circuits but the packages are larger than can be desired for highly integrated systems.

[0003] Methods for transferring active components from one substrate to another are described in U.S. Pat. No. 7,943,491. In examples of these approaches, small integrated circuits are formed on a native semiconductor source wafer. The small unpackaged integrated circuits, or chiplets, are released from the native source wafer by etching a layer formed beneath the circuits. A PDMS stamp is pressed against the native source wafer and the process side of the chiplets is adhered to individual stamp posts. The chiplets are pressed against a destination substrate or backplane with the stamp and adhered to the destination substrate. In other examples, U.S. Pat. No. 8,722,458 entitled Optical Systems Fabricated by Printing-Based Assembly teaches transferring light-emitting, light-sensing, or light-collecting semiconductor elements from a wafer substrate to a destination substrate or backplane.

[0004] In order to populate a large destination substrate with components from a native source wafer, the stamp repeatedly picks up components from different locations on the native source wafer with stamp posts and prints the components to different locations on the destination substrate. The arrangement of components on the destination substrate is at least partly defined by the arrangement of the components on the native source wafer and the arrangement of posts on the stamp. The location of the stamp with respect to the native source wafer and the destination substrate is controlled by an opto-electro-mechanical control system.

### SUMMARY

[0005] It has been found that because of variation in materials and photolithographic processes on the native source wafer, the performance or other attributes of components formed on a native source wafer can also vary. This variation in source materials can cause operational non-uniformities in components transferred to the destination substrate. There is a need, therefore, for systems, structures, devices, materials, and methods that reduce variability in arrangements of multiple arrays of micro-transfer-printed

micro-components on destination substrates. The present disclosure provides, inter alfa, structures, materials, and methods that provide reduced large-scale component variation on a substrate.

[0006] In accordance with certain embodiments of the present disclosure, a method of micro-transfer printing comprises providing a component source wafer and components disposed in, on, or over the component source wafer, providing a destination substrate, and providing a stamp for transferring the components from the component source wafer to the destination substrate, wherein the component source wafer has an attribute or structure that varies across the component source wafer such that different ones of the components in different locations have a different structure, operation, appearance, or performance of the components, transferring a first array of components from the component source wafer to the destination substrate with a first orientation, and transferring a second array of components from the component source wafer to the destination substrate with a second orientation, wherein the second orientation is different from the first orientation.

[0007] In some embodiments, methods of the present invention comprise transferring the first array and transferring the second array with micro-transfer printing (e.g., dry contact printing).

**[0008]** In some embodiments of the present invention, the second orientation is rotated relative to the first array to provide different first and second orientations. The second orientation can be rotated 90 degrees, 180 degrees, or 270 degrees with respect to the first orientation.

[0009] In some embodiments, methods of the present invention comprise transferring the second array of components adjacent to the first array of components on the destination substrate. In some embodiments, methods of the present invention comprise repeatedly transferring arrays of components from the component source wafer to the destination substrate with adjacent arrays on the destination substrate transferred at different orientations. In some embodiments, methods of the present invention comprise repeatedly transferring arrays of components from the component source wafer to the destination substrate N times in one dimension, where N/2 pairs of adjacent arrays on the destination substrate comprise array i and array (N-1-i) for each i from 0 to (N/2)-1. In some embodiments, methods of the present invention comprise repeatedly transferring arrays of components from the component source wafer to the destination substrate N×M times in two dimensions, where N/2×M/2 two-by-two adjacent component arrays on the destination substrate comprise array (i, j), array (N-1-i, j), array (i, M-1-i), and array (N-1-i, M-1-i) for each i from 0 to (N/2)-1 and each j from 0 to (M/2)-1.

[0010] In some embodiments, methods of the present invention comprise interlacing the second array with respect to the first array in at least one dimension to provide different first and second orientations. The interlacing can be in one dimension or in two dimensions. The first array and the second array can each be regular, arrangements of components in one dimension or regular arrangements of components in two dimensions.

[0011] In some embodiments, methods of the present invention comprise offsetting the second array with respect to the first array on the destination substrate by an amount that is different from an offset of the first array with respect to the second array on the component source wafer to

provide different first and second orientations. The second array can be disposed with respect to the first array on the destination substrate in a different direction than the second array is disposed with respect to the first array on the component source wafer. The first array and second array can be adjacent on the component source wafer before transferring but not adjacent on the destination substrate after transferring.

[0012] In some embodiments, methods of the present invention comprise providing a plurality of component source wafers, wherein the plurality of component source wafers comprises the component source wafer, and transferring arrays of components from each of the component source wafers onto the destination substrate with two or more different orientations.

[0013] In some embodiments of the present invention, the plurality of component source wafers comprises a first component source wafer and a second component source wafer different from the first component source wafer, and some methods of the present invention comprise interlacing components from the first component source wafer between components from the second component source wafer.

[0014] In some embodiments of the present invention, the components are light-emitting components such as inorganic light-emitting diodes.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0015] The foregoing and other objects, aspects, features, and advantages of the present disclosure will become more apparent and better understood by referring to the following description taken in conjunction with the accompanying drawings, in which:

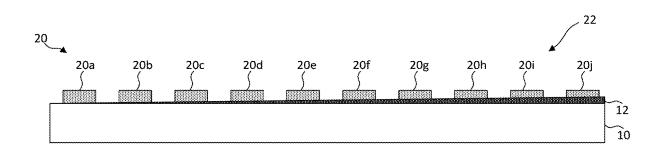

[0016] FIG. 1 is a schematic cross section of a native source wafer comprising an array of components useful in understanding embodiments of the present disclosure;

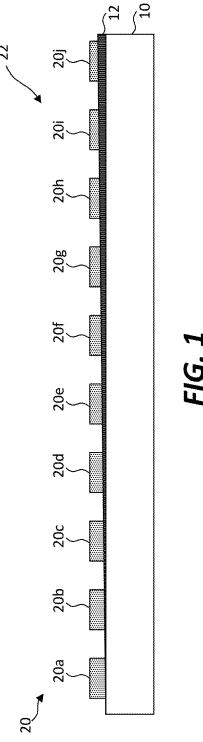

[0017] FIG. 2 is a schematic plan view of a native source wafer comprising an array of components having a common variable attribute that varies in one dimension across the array useful in understanding embodiments of the present disclosure;

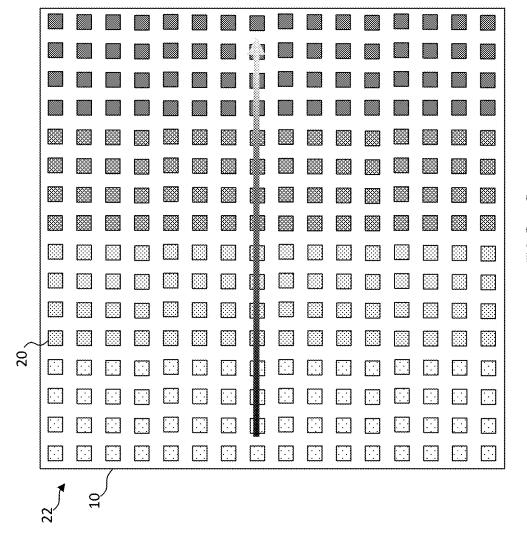

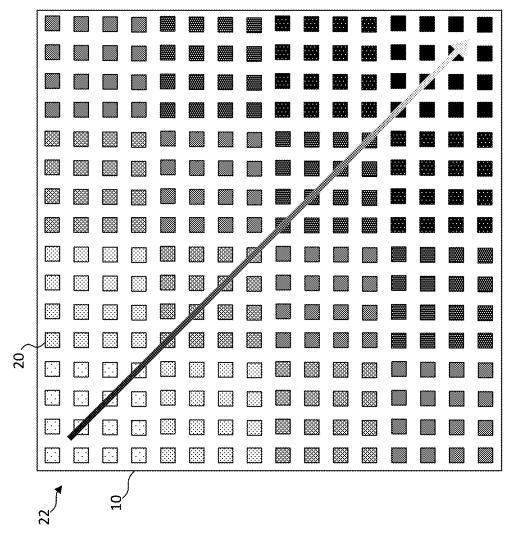

[0018] FIG. 3 is a schematic plan view of a native source wafer comprising an array of components having a common variable attribute that varies in two dimensions across the array useful in understanding embodiments of the present disclosure;

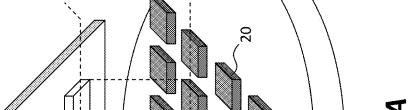

[0019] FIG. 4A is a perspective and FIG. 4B is a schematic cross section taken along cross section line A of FIG. 4A of a stamp and component source wafer according to illustrative embodiments of the present disclosure;

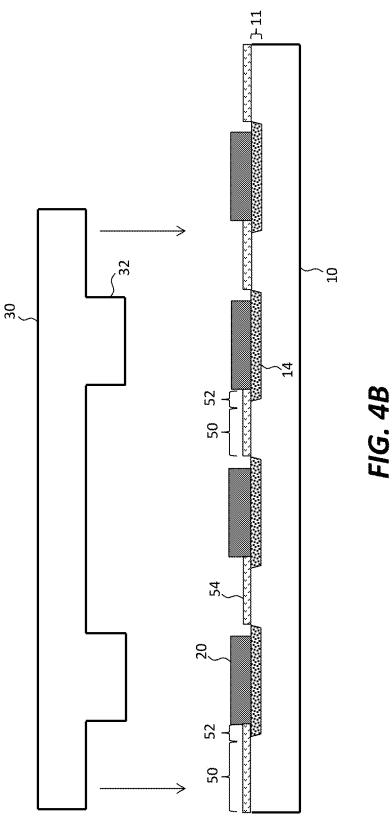

[0020] FIG. 5 is a schematic cross section of the stamp in contact with a first subset of components on the component source wafer according to illustrative embodiments of the present disclosure;

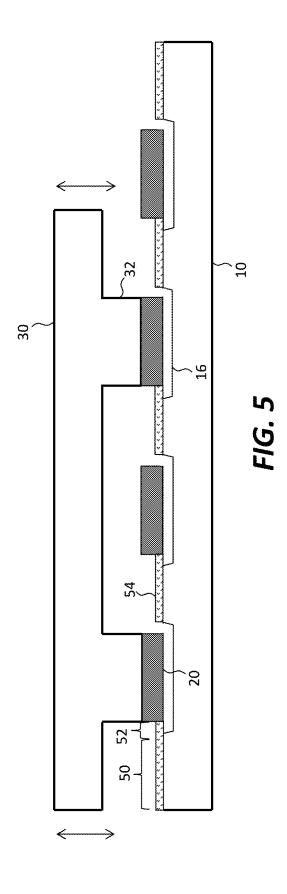

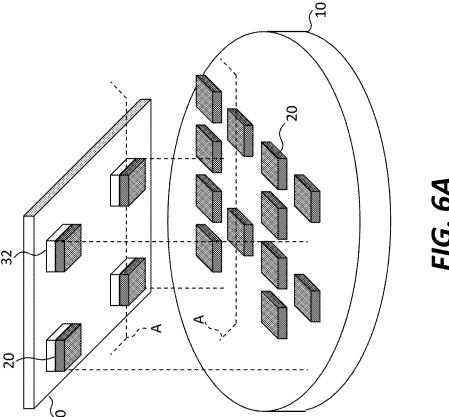

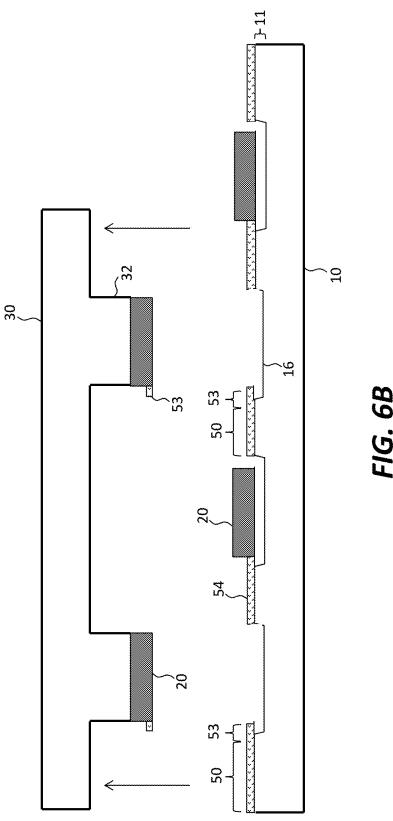

[0021] FIG. 6A is a perspective and FIG. 6B is a schematic cross section taken along cross section line A of FIG. 6A of the stamp with the first subset of components removed from the component source wafer according to illustrative embodiments of the present disclosure;

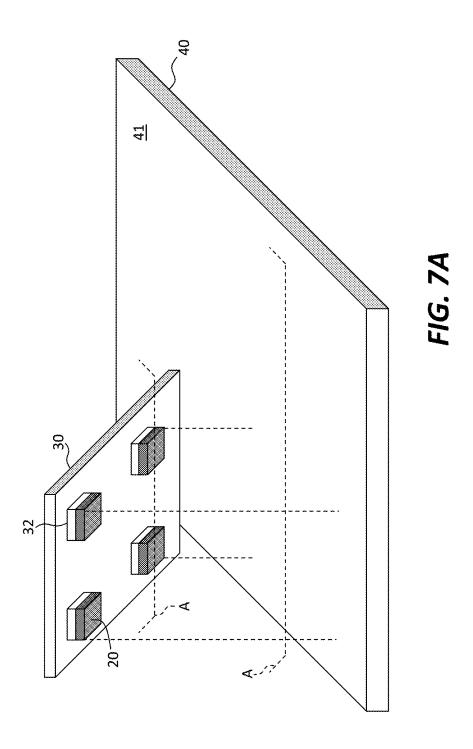

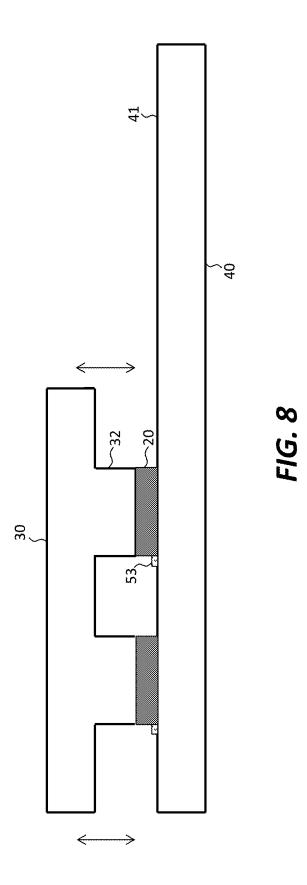

[0022] FIG. 7A is a perspective and FIG. 7B is a schematic cross section taken along cross section line A of FIG. 7A of the stamp before micro-transfer printing the first subset of components from the stamp to a destination substrate according to illustrative embodiments of the present disclosure:

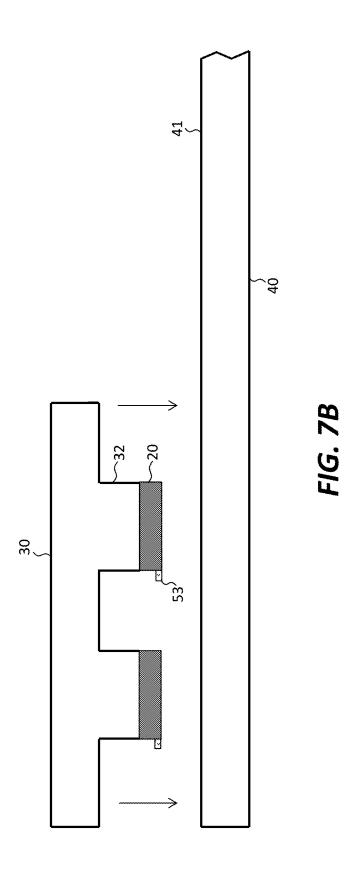

[0023] FIG. 8 is a schematic cross section of the stamp micro-transfer printing the first subset of components to the destination substrate according to illustrative embodiments of the present disclosure;

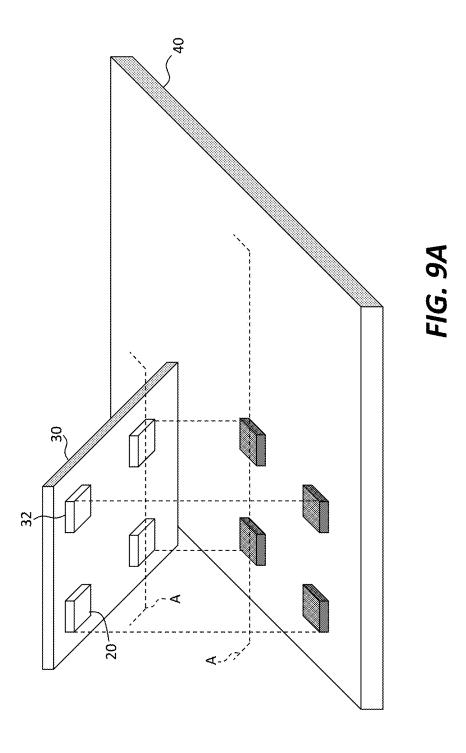

[0024] FIG. 9A is a perspective and FIG. 9B is a schematic cross section taken along cross section line A of FIG. 9A of the stamp and destination substrate after micro-transfer printing the first subset of components from the stamp to the destination substrate according to illustrative embodiments of the present disclosure;

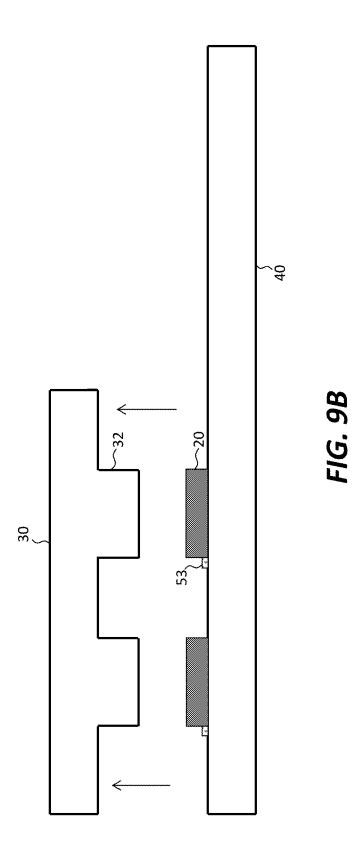

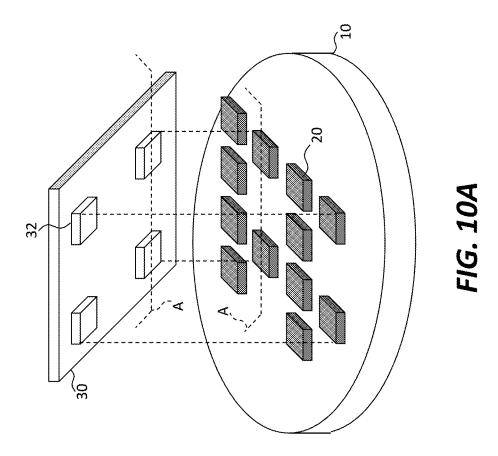

[0025] FIG. 10A is a perspective and FIG. 10B is a schematic cross section taken along cross section line A of FIG. 10A of the stamp and component source wafer before picking up a second subset of components with the stamp according to illustrative embodiments of the present disclosure:

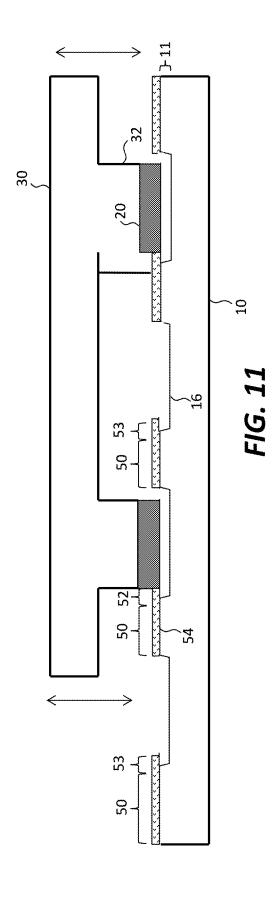

[0026] FIG. 11 is a schematic cross section of the stamp in contact with the second subset of components on the component source wafer according to illustrative embodiments of the present disclosure;

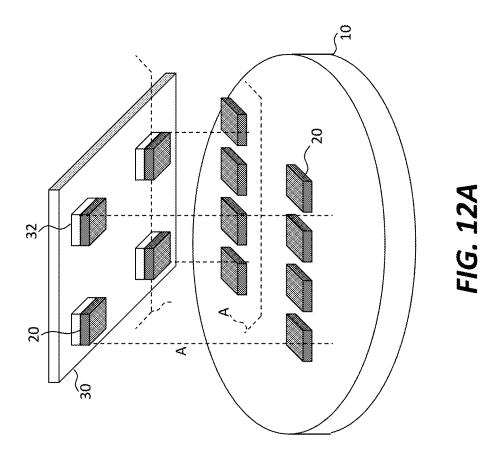

[0027] FIG. 12A is a perspective and FIG. 12B is a schematic cross section taken along cross section line A of FIG. 12A of the stamp with the second subset of components removed from the component source wafer according to illustrative embodiments of the present disclosure;

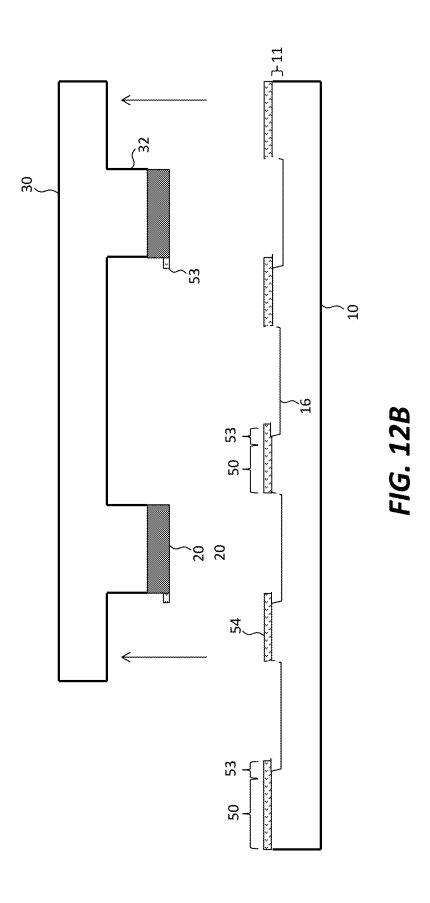

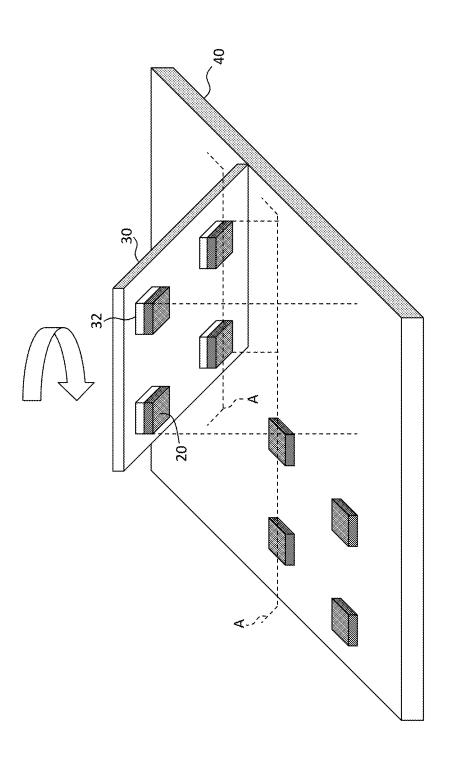

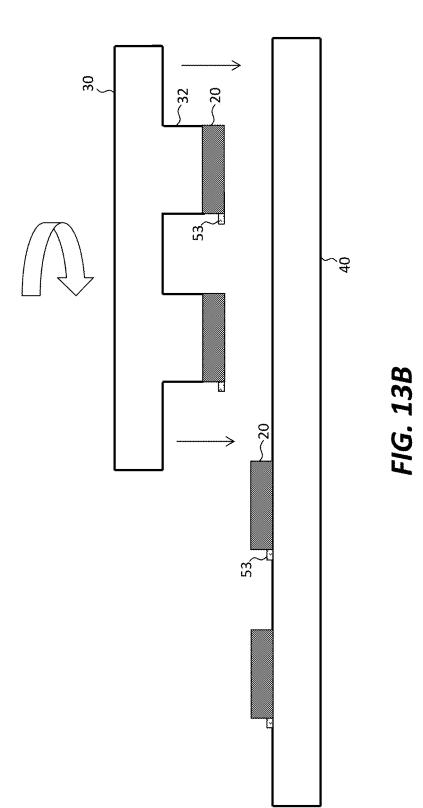

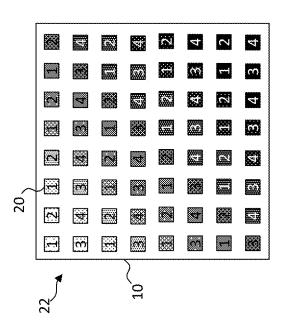

[0028] FIG. 13A is a perspective and FIG. 13B is a schematic cross section taken along cross section line A of FIG. 13A of the stamp before micro-transfer printing the second subset of components from the stamp to the destination substrate in a rotated configuration according to illustrative embodiments of the present disclosure;

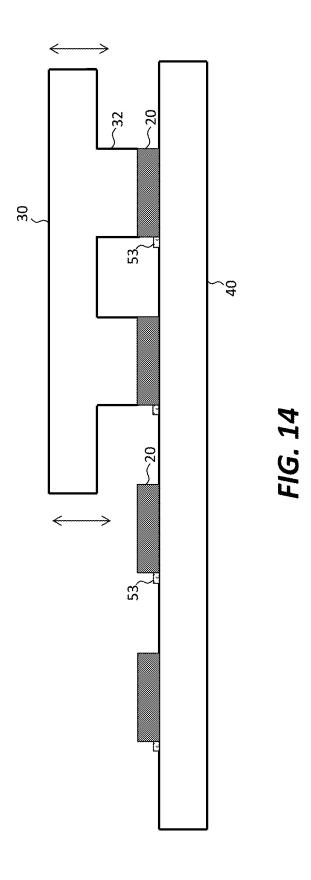

[0029] FIG. 14 is a cross section of the stamp microtransfer printing the second subset of components to the destination substrate in a rotated configuration according to illustrative embodiments of the present disclosure;

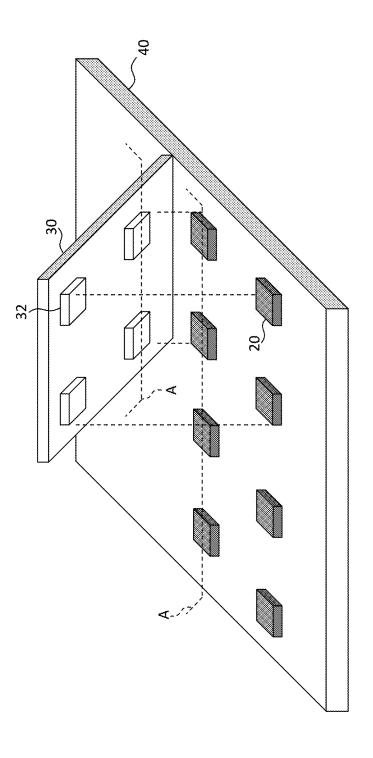

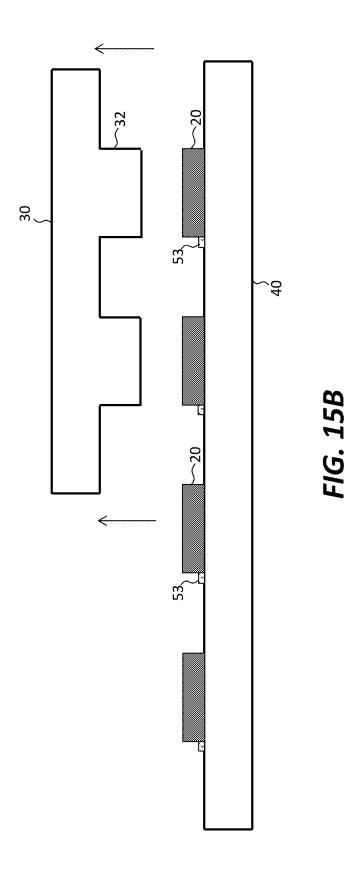

[0030] FIG. 15A is a perspective and FIG. 15B is a cross section taken along cross section line A of FIG. 15A of the stamp and destination substrate after micro-transfer printing the second subset of components from the stamp to the destination substrate in a rotated configuration according to illustrative embodiments of the present disclosure;

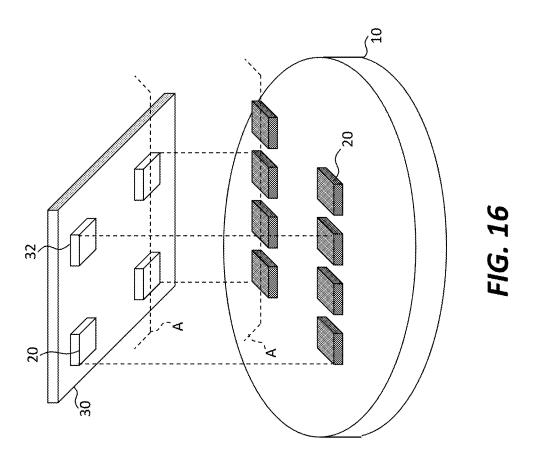

[0031] FIG. 16 is a perspective of the stamp and component source wafer before picking up a third subset of components with the stamp according to illustrative embodiments of the present disclosure;

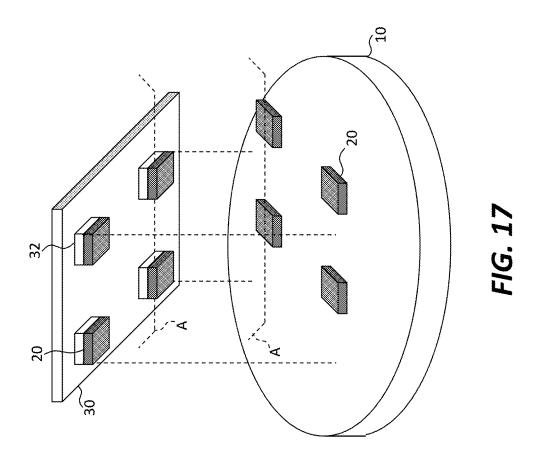

[0032] FIG. 17 is a perspective of the stamp with the third subset of components removed from the component source wafer according to illustrative embodiments of the present disclosure:

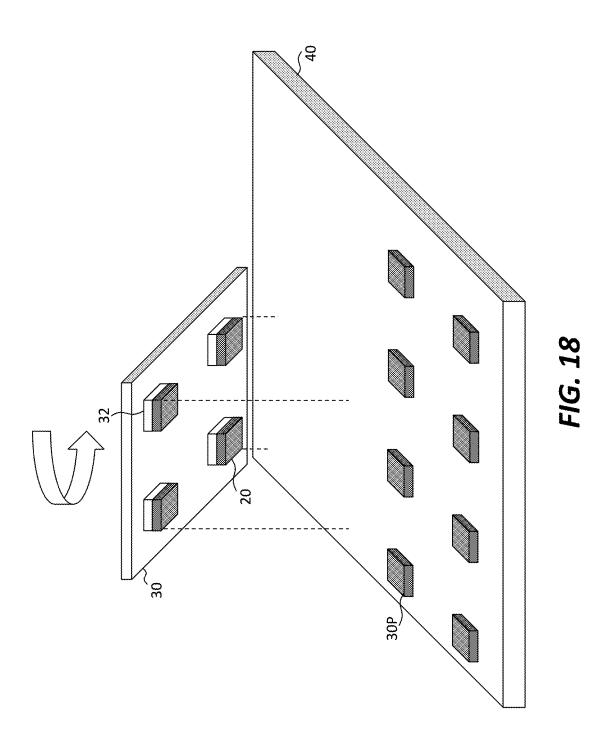

[0033] FIG. 18 is a perspective of the stamp before microtransfer printing the third subset of components from the stamp to the destination substrate in a rotated configuration according to illustrative embodiments of the present disclosure:

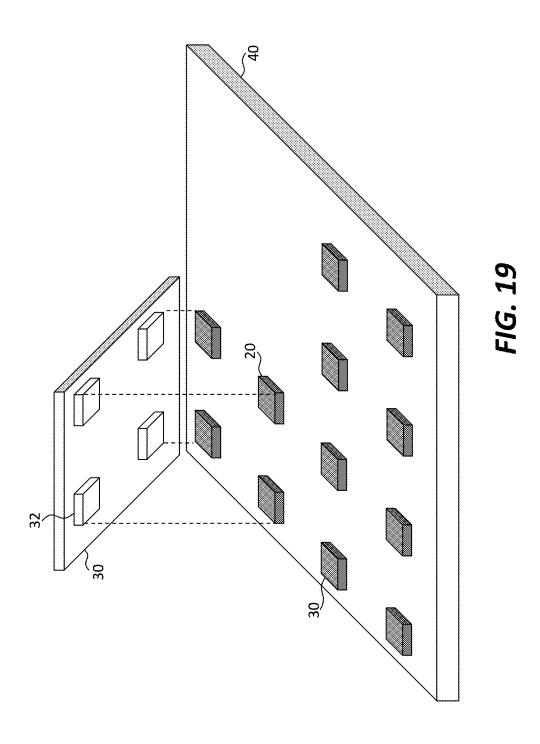

[0034] FIG. 19 is a perspective of the stamp after microtransfer printing the third subset of components from the stamp to the destination substrate in a rotated configuration according to illustrative embodiments of the present disclosure:

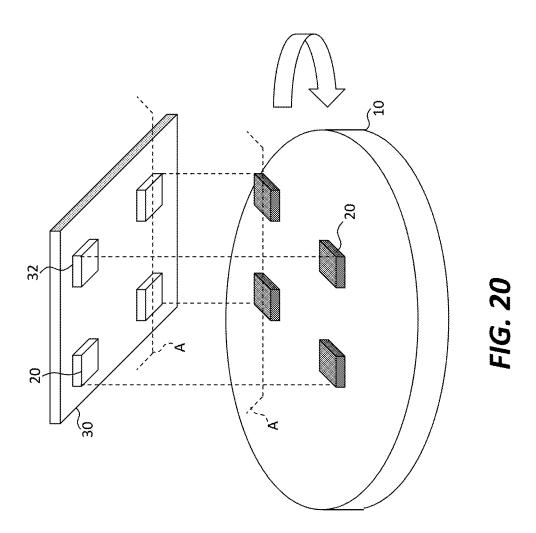

[0035] FIG. 20 is a perspective of the stamp and component source wafer in a rotated configuration before microtransfer printing a fourth subset of components according to illustrative embodiments of the present disclosure;

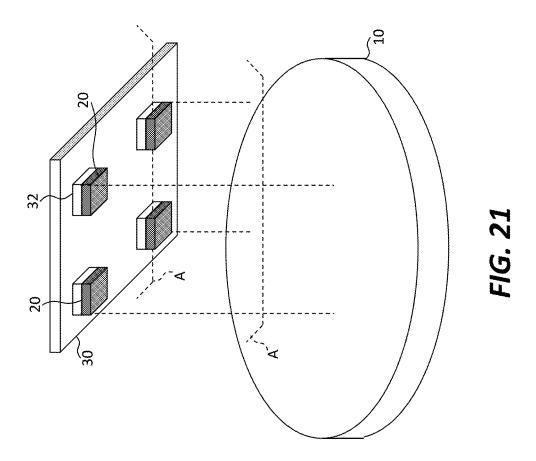

[0036] FIG. 21 is a perspective of the stamp with the fourth subset of components removed from the component source wafer according to illustrative embodiments of the present disclosure;

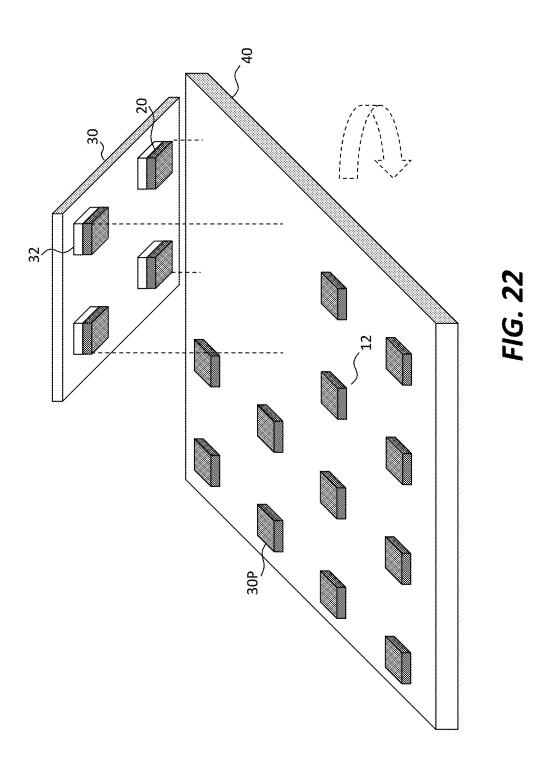

[0037] FIG. 22 is a perspective of the stamp before microtransfer printing the fourth subset of components from the stamp to the destination substrate in a rotated configuration according to illustrative embodiments of the present disclosure:

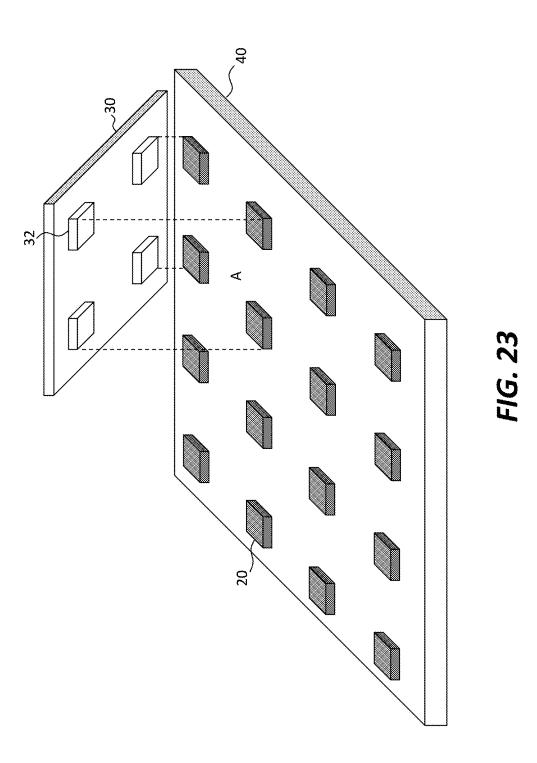

[0038] FIG. 23 is a perspective of the stamp after microtransfer printing the fourth subset of components from the stamp to the destination substrate in a rotated configuration according to illustrative embodiments of the present disclosure;

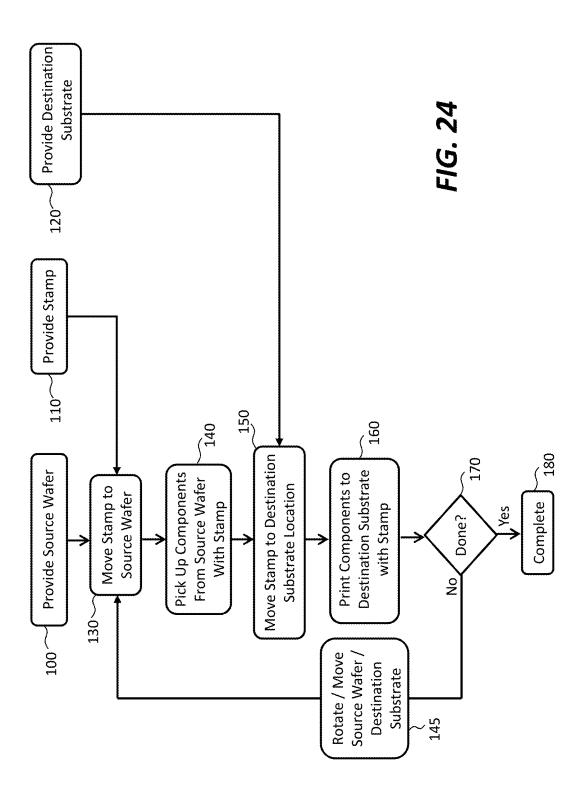

[0039] FIG. 24 is a flow diagram according to illustrative embodiments of the present disclosure;

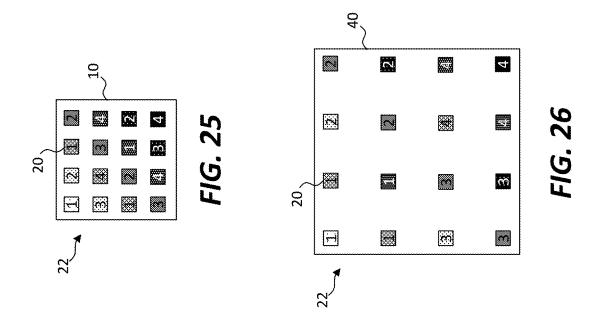

[0040] FIG. 25 is a plan view of a native source substrate with components labeled according to a stamp pick-up method useful in understanding embodiments of the present disclosure;

[0041] FIG. 26 is a plan view of a destination substrate with components printed according to the native source substrate and stamp pick-up method of FIG. 24 useful in understanding embodiments of the present disclosure;

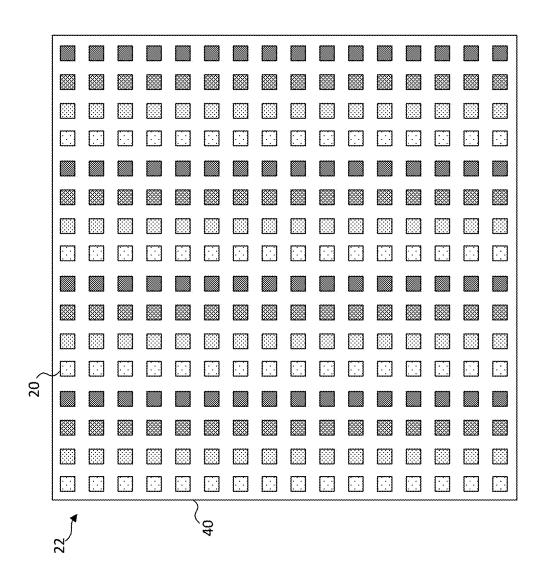

[0042] FIG. 27 is a plan view of a destination substrate with printed components from a native source substrate corresponding to FIG. 2 useful in understanding embodiments of the present disclosure;

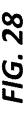

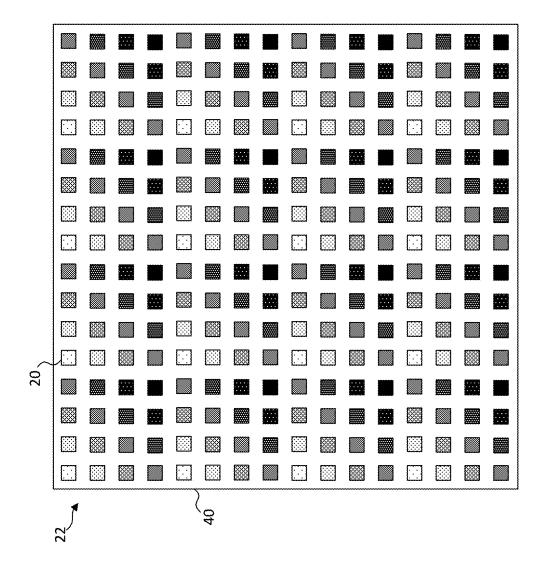

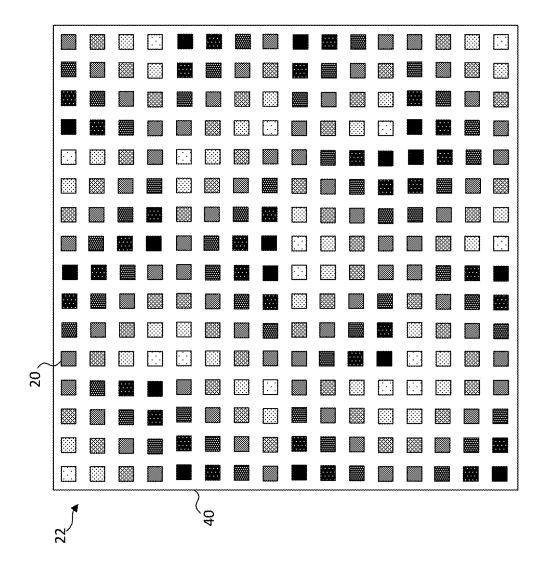

[0043] FIG. 28 is a plan view of a destination substrate with printed components from a native source substrate corresponding to FIG. 3 useful in understanding embodiments of the present disclosure;

[0044] FIG. 29 is a micrograph of a destination substrate with printed components from a native source substrate corresponding to FIG. 3 in operation useful in understanding embodiments of the present disclosure;

[0045] FIG. 30 is a plan view of a native source substrate with an 8×8 array of components labeled according to a stamp pick-up method useful in understanding embodiments of the present disclosure;

[0046] FIG. 31 is a plan view of a destination substrate with printed components from the native source substrate corresponding to FIG. 30 useful in understanding embodiments of the present disclosure;

[0047] FIG. 32 is a plan view of a native source substrate with an 8×8 array of components labeled according to a stamp pick-up method according to illustrative embodiments of the present disclosure;

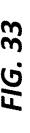

[0048] FIG. 33 is a plan view of a native source substrate with an 8×8 array of components labeled according to a stamp pick-up method according to illustrative embodiments of the present disclosure;

[0049] FIG. 34 is a plan view of a native source substrate with an 8×8 array of components labeled according to a stamp pick-up method according to illustrative embodiments of the present disclosure;

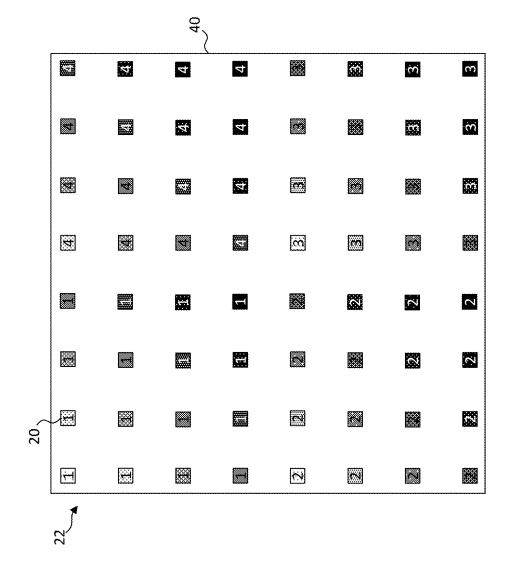

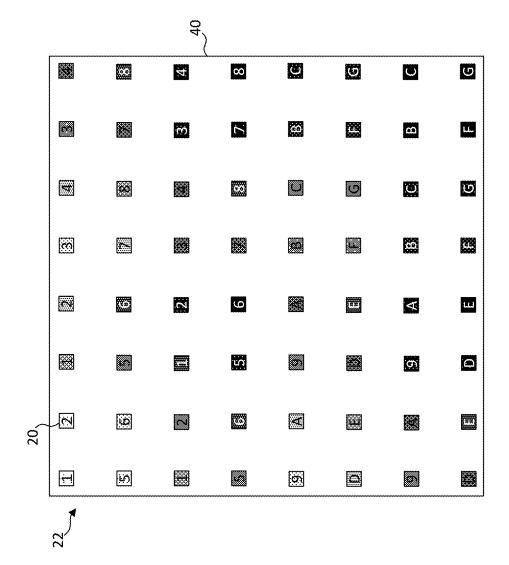

[0050] FIG. 35 is a plan view of a destination substrate with printed components from the native source substrate corresponding to FIG. 32 according to illustrative embodiments of the present disclosure;

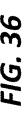

[0051] FIG. 36 is a plan view of a destination substrate with printed components from the native source substrate corresponding to FIG. 32 according to illustrative embodiments of the present disclosure;

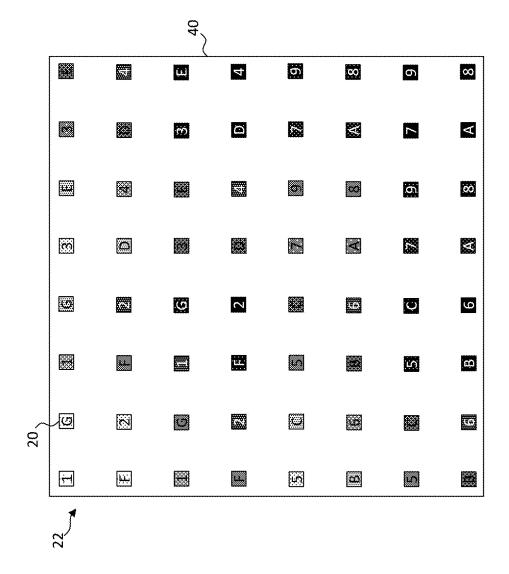

[0052] FIG. 37 is a plan view of a destination substrate with printed components from the native source substrate corresponding to FIG. 32 according to illustrative embodiments of the present disclosure;

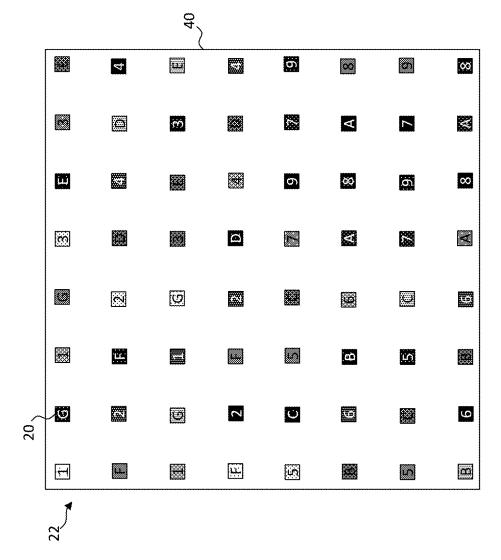

[0053] FIG. 38 is a plan view of a destination substrate with printed components from the native source substrate corresponding to FIG. 3 according to illustrative embodiments of the present disclosure; and

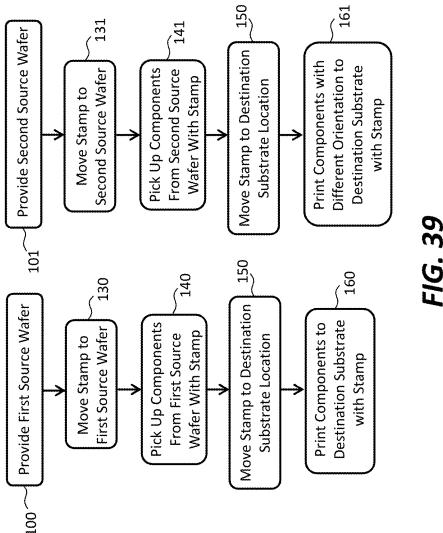

[0054] FIG. 39 is a flow diagram according to illustrative embodiments of the present disclosure.

[0055] The perspectives shown in FIGS. 4A, 6A, 7A, 9A, 10A, 12A, 13A, 15A, and 16-23 are exploded illustrations with exaggerated viewing angles and the two cross section lines A indicated in some of the perspective Figures are actually congruent.

[0056] Features and advantages of the present disclosure will become more apparent from the detailed description set forth below when taken in conjunction with the drawings, in which like reference characters identify corresponding elements throughout. In the drawings, like reference numbers generally indicate identical, functionally similar, and/or structurally similar elements. The figures are not necessarily drawn to scale.

# DETAILED DESCRIPTION OF CERTAIN EMBODIMENTS

[0057] Certain embodiments of the present disclosure are directed toward methods of micro-transfer printing arrays of components from a component source wafer to a destination substrate using a stamp, wherein an attribute or structure of the components varies systematically over the component source wafer so that different ones of the components in different locations on the component source wafer have a different structure, operation, appearance, or performance. The attribute variation can, in the absence of structures, devices, systems, and methods of the present disclosure, result in unwanted large-scale non-uniformity in component operation, structure, or appearance on the destination substrate. According to some embodiments of the present disclosure, the large-scale operation can be mitigated by providing components on a destination substrate at different orientations with respect to the attribute variation on a component source wafer. The components can be provided in arrays so that a first array is disposed with a first orientation and a second array is disposed with a second orientation, where the second orientation is different from the first orientation. Different orientations can, for example, comprise different spatial rotations, offsets, interlacings (e.g., interdigitations), or interlacing in one or two directions (dimensions) in which the attribute varies. Arrays of components 20 can be for example regular one-dimensional arrays or regular two-dimensional arrays.

[0058] FIG. 1 is a cross section of a component source wafer 10 comprising an array 22 of components 20 (e.g., 20a-20j). Components 20 can be native to component source wafer 10, that is components 20 can be constructed on, in, or over component source wafer 10 using, for example, photolithographic materials and methods useful for integrated circuit technology. Any manufacturing process experiences variation in materials and process control that can result in variation in native component source wafers 10. According to some embodiments, a plurality of components 20 (e.g., components 20a-20j) are disposed in, on, or over component source wafer 10. In some embodiments, com-

ponent source wafer 10 has an attribute or structure 12 that varies across component source wafer 10 (e.g., across a surface of component source wafer 10) that affects the structure, operation, appearance, or performance of components 20. The variation can be, but is not necessarily, monotonic with respect to one or more directions (e.g., orthogonal directions) over a component source wafer. For simplicity in explanation and to aid understanding, an attribute or structure 12 is referred to herein as an attribute 12. For example, attribute 12 can be an epitaxial layer whose thickness (as shown in FIG. 1), material purity, doping, or crystallinity varies across component source wafer 10. Attribute 12 can be particle contamination or any other variable attribute or structure 12 of component source wafer 10 that affects the structure, operation, or performance of components 20. The variation of attribute 12 can be linear (or non-linear) in one or two dimensions over component source wafer 10 or a surface of component source wafer 10. The variation of an attribute 12 can be spatially monotonic, so that attribute 12 is always increasing (or decreasing) in one or more directions either across the entire component source wafer 10 or portions of component source wafer 10 much larger than an extent or size of a component 20, for example the spatial extent of 10, 100, or 1000 components 20 over component source wafer 10 in one or two directions, or can be otherwise systematic, for example repetitive. Components 20 can be provided in an array 22, for example a regular array, in one or two dimensions over component source wafer 10 or a surface of component source wafer 10.

[0059] FIGS. 2 and 3 illustrate an array 22 of components 20 distributed regularly in two dimensions over a component source wafer 10, for example a rectangular portion of component source wafer 10. A variation of an attribute 12 is visually represented by the shading of component 20. A darker shading implies a greater amount or quantity of attribute 12, for example a greater epitaxial layer thickness. The shading of component 20 is merely illustrative of the variation of attribute 12 and does not imply that components 20 vary in color or appearance. By shading the illustration of component source wafer 10 in the figures, the variation in structure, operation, appearance, or performance of components 20 is visually apparent in the figures and is more readily understood. As shown in FIG. 2, the quantity of attribute 12 increases in one direction (e.g., horizontally), as shown by the arrow. Referring to FIG. 3, the quantity of attribute 12 increases in two directions (e.g., both horizontally and vertically), as shown by the arrow.

[0060] Referring to the sequential cross sections and perspectives of FIGS. 4A-23 and the flow diagram of FIG. 24, according to embodiments of the present disclosure, a method of micro-transfer printing comprises providing a component source wafer 10 comprising components 20 in step 100 and providing a stamp 30 in step 110 (as shown in the exploded FIG. 4A perspective and corresponding cross section FIG. 4B taken along cross section line A of FIG. 4A). Stamp 30 can, but does not necessarily, comprise stamp posts 32 each with a stamp post area on a distal end of stamp posts 32. The stamp posts 32 protrude from stamp 30 to contact components 20 when stamp 30 is pressed against components 20. As shown in FIG. 4B, components 20 are entirely disposed over, and can be formed on (e.g., in direct contact with), sacrificial portions 14 spatially separated by anchors 50 in sacrificial layer 11 of component source wafer 10. Sacrificial layer 11 can be a patterned sacrificial layer 11. Components 20 can be, but are not necessarily, arranged in a rectangular array 22, for example in a regular twodimensional arrangement, as shown in FIG. 4A. A dielectric layer 54 disposed over destination substrate 40 and sacrificial portions 14 connects each component 20 with a component tether 52 to an anchor 50. Component tethers 52 are not necessarily made from a dielectric or in a dielectric layer. Component tethers 52 can be laterally connected to anchors 50 (as shown) or disposed in other locations, for example beneath components 20.

[0061] Referring to FIG. 5, sacrificial portions 14 (shown in FIG. 4B) are sacrificed, for example by etching sacrificial portions 14 to form gaps 16, so that components 20 are suspended over gaps 16 and attached to anchors 50 of component source wafer 10 by component tethers 52 that maintain the physical position of components 20 with respect to component source wafer 10 after sacrificial portions 14 are etched. In some embodiments, each component is attached to each of one or more anchors 50 by one or more component tethers 52. Stamp 30 is moved into position with respect to component source wafer 10, for example by an opto-mechatronic motion platform, in step 130 and components 20 are picked up from component source wafer 10 by adhering components 20 to stamp 30, for example by pressing stamp 30 against components 20 on component source wafer 10 with the motion platform and adhering components 20 to the distal ends of stamp posts 32, for example with van der Waals or electrostatic forces.

[0062] As shown in the FIG. 6A perspective and FIG. 6B cross section taken along cross section line A of FIG. 6A, stamp 30 in contact with components 20 suspended over gaps 16 is then removed from component source wafer 10 by the motion platform, fracturing component tethers 52 from anchors 50 to form separated or fractured component tethers 53 and picking up components 20 from component source wafer 10 with stamp 30 in step 140, providing picked-up stamp components 20. Picked-up stamp components 20 can comprise a separated or fractured component tether 53.

[0063] Referring to the perspective of FIG. 7A and cross section of FIG. 7B taken along cross section line A of FIG. 7A, a destination substrate 40 is provided in step 120. In step 150, stamp 30 and stamp components 20 with fractured component tethers 53 are moved into position and aligned with respect to destination substrate 40.

[0064] Referring to FIG. 8, in step 160 picked-up stamp components 20 with fractured component tethers 53 are micro-transfer printed to a surface of destination substrate 40 in step 160 and, referring to FIGS. 9A and 9B, stamp 30 is removed from destination substrate 40.

[0065] If the process is not completed (done step 170), the process of picking up components 20 from component source wafer 10 is repeated (steps 130 and 140), possibly more than once. However, for at least one of the repetitions, micro-transfer printed components 20 are disposed with an orientation different from the orientation of the first micro-transfer print step 160. The orientation for a component source wafer 10 is taken with respect to the direction in which attribute 12 varies, for example the direction of the arrow in FIGS. 2 and 3. In some embodiments, every print step 160 is performed with a different orientation than the first print step 160. In some embodiments, only one or only some of the repeated print steps 160 is performed with a different orientation. In some embodiments, every other, every third, or every fourth repeated print step 160 is

performed with a different orientation. An orientation can be repeated for different print steps, for example two orientations can be alternately employed or multiple orientations (such as four orientations) can by cyclically employed.

[0066] As used herein, a different orientation can, but does not necessarily, include components 20 micro-transfer printed (step 160) with a different rotation, for example rotated in an array 22 adjacent to a micro-transfer printed array 22 of components 20, for example as shown in FIG. 32 discussed below. In some embodiments, a different orientation can include micro-transfer printed (step 160) components 20 that overlap with a micro-transfer printed array 22 of components 20. Overlapping arrays 22 of components 20 can be interlaced (e.g., interdigitated), for example as shown in FIG. 35 discussed below. In some embodiments, a different orientation can include arrays 22 of components 20 micro-transfer printed (step 160) to adjacent locations on a destination substrate 40 that are micro-transfer printed from locations on a component source wafer 10 that are not adjacent. In some embodiments, multiple different orientations are employed for micro-transfer printed arrays 22 of components 20, for example as shown in FIG. 33 discussed below. For example, an array 22 of components 20 with a different orientation from another array 22 of components 20 can be rotated and offset with respect to the other array 22 of components 20. Adjacent arrays 22 of components 20 are arrays 22 of components 20 that do not overlap and are not interlaced (e.g., interdigitated or intermingled) on a destination substrate 40 but that include components 20 that are in neighboring rows or columns(for example as shown in FIGS. 23, 26, and 31 discussed below) so that there are no components 20 between components 20 in adjacent arrays 22 on destination substrate 40 that are not in the adjacent arrays 22 of components 20 on component source wafer 10. That is, components 20 in adjacent arrays 22 on destination substrate 40 are not separated by any components 20 that are not part of the adjacent arrays 22 of components 20 on component source wafer 10.

[0067] Different orientations for micro-transfer printing can be enabled by moving any one or any combination of component source wafer 10, stamp 30, or destination substrate 40. For example, stamp 30 can be rotated after component 20 pickup from component source wafer 10 and before component 20 printing to destination substrate 40, destination substrate 40 can be rotated in different directions or in different amounts before each micro-transfer print step 160, or component source wafer 10 can be rotated in different directions or in different amounts before each micro-transfer pickup step 140.

[0068] Referring next to the perspective of FIG. 10A and cross section of FIG. 10B taken along cross section line A of FIG. 10A, stamp 30 is aligned with components 20 suspended over gaps 16 (step 130), brought into contact with components 20 on component source wafer 10 (shown in FIG. 11), and then removed from component source wafer 10 by the motion platform, fracturing component tethers 52 from anchors 50 to form separated or fractured component tethers 53 and picking up components 20 from component source wafer 10 with stamp 30 in step 140, as shown in the perspective of FIG. 12A and the corresponding cross section of FIG. 12B taken across cross section line A of FIG. 12A. [0069] As shown in the perspective of FIG. 13A and cross section of FIG. 13B taken along cross section line A of FIG. 13A, stamp 30 and stamp components 20 with fractured

component tethers 53 are moved into position with respect to destination substrate 40 (step 150). However, before micro-transfer printing components 20 to destination substrate 40 with stamp 30 in step 160, stamp 30 or destination substrate 40 is provided in a different orientation, for example by rotating stamp 30 or destination substrate 40, as indicated by the circular arrow in FIGS. 13A, 13B. Alternatively, as described below, stamp 30 or component source wafer 10 is provided in a different orientation before component 20 pickup in step 140, for example by rotating stamp 30 or component source wafer 10. Referring to FIG. 14, in step 160 picked-up stamp components 20 with fractured component tethers 53 are micro-transfer printed to destination substrate 40 in step 160 and, referring to FIGS. 15A and 15B, stamp 30 is removed from destination substrate 40.

[0070] Thus, according to some embodiments of the present disclosure, a method of micro-transfer printing comprises providing a component source wafer 10 and components 20 disposed in, on, or over component source wafer 10 (step 100), providing a destination substrate 40 (step 120), and providing a stamp 30 for transferring components 20 from component source wafer 10 to destination substrate 40 (step 110), where component source wafer 10 has an attribute or structure 12 that varies (e.g., monotonically) across component source wafer 10 that affects the structure, operation, appearance, or performance of the components 20. In steps 130, 140, 150, 160, a first array 22 of components 20 is transferred from component source wafer 10 to destination substrate 40 with a first orientation and in step 145, 130, 140, 150, 160 a second array 22 of components 20 is transferred from component source wafer 10 to destination substrate 40 with a second orientation different from the first orientation. Component 20 transfer can be performed using micro-transfer printing (e.g., dry contact printing), for example.

[0071] The process of printing components 20 in different orientations is repeated again. Referring to the perspective of FIG. 16, stamp 30 is aligned with components 20 on component source wafer 10 (step 130), brought into contact with components 20 on component source wafer 10, and then removed from component source wafer 10 by the motion platform, fracturing component tethers 52 from anchors 50 to form separated or fractured component tethers 53 and picking up components 20 from component source wafer 10 with stamp 30 in step 140, as shown in the perspective of FIG. 17. As shown in the perspective of FIG. 18, stamp 30 and stamp components 20 with fractured component tethers 53 are moved into position in a different orientation (illustrated by the circular arrow rotated in an opposite direction with respect to FIG. 13A, 13B) with respect to destination substrate 40 (step 150). Referring to FIG. 19, in step 160 picked-up stamp components 20 with fractured component tethers 53 are micro-transfer printed to destination substrate 40 in step 160 and stamp 30 is removed from destination substrate 40.

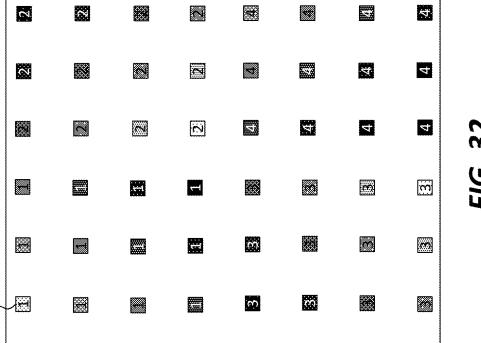

[0072] The process of printing components 20 in different orientations is repeated again for remaining components 20. Referring to the perspective of FIG. 20, stamp 30 is aligned with components 20 on component source wafer 10 (step 130). In this step, component source wafer 10 is provided in a different orientation (illustrated by the circular arrow), rather than providing the stamp in a different orientation, as in FIGS. 13A-B and FIG. 18. Stamp posts 32 of stamp 30 are brought into contact with components 20 on component

source wafer 10, and then removed from component source wafer 10 by the motion platform, fracturing component tethers 52 from anchors 50 to form separated or fractured component tethers 53 and picking up components 20 from component source wafer  $\hat{10}$  with stamp  $3\bar{0}$  in step 140, as shown in the perspective of FIG. 21. As shown in the perspective of FIG. 22, stamp 30 and stamp components 20 with fractured component tethers 53 are moved into position with respect to destination substrate 40 (step 150). A dashed circular arrow is illustrated in FIG. 22 to illustrate that destination substrate 40 can be rotated instead of rotating component source wafer 10 in FIG. 20 or stamp 30 in FIG. 16 to provide components 20 in a different orientation on destination substrate 40. As shown in FIG. 23, in step 160 picked-up stamp components 20 with fractured component tethers 53 are micro-transfer printed to destination substrate 40 in step 160 and stamp 30 is removed from destination substrate 40.

[0073] Components 20 are all micro-transfer printed from component source wafer 10 to destination substrate 40 in various orientations (step 170) and the process is completed (step 180).

[0074] FIG. 25 is an illustration of a component source wafer 10 having a four-by-four array 22 of components 20 whose attributes 12 vary monotonically (e.g., linearly) in each of two dimensions, indicated by the shading of the components 20 and corresponding to FIG. 3 (in a smaller component array 22). Components 20 on component source wafer 10 are labeled with a number corresponding to the stamp operation that micro-transfer prints components 20 from component source wafer 10 to destination substrate 40 using a stamp 30 with a two-by-two array of stamp posts 32, so that four stamp operations are required to complete the transfer, as described with respect to FIGS. 4A-23 above. Stamp operations that do not micro-transfer print components 20 in different orientations result in a distribution of components 20 on destination substrate 40, for example without different rotations. as shown in FIG. 26. As shown in FIG. 26 by the shading of components 20, the attribute 12 variation of component source wafer 10 is repeated multiple times, albeit at a different resolution on destination substrate 40 than on component source wafer 10.

[0075] FIG. 27 illustrates the result of micro-transfer printing sixteen four-by four arrays 22 of components 20 from a component source wafer 10 (e.g., corresponding to FIG. 2) onto a destination substrate 40 in a common orientation, for example without different rotations. Similarly, FIG. 28 illustrates the result of micro-transfer printing sixteen four-by four arrays 22 of components 20 from a component source wafer 10 (e.g., corresponding to FIG. 3) onto a destination substrate 40 in a common orientation, for example without different rotations. As shown by the shading of components 20, in these cases (FIGS. 26-28) the attribute 12 variation of component source wafer 10 is repeated multiple times in either one dimension (horizontally, as shown in FIG. 27) or in two dimensions (horizontally and vertically, as shown in FIG. 28) albeit at a different resolution on destination substrate 40 than on component source wafer 10.

[0076] FIG. 29 is a micrograph of sixteen arrays 22 of components 20 micro-transfer printed in a common orientation, for example without different rotations, from a component source wafer 10 (e.g., corresponding to FIG. 3) to a destination substrate 40. The regular variation in component

attributes 12 is readily visible. Such variation can be considered a form of pattern noise or fixed-pattern noise, often associated with image sensors. Such noise can be addressed by flat-field correction techniques that control the operation of components 20 electronically. However, according to some embodiments of the present disclosure, the variation (non-uniformity) can also be addressed by transferring arrays 22 of components 20 from a component source wafer 10 to a destination substrate 40 using different orientations for components 20, for example using micro-transfer printing or contact printing.

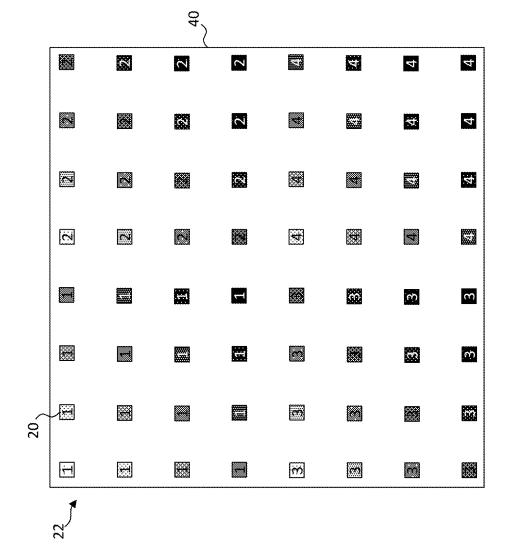

[0077] FIG. 30 is an illustration of a component source wafer 10 having an eight-by-eight array 22 of components 20 whose attributes 12 vary in two dimensions, indicated by the shading of the components 20 and corresponding to FIG. 3 (in a smaller array 22 of components 20) and FIG. 25 (in a larger array 22 of components 20). Components 20 on component source wafer 10 are labeled with a number corresponding to the operation (e.g., stamp operation) that transfers (e.g., micro-transfer prints) components 20 from component source wafer 10 to destination substrate 40, for example using a stamp 30 with a four-by-four array of stamp posts 32 spaced apart by two components 20, so that four operations are required to complete the transfer of the shown array. Operations that do not transfer (e.g., micro-transfer print) components 20 in different orientations result in a distribution of components 20 on destination substrate 40 as shown in FIG. 31. As shown in FIG. 31 by the shading of components 20, the attribute 12 variation of component source wafer 10 is repeated four times, albeit at a different resolution on destination substrate 40.

[0078] Referring to FIG. 32, in an illustration according to some embodiments of the present invention, arrays 22 of components 20 transferred (e.g., micro-transfer printed) in operations 2, 3, and 4 (e.g., stamp operations) each have different orientations on destination substrate 40 than the array 22 of components 20 transferred (e.g., micro-transfer printed) in operation 1 (e.g., a stamp operation). Each array 22 of components 20 transferred in operations 2, 3, and 4 is rotated with respect to array 22 of components 20 and is adjacent to array 22 of components 20 transferred in operation 1. Referring to FIG. 33, in an illustration according to some embodiments of the present invention, each array 22 of components 20 transferred (e.g., micro-transfer printed) in operations 2, 3, and 4 (e.g., stamp operations) is offset with respect to array 22 of components 20 as distributed on component source wafer 10 (shown in FIG. 30). Thus, the attribute 12 of components 20 varies less regularly with respect to spatial location on destination substrate 40.

[0079] Without wishing to be bound by any particular theory, such variation can be less objectionable to a human visual system for a particular application (e.g., if components 20 are light-emitting diodes in a display). For example, the array 22 shown in FIG. 33, that has been formed using different orientations, has an attribute 12 that varies with some frequency in one or more directions. For example, FIG. 33 shows some variation in the horizontal direction and a diagonal direction (e.g., from top left corner to bottom right corner). The comparative array 22 shown in FIG. 31, that has been formed using only a single orientation, also has an attribute 12 that varies with some frequency in one or more directions. Comparing the arrays 22 of FIG. 31 and FIG. 33, one of ordinary skill can appreciate that the frequency (or amplitude) of variation in at least one direc-

tion, for example in the aforementioned diagonal direction, is reduced in the array 22 of FIG. 33. In some embodiments, transferring using different orientations may also increase the frequency (or amplitude) of variation in a different direction, such as the horizontal direction. In some embodiments, multiple different orientations, such as offset and rotation, are used to further reduce variations, for example in multiple directions.

[0080] FIG. 34 is an illustration of a component source wafer 10 having an eight-by-eight array 22 of components 20 whose attributes 12 vary in two dimensions, indicated by the shading of the components 20 and corresponding to FIG. 3 (in a smaller array 22 of components 20) and FIG. 25 (in a larger array 22 of components 20). Components 20 on component source wafer 10 are labeled with a hexadecimal number (starting with '1' and ending with 'G') corresponding to the operation (e.g., stamp operation) that transfers (e.g., micro-transfer prints) components 20 from component source wafer 10 to destination substrate 40, for example using a stamp 30 with a two-by-two array of stamp posts 32, so that sixteen operations are required to complete the transfer of the shown array. As shown in FIG. 35, in an illustration according to some embodiments of the present invention, arrays 22 of components 20 transferred (e.g., micro-transfer printed) in operations 2-G (e.g., stamp operations) each have different orientations than the transferred (e.g., micro-transfer printed) array 22 of components 20 in operation 1 (e.g., a stamp operation). Each array 22 of components 20 transferred in operations 2-G is interlaced (e.g., interdigitated) with respect to array 22 of components 20 transferred in operation 1. As shown in FIG. 36, in an illustration according to some embodiments, each array 22 of components 20 transferred (e.g., micro-transfer printed) in operations 2-G (e.g., stamp operations) is offset and interlaced with respect to array 22 of components 20 transferred (e.g., micro-transfer printed) in operation 1 (e.g., a stamp operation) so that adjacent arrays 22 of components 20 micro-transfer printed on destination substrate 40 are not picked up from adjacent arrays 22 of components 20 on component source wafer 10 and the arrays 22 of components 20 are interlaced.

[0081] As shown in FIG. 37, in an illustration according to some embodiments of the present invention, each array 22 of components 20 transferred (e.g., micro-transfer printed) in operations 2-G (e.g., stamp operations) is offset, interlaced, and rotated with respect to array 22 of components 20 transferred (e.g., micro-transfer printed) in operation 1 (e.g., a stamp operation) so that adjacent arrays 22 of components 20 transferred to destination substrate 40 are not picked up from adjacent arrays 22 of components 20 on component source wafer 10 and the arrays 22 of components 20 are interlaced and rotated. Thus, without wishing to be bound to any particular theory, the attribute 12 of components 20 varies less regularly or less significantly with respect to a local average with respect to position on destination substrate 40 and can thus be less objectionable to the human visual system (e.g., for example if components 20 are light-emitting diodes in a display). For example, as shown in FIG. 37, two-by-two or four-by-four arrays 22 of adjacent components 20 on destination substrate 40 can have average attribute 12 values that have less variation than two-by-two or four-by-four arrays 22 of adjacent components 20 on the component source wafer 10.

[0082] FIG. 38 is an illustration according to some embodiments of the present disclosure wherein some of the arrays 22 of components 20 transferred (e.g., micro-transfer printed) in print steps 160 are rotated by different amounts with respect to others, for example some are not rotated, some are rotated 90 degrees, some are rotated 180 degrees, and some are rotated 270 degrees. The varying rotations reduce the systematic changes in attribute 12 and at least apparently randomize the changes in attribute 12 of components 20 distributed over destination substrate 40.

[0083] In some embodiments, a method comprises repeatedly transferring arrays 22 of components 20 from component source wafer 10 to destination substrate 40 N times in one dimension, where N/2 pairs of adjacent arrays 22 of components 20 on destination substrate 40 comprise array 22 i and array 22 (N-1-i) for each i from 0 to (N/2)-1.

[0084] For example, referring to FIG. 2, a horizontal one-dimensional array of sixteen components 20 (e.g., the top row of FIG. 2) has a monotonically changing attribute 12. Referring to FIG. 27, the components 20 are reordered in the same horizontal direction by transferring four groups (arrays 22) of four components 20 each (thus, in this example N=4 and i equals 0, 1, 2, and 3). (Note that the physical spacing of components 20 in FIG. 27 is one quarter that of FIG. 2.) If adjacent groups of four are sampled, as in FIG. 27, then components from group i=0 are transferred adjacent to components 20 from group i=1. Similarly, components 20 from group i=1 are also adjacent to components 20 from group i=2 and components 20 from group i=2 are also adjacent to components 20 from group i=3, so that the components 20 have attributes 12 ordered as 1, 2, 3, 4 in four horizontally adjacent arrays, as shown in FIG. 27. In contrast, according to the equation above and for some embodiments of the present invention, for arrays from zero to (N/2)-1=1, if components from group i=0 are disposed adjacent to components from group i=3 (because N-1-I=4-1-0=3) and components from group i=1 are disposed adjacent to components from group i=2 (because N-1-I=4-1-1=2), so that the components 20 have attributes 12 ordered as 1, 4, 2, 3, the changes in attribute 12 in the horizontal direction are no longer monotonic and the visibility or objectionability of the variation can be therefore reduced.

[0085] In some embodiments, a method of the present disclosure, comprises repeatedly transferring arrays 22 of components 20 from component source wafer 10 to destination substrate 40 N×M times in two dimensions, where N/2×M/2 two-by-two adjacent component arrays 22 on destination substrate 40 comprise array 22 (i, j), array 22 (N-1-i, j), array 22 (i, M-1-j), and array 22 (N-1-i, j)M-1-i) for each i from 0 to (N/2)-1 and each j from 0 to (M/2)-1. Thus, components 20 in different arrays 22 are interlaced in one or two dimensions. By transferring different arrays 22 of components 20 in such a manner, a variation in attributes 12 may be made less regular, less visible, or less objectionable; arrays 22 of components 20 on destination substrate 40 (after transfer) are mixed up with respect to the corresponding arrays 22 of components 20 on component source wafer 10 (before transfer). The two-dimensional case operates as described above with the one-dimensional case except in two orthogonal directions at the same time.

[0086] In some embodiments and as illustrated in FIG. 39, a method comprises transferring a plurality of component source wafers 10 and arrays 22 of components 20 from each component source wafer 10 onto destination substrate 40

with two or more different orientations. For example, the plurality of component source wafers 10 can comprise a first component source wafer 10 and a second component source wafer 10 different from the first component source wafer 10, provided in steps 100 and 101. The method can comprise interlacing (e.g., interdigitating) components 20 from first component source wafer 10 between components 20 from second component source wafer 10 for example by using the same or different stamps 30 to pick up components 20 from first and second component source wafers 10 in steps 130, 131 and 140, 141 respectively, move the stamp 30 to destination substrate 40 in step 150, and print components 20 to destination substrate 40 in step 160 with an orientation and print components 20 to destination substrate 40 in step 161 with a different orientation. In some embodiments, different component source wafers 10 have different kinds or types of components 20. For example, components 20 can be LEDs and the different component source wafers 10 can each include LEDs that emit a different color of light. For example, in some embodiments, each of three component source wafers 10 includes one of red, green, and blue LEDs that emit red, green, or blue light, respectively, and the different LEDs are transferred with different orientations. Sets of three different LEDS can comprise pixels in a display and destination substrate 40 can be a display substrate.

[0087] Displays having same and different color arrays 22 of LED components 20 of micro-transfer printed from one or more component source wafers 10 to a destination substrate 40 using multiple orientations have been constructed and visually examined and shown to have less visible variation in color and brightness.

[0088] In some embodiments of the present disclosure, the order in which components 20 are printed (e.g., front right components 20 on a stamp 30 versus back left components 20 on a stamp 30) is arbitrary.

[0089] According to some embodiments of the present disclosure, micro-transfer printing includes transferring components 20 from a source substrate (e.g., component source wafer 10) to a destination substrate (e.g., destination substrate 40) by contacting components 20 on the source substrate with a stamp 30 to remove components 20 from the source substrate, transferring stamp 30 and contacted components 20 to the destination substrate 40, and contacting components 20 to a surface of the destination substrate 40. Components 20 can be adhered to stamp 30 or the destination substrate 40 by, for example, one or more of van der Waals forces, electrostatic forces, magnetic forces, chemical forces, and adhesive forces (e.g., from an adhesive). In some embodiments of the present disclosure, components 20 are adhered to stamp 30 with separation-rate-dependent adhesion, for example kinetic control of viscoelastic stamp materials such as can be found in elastomeric devices such as a PDMS stamp 30. Stamps 30 can comprise stamp posts 32 having a stamp post area on the distal end of stamp posts 32. Stamp posts 32 can have a length, a width, or both a length and a width, similar or substantially equal to a length, a width, or both a length and a width of component 20. In some embodiments, as discussed further below, stamp posts 32 of a stamp 30 can be smaller than components 20 in one or two orthogonal directions.

[0090] In exemplary methods, a stamp 30 (e.g., a viscoelastic elastomer stamp, such as a stamp optionally comprising a plurality of stamp posts 32) is designed and fabricated to retrieve and transfer arrays 22 of components

20 from their native component source wafer 10 onto non-native destination substrates 40. In some embodiments, stamp 30 mounts onto motion-plus-optics machinery (e.g., an opto-mechatronic motion platform) that can precisely control stamp 30 alignment and kinetics with respect to both component source wafers 10 and destination substrates 40. During micro-transfer printing, the motion platform brings stamp 30 into contact with components 20 on component source wafer 10, with optical alignment performed before contact. For example, in some embodiments, light can be transmitted and/or received through stamp 30 (e.g., through one or more stamp posts 32) in order to perform an optical alignment. Rapid upward movement of the print-head fractures component tether(s) 52 forming fractured component tethers 53, transferring component(s) 20 to stamp 30 or stamp posts 32. The populated stamp 30 then travels to destination substrate 40 and one or more components 20 are then aligned (e.g., in a manner similar to for pick-up) to destination substrate 40 and printed.

[0091] A component source wafer 10 can be any source wafer or substrate with micro-transfer printable components 20 that can be transferred with a stamp 30. For example, a component source wafer 10 can be or include a semiconductor (e.g., silicon) in a crystalline or non-crystalline form, a compound semiconductor (e.g., comprising GaN or GaAs), or a glass, polymer, sapphire, or quartz wafer. Sacrificial portions 14 can be formed of a patterned oxide (e.g., silicon dioxide) or nitride (e.g., silicon nitride) layer or can be an anisotropically etchable portion of sacrificial layer 11 of component source wafer 10. Typically, but not necessarily, component source wafers 10 are smaller than destination substrates 40.

[0092] Exemplary components 20 include active, passive, and active and passive components 20. Exemplary components 20 include, but are not limited to, any one or more of integrated devices, integrated circuits (such as CMOS circuits), light-emitting diodes, photodiodes, sensors, electrical or electronic devices, optical devices, opto-electronic devices, magnetic devices, magneto-electronic devices, and piezo-electric device, materials or structures. Components 20 can comprise electronic component circuits that operate component 20. Components 20 can be responsive to electrical energy, to optical energy, to electromagnetic energy, to mechanical energy, or to a combination thereof. In some embodiments, a component 20 is a light-emitting diode (LED).

[0093] Components 20 formed or disposed in or on component source wafers 10 can be constructed using, for example, one or more of integrated circuit, micro-electromechanical, and photolithographic methods. Components 20 can comprise one or more different component materials, for example, non-crystalline or crystalline semiconductor materials such as silicon or compound semiconductor materials or non-crystalline or crystalline piezo-electric materials.

[0094] In some embodiments of the present disclosure, components 20 can be native to and formed on sacrificial portions 14 of component source wafers 10 and can include one or more seed layers used for constructing crystalline layers on or in component source wafers 10. In some examples, components 20, sacrificial portions 14, anchors 50, and component tethers 52 can be constructed using photolithographic processes. Components 20 can be microdevices having at least one of a length and width no more

than 200 microns(e.g., no more than 100 microns, no more than 50 microns, no more than 25 microns, no more than 15 microns, no more than 10 microns, or no more than five microns), and, optionally, a thickness of no more than 50 microns (e.g., no more than 25 microns, no more than 15 microns, no more than 10 microns, no more than five microns, no more than two microns, or no more than one micron). In some embodiments, components 20 can be unpackaged dice (each an unpackaged die) transferred directly from native component source wafers 10 on or in which components 20 are constructed to destination substrate 40 (without wafer dicing).

[0095] Anchors 50 and component tethers 52 can be or can comprise portions of component source wafer 10 that are not sacrificial portions 14 and can include layers formed on component source wafers 10, for example dielectric or metal layers and for example layers formed as a part of photolithographic processes used to construct or encapsulate components 20.

[0096] Destination substrate 40 can be any destination substrate or target substrate to which components 20 are transferred (e.g., micro-transfer printed), for example flat-panel display substrates, printed circuit boards, or similar substrates. Destination substrates 40 can be, for example substrates comprising glass, polymer, quartz, ceramics, metal, or sapphire. Destination substrates 40 can be semi-conductor substrates (for example silicon) or compound semiconductor substrates and can have multiple layers.

[0097] In some embodiments of the present disclosure, a layer of adhesive, such as a layer of resin, polymer, or epoxy, either curable or non-curable, adheres components 20 onto destination substrate 40 and can be disposed, for example by coating or lamination. In some embodiments, the layer of adhesive is disposed in a pattern, for example using inkjet, screening, or photolithographic techniques. In some embodiments, a layer of adhesive is coated, for example with a spray or slot coater, and then patterned, for example using photolithographic techniques.

[0098] Patterned electrical conductors (e.g., wires, traces, or electrical contact pads such as those found on printed circuit boards, flat-panel display substrates, and in thin-film circuits) can be formed on any one or combination of one or more components 20 and destination substrate 40. One or more electrical contact pads can be in or on destination substrate 40 and/or in or on one or more components 20 to electrically connect components 20. Such patterned electrical conductors and contact pads can comprise, for example metal, transparent conductive oxides, or cured conductive inks and can be constructed using photolithographic methods and materials, for example metals such as aluminum, gold, or silver deposited by evaporation and patterned using pattern-wise exposed, cured, and etched photoresists, or constructed using imprinting methods and materials or inkjet printers and materials, for example comprising cured conductive inks deposited on a surface or provided in microchannels in or on destination substrate 40.

[0099] Micro-transfer printing processes suitable for disposing components 20 onto destination substrates 40 are described in *Inorganic light-emitting diode displays using micro-transfer printing* (Journal of the Society for Information Display, 2017, DOI # 10.1002/jsid.610, 1071-0922/17/2510-0610, pages 589-609), U.S. Pat. 8,722,458 entitled *Optical Systems Fabricated by Printing-Based Assembly*, U.S. patent application Ser. No. 15/461,703 entitled Pressure

Activated Electrical Interconnection by Micro-Transfer Printing, U.S. Pat. No. 8,889,485 entitled *Methods for Surface Attachment of Flipped Active Components*, U.S. patent application Ser. No. 14/822,864 entitled *Chiplets with Connection Posts*, U.S. patent application Ser. No. 14/743, 788 entitled *Micro-Assembled LED Displays and Lighting Elements*, and U.S. patent application Ser. No. 15/373,865, entitled *Micro-Transfer Printable LED Component*, the disclosure of each of which is incorporated herein by reference in its entirety.

[0100] For a discussion of micro-transfer printing techniques, see also U.S. Pat. Nos. 7,622,367 and 8,506,867, each of which is hereby incorporated by reference in its entirety. Micro-transfer printing using compound micro-assembly structures and methods can also be used with the present disclosure, for example, as described in U.S. patent application Ser. No. 14/822,868, filed Aug. 10, 2015, entitled *Compound Micro-Assembly Strategies and Devices*, which is hereby also incorporated by reference in its entirety. Accordingly, in some embodiments, printed structure 99 is a compound micro-assembled structure.

[0101] According to various embodiments of the present disclosure, component source wafer 10 can be provided with components 20, patterned sacrificial portions 14, component tethers 52, and anchors 50 already formed, or they can be constructed as part of a method. Component source wafer 10, components 20, stamp 30, and destination substrate 40 can be made separately and at different times or in different temporal orders or locations and provided in various process states.

[0102] The spatial distribution of components 20 on a component source wafer 10 or printed structures 99 is a matter of design choice for the end product desired. In some embodiments of the present disclosure, all components 20 in an array 22 on a component source wafer 10 are transferred to a stamp 30. In some embodiments, a subset of components 20 in an array 22 on a component source wafer 10 is transferred. By varying the number and arrangement of stamp posts 32 on transfer stamps 30, the distribution of components 20 on stamp posts 32 of the transfer stamp 30 can be likewise varied, as can the distribution of components 20 on destination substrate 40.

[0103] Because components 20, in certain embodiments, can be made using integrated circuit photolithographic techniques having a relatively high resolution and cost and destination substrate 40, for example a printed circuit board, can be made using printed circuit board techniques having a relatively low resolution and cost, electrical conductors and substrate contact pads on destination substrate 40 can be much larger than electrical contacts or component electrodes on component 20, thereby reducing manufacturing costs. For example, in certain embodiments, micro-transfer printable component 20 has at least one of a width, length, and height from 0.5  $\mu m$  to 200  $\mu m$  (e.g., 0.5 to 2  $\mu m$ , 2 to 5  $\mu m$ , 5 to 10  $\mu m$ , 10 to 20  $\mu m$ , 20 to 50  $\mu m$ , 50 to 100  $\mu m$ , or 100 to 200  $\mu m$ ).

[0104] In certain embodiments, destination substrate 40 is or comprises a member selected from the group consisting of polymer, plastic, resin, polyimide, PEN, PET, metal, metal foil, glass, a semiconductor, and sapphire. In certain embodiments, destination substrate 40 has a thickness from 5 microns to 20 mm (e.g., 5 to 10 microns, 10 to 50 microns, 50 to 100 microns, 100 to 200 microns, 200 to 500 microns,

500 microns to 0.5 mm, 0.5 to 1 mm, 1 mm to 5 mm, 5 mm to 10 mm, or 10 mm to 20 mm).

[0105] Components 20, in certain embodiments, can be constructed using foundry fabrication processes used in the art. Layers of materials can be used, including materials such as metals, oxides, nitrides and other materials used in the integrated-circuit art. Each component 20 can be or include a complete semiconductor integrated circuit and can include, for example, transistors, diodes, light-emitting diodes, or sensors. Components 20 can have different sizes, for example, each having an area of 100 square microns or larger, 1000 square microns or larger or 10,000 square microns or larger, or 1 square mm or larger. Components 20 can have variable aspect ratios, for example between 1:1 and 10:1 (e.g., 1:1, 2:1, 5:1, or 10:1). Components 20 can be rectangular or can have other shapes.

[0106] Various embodiments of structures and methods are described herein. Structures and methods were variously described as transferring components 20, printing components 20, or micro-transfer printing components 20 as examples and the particular word used should be understood to be non-limiting as to the methods that may be used to implement the described embodiments. In some embodiments, micro-transfer-printing includes using a stamp 30 (e.g., an elastomeric stamp 30, such as a PDMS stamp 30) to transfer a component 20 using controlled adhesion. For example, an exemplary stamp 30 can use kinetic or shearassisted control of adhesion between the stamp 30 and a component 20. It is contemplated that, in certain embodiments, where a method is described as including printing (e.g., micro-transfer-printing) a component 20, other analogous embodiments exist using a different transfer method. As used herein, transferring a component 20 (e.g., from a component source wafer 10 or wafer to a destination substrate 40) can be accomplished using any one or more of a variety of known techniques. For example, in certain embodiments, a pick-and-place method can be used. As another example, in certain embodiments, a flip-chip method can be used (e.g., involving an intermediate, handle or carrier substrate). In methods according to certain embodiments, a stamp 30 is a vacuum tool or other transfer device used to transfer components 20. In some embodiments, a stamp 30 uses one or more of electrostatic forces, magnetic forces, and vacuum forces to transfer components 20 (e.g., applied to individual components 20 by individual stamp posts 32).

[0107] As is understood by those skilled in the art, the terms "over" and "under" are relative terms and can be interchanged in reference to different orientations of the layers, elements, and substrates included in the present disclosure. Furthermore, a first layer "on" a second layer is a relative orientation of the first layer to the second layer that does not preclude additional layers being disposed therebetween. For example, a first layer on a second layer, in some implementations, means a first layer directly on and in contact with a second layer. In other implementations, a first layer on a second layer with another layer therebetween (e.g., an in mutual contact).

[0108] Having described certain implementations of embodiments, it will now become apparent to one of skill in the art that other implementations incorporating the concepts of the disclosure may be used. Therefore, the disclosure

should not be limited to certain implementations, but rather should be limited only by the spirit and scope of the following claims.

[0109] Throughout the description, where apparatus and systems are described as having, including, or comprising specific elements, or where processes and methods are described as having, including, or comprising specific steps, it is contemplated that, additionally, there are apparatus and systems of the disclosed technology that consist essentially of, or consist of, the recited elements, and that there are processes and methods according to the disclosed technology that consist essentially of, or consist of, the recited processing steps.

[0110] It should be understood that the order of steps or order for performing certain action is immaterial so long as the disclosed technology remains operable. Moreover, two or more steps or actions in some circumstances can be conducted simultaneously. The disclosure has been described in detail with particular reference to certain embodiments thereof, but it will be understood that variations and modifications can be effected within the spirit and scope of the disclosure.

## PARTS LIST

[0111] A cross section line

[0112] 10 component source wafer

[0113] 11 sacrificial layer

[0114] 12 attribute/structure/epitaxial (epi) layer

[0115] 14 sacrificial portions

[0116] 16 gap

[0117] 20 component

[0118] 20*a*-20*j* component

[0119] 22 array

[0120] 30 stamp

[0121] 32 stamp post

[0122] 40 destination substrate

[0123] 50 anchor

[0124] 52 component tether

[0125] 53 fractured component tether

[0126] 54 dielectric layer

[0127] 99 printed structure

[0128] 100 provide component source wafer step

[0129] 110 provide stamp step

[0130] 120 provide destination substrate step

[0131] 130 move stamp to component source wafer step

[0132] 131 move stamp to second component source wafer step

[0133] 140 pick up components from component source wafer with stamp step

[0134] 141 pick up components from second component source wafer with stamp step

[0135] 145 rotate source wafer

[0136] 150 move stamp to destination substrate location step

[0137] 160 print components to destination substrate with stamp step

[0138] 161 print components with different orientation to destination substrate with stamp step

[0139] 170 done step

[0140] 180 complete step

What is claimed:

1. A method of micro-transfer printing, comprising: providing a component source wafer and components disposed in, on, or over the component source wafer, providing a destination substrate, and providing a stamp for transferring the components from the component source wafer to the destination substrate, wherein the component source wafer has an attribute or structure that varies across the component source wafer such that different ones of the components in different locations have a different structure, operation, appearance, or performance;

transferring a first array of components from the component source wafer to the destination substrate with a first orientation; and

transferring a second array of components from the component source wafer to the destination substrate with a second orientation, wherein the second orientation is different from the first orientation.

- 2. The method of claim 1, comprising transferring the first array and transferring the second array using micro-transfer printing.

- 3. The method of claim 1, wherein the second orientation is rotated relative to the first array to provide different first and second orientations.

- **4**. The method of claim **3**, wherein the second orientation is rotated 90 degrees or 270 degrees with respect to the first orientation.

- **5.** The method of claim **3**, wherein the second orientation is rotated 180 degrees with respect to the first orientation.

- **6**. The method of claim **1**, comprising transferring the second array of components adjacent to the first array of components on the destination substrate.

- 7. The method of claim 1, comprising repeatedly transferring arrays of components from the component source wafer to the destination substrate with adjacent arrays on the destination substrate transferred at different orientations.

- 8. The method of claim 7, comprising repeatedly transferring arrays of components from the component source wafer to the destination substrate N times in one dimension, where N/2 pairs of adjacent arrays on the destination substrate comprise array i and array (N-1-i) for each i from 0 to (N/2)-1.

- 9. The method of claim 7, comprising repeatedly transferring arrays of components from the component source wafer to the destination substrate N×M times in two dimensions, where  $N/2 \times M/2$  two-by-two adjacent component arrays on the destination substrate comprise array (i, j), array (N-1-i, j), array (i, M-1-j), and array (N-1-i, M-1-j) for each i from 0 to (N/2)-1 and each j from 0 to (M/2)-1.

- 10. The method of claim 1, comprising interlacing the second array with respect to the first array in at least one dimension to provide different first and second orientations.

- 11. The method of claim 1, wherein the interlacing is in two dimensions.

- 12. The method of claim 1, wherein the first array and the second array are each regular, arrangements of components in one dimension.

- 13. The method of claim 1, wherein the first array and the second array are each regular arrangements of components in two dimensions.

- 14. The method of claim 1, comprising offsetting the second array with respect to the first array on the destination substrate by an amount that is different from an offset of the first array with respect to the second array on the component source wafer to provide different first and second orientations.

- 15. The method of claim 14, wherein the second array is disposed with respect to the first array on the destination substrate in a different direction than the second array is disposed with respect to the first array on the component source wafer.

- 16. The method of claim 14, wherein the first array and second array are adjacent on the component source wafer before transferring but are not adjacent on the destination substrate after transferring.

- 17. The method of claim 1, comprising:

- providing a plurality of component source wafers, wherein the plurality of component source wafers comprises the component source wafer; and

- comprising transferring arrays of components from each of the component source wafers onto the destination substrate with two or more different orientations.

- 18. The method of claim 17, wherein the plurality of component source wafers comprises a first component source wafer and a second component source wafer different from the first component source wafer, and the method comprises interlacing components from the first component source wafer between components from the second component source wafer.

- 19. The method of claim 1, wherein the components are light-emitting components.

- 20. The method of claim 1, wherein the components are inorganic light-emitting diodes.

\* \* \* \* \*