# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2020/0227518 A1 Laven et al.

Jul. 16, 2020 (43) **Pub. Date:**

### (54) SEMICONDUCTOR DEVICE WITH STRIPE-SHAPED CELL TRENCH STRUCTURES AND RECESSED CONTACTS AND METHOD OF MANUFACTURING **THEREOF**

- (71) Applicant: Infineon Technologies AG, Neubiberg

- (72) Inventors: Johannes Georg Laven, Taufkirchen (DE); Maria Cotorogea, Taufkirchen (DE); Hans-Joachim Schulze, Taufkirchen (DE); Haybat Itani, Villach (AT); Erich Griebl, Dorfen (DE); Andreas Haghofer, Villach (AT)

- (21) Appl. No.: 16/828,665

- (22) Filed: Mar. 24, 2020

#### Related U.S. Application Data

(63) Continuation of application No. 16/110,508, filed on Aug. 23, 2018, now Pat. No. 10,629,676, which is a continuation of application No. 15/589,531, filed on May 8, 2017, now abandoned, which is a continuation of application No. 13/963,312, filed on Aug. 9, 2013, now Pat. No. 9,666,663.

### **Publication Classification**

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

|      | H01L 29/06  | (2006.01) |

|      | H01L 21/265 | (2006.01) |

|      | H01L 29/40  | (2006.01) |

|      | H01L 29/417 | (2006.01) |

|      | H01L 29/66  | (2006.01) |

|      | H01L 21/22  | (2006.01) |

|      | H01L 29/78  | (2006.01) |

| H01L 21/223 | (2006.01) |

|-------------|-----------|

| H01L 21/311 | (2006.01) |

| H01L 29/08  | (2006.01) |

| H01L 29/10  | (2006.01) |

| H01L 29/423 | (2006.01) |

(52) U.S. Cl.

CPC ...... H01L 29/06 (2013.01); H01L 29/4236 (2013.01); H01L 29/407 (2013.01); H01L 29/41766 (2013.01); H01L 29/66727 (2013.01); H01L 29/66734 (2013.01); H01L 21/22 (2013.01); H01L 21/265 (2013.01); H01L 29/7813 (2013.01); H01L 21/2236 (2013.01); H01L 21/26513 (2013.01); H01L 21/31111 (2013.01); H01L 29/0657 (2013.01); H01L 29/0696 (2013.01); H01L 29/0865 (2013.01); H01L 29/1095 (2013.01); H01L 21/26586 (2013.01)

#### (57)**ABSTRACT**

A semiconductor device includes a plurality of first and second stripe-shaped cell trench structures formed in a semiconductor substrate and extending lengthwise in parallel with one another. Each stripe-shaped cell trench structure includes a buried electrode and an insulator layer between the buried electrode and the semiconductor substrate. A recess is formed in the insulator layer along a sidewall of one or more of the first stripe-shaped cell trench structures and vertically extends to a corresponding heavily doped contact zone. An electrically conductive material disposed in each recess contacts the corresponding buried electrode, a corresponding source zone and a corresponding heavily doped contact zone at the sidewall. Two or more of the first stripe-shaped cell trench structures are interposed between neighboring ones of the second stripe-shaped cell trench structures. Source zones alternate with portions of body zones in a lateral direction parallel to the stripe-shaped cell trench structures.

FIG 1B

FIG 1C

FIG 1D

FIG 2

FIG 3A

FIG 3B

FIG 3C

220 510 315 150a 315a 315b 220 520 150a 510 220 +110 150b 316 510 316 220 150b 510 + 1 0 150b 220 510 315 150a 525 220 520 526 315 150a 510 220

220 510 305 150a 305a 305b 220 520 150a  $\bigcirc$ 510 306 220 150b  $\Box$ 510 306 220 150b α. 510 150b Ω. 220 510 305 150a 220 520 526 305 150a  $\Box$ 510 220 515

226 Ω. 336 520 Ω.  $\Box$ 510 Q. 226 Q. Ω. 336 520  $\Box$ 510 226

#### SEMICONDUCTOR DEVICE WITH STRIPE-SHAPED CELL TRENCH STRUCTURES AND RECESSED CONTACTS AND METHOD OF MANUFACTURING THEREOF

#### **BACKGROUND**

[0001] Semiconductor devices based on vertical IGFET (insulated gate field effect transistor) cells include cell trench structures with buried electrodes and semiconductor mesas between the cell trench structures. Typically a photolithographic mask defines placement and size of the cell trench structures and another photolithographic mask defines placement and size of contact structures providing electric contacts to impurity zones in the semiconductor mesas. Other approaches rely on forming the contact structures self-aligned to the cell trench structures. It is desirable to provide semiconductor devices with narrow semiconductor mesas and small distances between neighboring cell trench structures in a reliable way and at low costs.

#### **SUMMARY**

[0002] According to an embodiment, a method of manufacturing a semiconductor device is provided. First and second cell trench structures are provided that extend from a first surface into a semiconductor substrate. The first cell trench structure includes a first buried electrode and a first insulator layer between the first buried electrode and a semiconductor mesa separating the first and second cell trench structures. A capping layer is provided that covers the first surface. The capping layer is patterned to form an opening having a minimum width that is larger than a thickness of the first insulator layer. The opening exposes a first vertical section of the first insulator layer at the first surface. An exposed portion of the first insulator layer is removed to form a recess between the semiconductor mesa and the first buried electrode. A contact structure is provided in the opening and the recess.

[0003] According to another embodiment, a method of manufacturing a semiconductor device includes introducing first and second cell trenches from a first surface into a semiconductor substrate, wherein first semiconductor mesas are formed between first and second cell trenches and second semiconductor mesas are formed between the first cell trenches. A first insulator layer is provided that lines at least sidewalls of the first cell trenches. First buried electrodes are provided in the first cell trenches on the first insulator layer. A capping layer is provided that covers the first surface. The capping layer is patterned to form first and second openings having a minimum width that is larger than a thickness of the first insulator layer. The first openings expose first vertical sections of the first insulator layers adjoining the first semiconductor mesas, respectively. The second openings expose the first buried electrodes of first cell trenches located between second semiconductor mesas. Exposed portions of the first insulator layers are removed to form recesses between the first semiconductor mesas and adjoining ones of the first buried electrodes. Conductive material is deposited to form, in the recesses and the first openings, first contact structures and second contact structures in the second openings.

[0004] Another embodiment refers to a semiconductor device with first and second cell trench structures extending

from a first surface into a semiconductor substrate. First semiconductor mesas separate first and second cell trench structures and second semiconductor mesas separate first cell trench structures. The first cell trench structures include a first buried electrode and a first insulator layer respectively, wherein first vertical sections of the first insulator layers separate the first buried electrodes from the first semiconductor mesas. A capping layer is located on the first surface. The semiconductor device includes first contact structures, wherein each first contact structure includes a first section in an opening of the capping layer and a second section between one of the first semiconductor mesas and one of the first buried electrodes directly adjoining the respective first semiconductor mesa.

[0005] Those skilled in the art will recognize additional features and advantages upon reading the following detailed description and on viewing the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0006] The accompanying drawings are included to provide a further understanding of the invention and are incorporated in and constitute a part of this specification. The drawings illustrate the embodiments of the present invention and together with the description serve to explain principles of the embodiment. Other embodiments and intended advantages will be readily appreciated as they become better understood by reference to the following detailed description

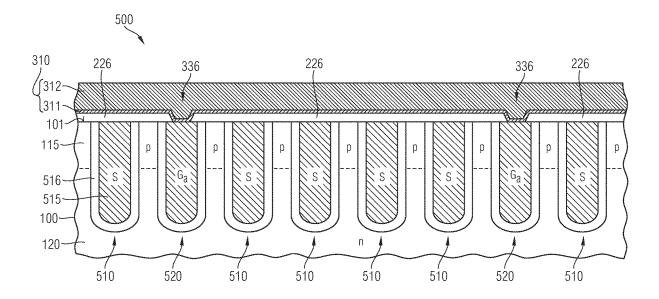

[0007] FIG. 1A is a schematic cross-sectional view of a portion of a semiconductor substrate after providing an etch mask.

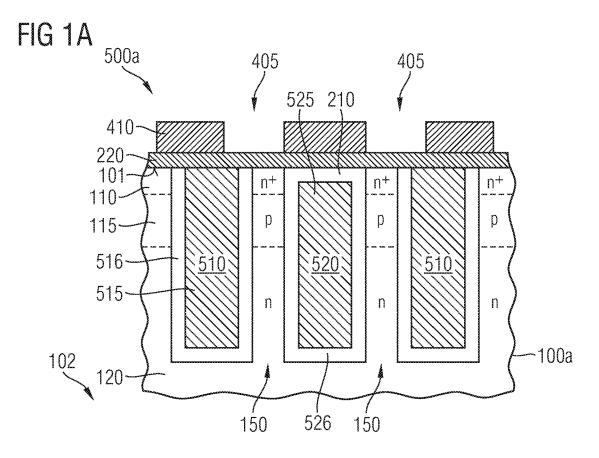

[0008] FIG. 1B is a schematic cross-sectional view of the semiconductor substrate portion of FIG. 1A after providing openings in a capping layer by using the etch mask.

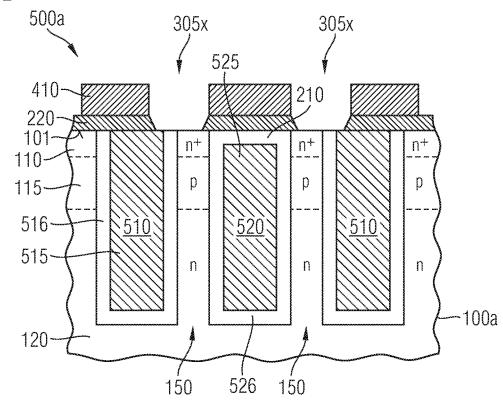

[0009] FIG. 1C is a schematic cross-sectional view of the semiconductor substrate portion of FIG. 1B after forming recesses between first cell trench structures and first semiconductor mesas.

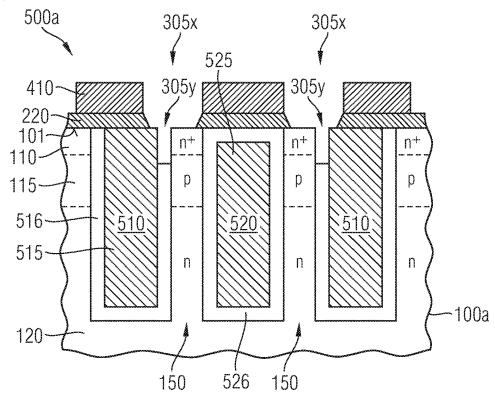

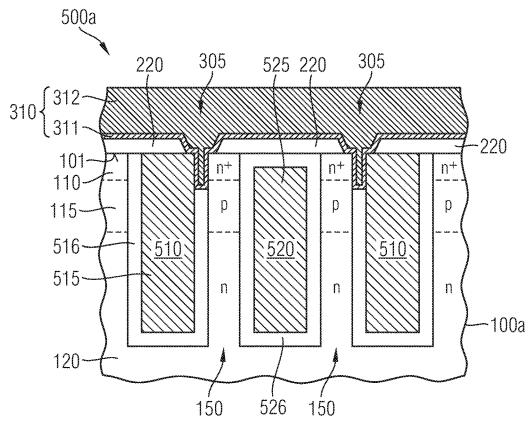

[0010] FIG. 1D is a schematic cross-sectional view of the semiconductor substrate portion of FIG. 1C after providing solid contact structures filling the openings and the recesses.

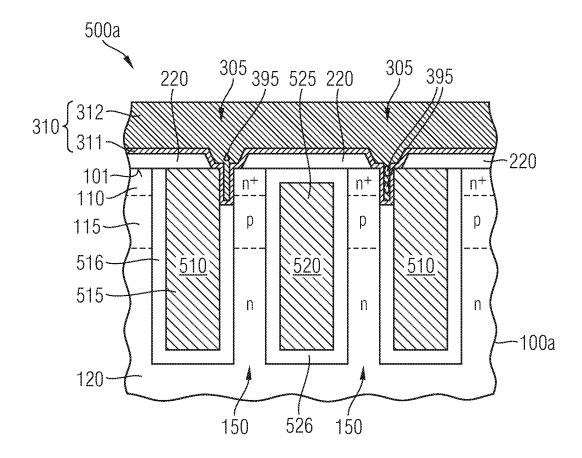

[0011] FIG. 2 is a schematic cross-sectional view of the semiconductor substrate portion of FIG. 1C after providing contact structures with voids in the openings and the recesses.

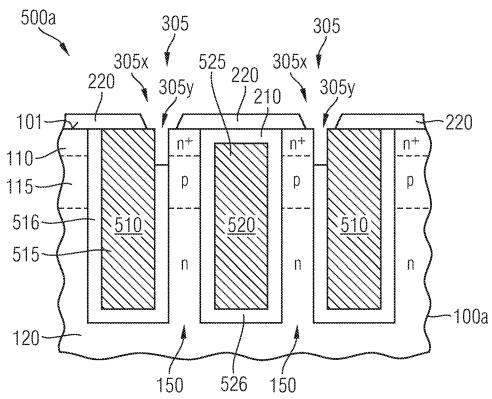

[0012] FIG. 3A shows a portion of a semiconductor substrate after providing recesses between a first buried electrode and first semiconductor mesas.

[0013] FIG. 3B shows the semiconductor substrate portion of FIG. 3A after widening the recesses.

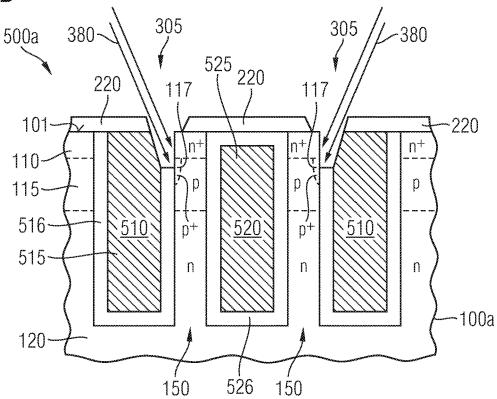

[0014] FIG. 3C illustrates the semiconductor substrate portion of FIG. 2B after providing contact structures in the openings and widened recesses.

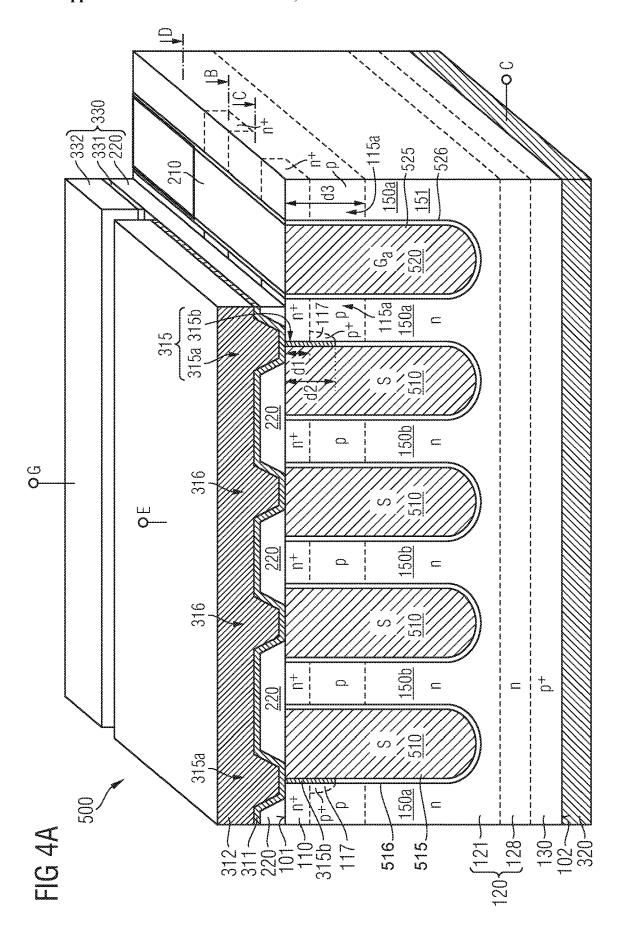

[0015] FIG. 4A is a schematic perspective view of a portion of semiconductor device in accordance with an embodiment related to an IGBT.

[0016] FIG. 4B illustrates a cross section of the semiconductor devices of FIG. 4A along section line B.

[0017] FIG. 4C illustrates a section of the semiconductor devices of FIG. 4A along cross section line C.

[0018] FIG. 4D illustrates a section of the semiconductor devices of FIG. 4A along cross section line D.

#### DETAILED DESCRIPTION

[0019] In the following detailed description, reference is made to the accompanying drawings, which form a part hereof, and in which are shown by way of illustrations specific embodiments in which the invention may be practiced. It is to be understood that other embodiments may be utilized and structural or logical changes may be made without departing from the scope of the present invention. For example, features illustrated or described for one embodiment can be used on or in conjunction with other embodiments to yield yet a further embodiment. It is intended that the present invention includes such modifications and variations. The examples are described using specific language that should not be construed as limiting the scope of the appending claims. The drawings are not scaled and are for illustrative purposes only. For clarity, the same elements have been designated by corresponding references in the different drawings if not stated otherwise.

[0020] The terms "having", "containing", "including", "comprising" and the like are open and the terms indicate the presence of stated structures, elements or features but not preclude additional elements or features. The articles "a," "an" and "the" are intended to include the plural as well as the singular, unless the context clearly indicates otherwise. The term "electrically connected" describes a permanent low-ohmic connection between electrically connected elements, for example a direct contact between the concerned elements or a low-ohmic connection via a metal and/or highly doped semiconductor. The term "electrically coupled" includes that one or more intervening element(s) adapted for signal transmission may be provided between the electrically coupled elements, for example elements that are controllable to temporarily provide a low-ohmic connection in a first state and a high-ohmic electric decoupling in a second state.

[0021] The Figures illustrate relative doping concentrations by indicating "-" or "+" next to the doping type "n" or "p". For example, "n" means a doping concentration that is lower than the doping concentration of an "n"-doping region while an "n"-doping region has a higher doping concentration than an "n"-doping region. Doping regions of the same relative doping concentration do not necessarily have the same absolute doping concentration. For example, two different "n"-doping regions may have the same or different absolute doping concentrations.

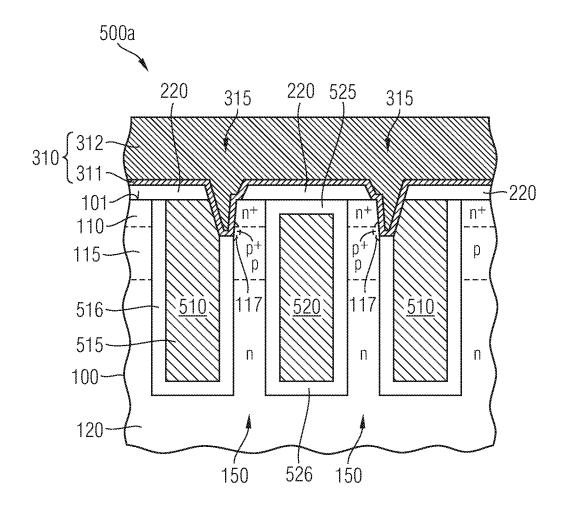

[0022] FIGS. 1A to 1D refer to a semiconductor substrate 500a consisting of or containing a semiconductor layer 100a of a single-crystalline semiconductor material. The single-crystalline semiconductor material may be silicon Si, silicon carbide SiC, germanium Ge, a silicon germanium crystal Site, gallium nitride GaN or gallium arsenide GaAs. The semiconductor substrate 500a may be a silicon wafer from which a plurality of identical semiconductor dies is obtained. The semiconductor layer 100a has a planar first surface 101 and a second surface 102 parallel to the first surface 101. The normal to the first and second surfaces 101, 102 defines a vertical direction and directions orthogonal to the vertical direction are lateral directions.

[0023] In at least a portion of the semiconductor substrate 500a, a first layer of a first conductivity type may be formed that directly adjoins the first surface 101. The first layer of the first conductivity type may form a planar interface with a layer of a second, complementary conductivity type that separates the first layer of the first conductivity type from a

second layer of the first conductivity type. The interfaces between the layers may be parallel to the first surface 101.

[0024] The first conductivity type may be the n type and the second conductivity type may be the p type as illustrated in the Figures. According to other embodiments the first conductivity type may be the p type and the second conductivity type may be the n type. Outside the illustrated portion, the semiconductor layer 100a may include further impurity zones, intrinsic zones, as well as dielectric and conductive structures that may be configured to form electric circuits.

[0025] First and second cell trench structures 510, 520 extend from the first surface 101 into the semiconductor substrate 500a, wherein buried edges of the first and second cell trench structures have a greater distance to the first surface 101 than a pn junction between the layer of the second conductivity type and the second layer of the first conductivity type. The cell trench structures 510, 520 provide segments in the first layer of the first conductivity type and the layer of the second conductivity type such that semiconductor mesas 150 between the first and second cell trench structures 510, 520 have a layered structure with source zones 110 of the first conductivity type directly adjoining the first surface 101 and body zones 115 of the second conductivity type separating the source zones 110 from portions of a drift layer 120 of the first conductivity type.

[0026] The first cell trench structures 510 include at least a first buried electrode 515 and a first insulator layer 516 separating the first buried electrode 515 from the semiconductor material of the semiconductor substrate 500*a* outside the first and second cell trench structures 510, 520,

[0027] Each second cell trench structure 520 includes a second buried electrode 525 and a second insulator layer 526 separating the second buried electrode 525 from the semiconductor material of the semiconductor substrate 500a outside the cell trench structures 510, 520. At least one of the first and second cell trench structures 510, 520 may include a further buried electrode dielectrically insulated from the respective first or second buried electrode 515, 525.

[0028] The first and second cell trench structures 510, 520 may have the same vertical and lateral dimensions. According to other embodiments the first cell trench structures 510 are wider or narrower than the second cell trench structures 520. Alternatively or in addition, the vertical extension of the first cell trench structures 510 exceeds or falls below the vertical extension of the second cell trench structures 520. According to an embodiment, the vertical extension of both the first and the second cell trench structures 510, 520 may be in a range from 500 nm to 20  $\mu m$ , e.g. in a range from 2  $\mu m$  to 7  $\mu m$ .

[0029] The first and second buried electrodes 515, 525 and, if applicable, the further buried electrode(s) may be provided from one or more conductive materials including polycrystalline silicon (polysilicon), which may be heavily doped, metal silicides, carbon C, metals, e.g. copper or tungsten, metal alloys, metal nitrides, metal silicides or other metal compounds, e.g. titanium nitride TiN, titanium tungstenide TiW, tantalum nitride TaN and others. For example, the first, the second, or both buried electrodes 515, 516 have a layered structure including two or more layers of the above-mentioned materials. The first and second buried electrodes 515, 516 may have the same structure and may

contain the same materials or may have different structures and/or contain different materials.

[0030] The first and second insulator layers 516, 526 may have the same thickness or may have different thicknesses. For example, the first insulator layer 516 may be thicker than the second insulator layer 526. The first and second insulator layers 516, 526 may be based on the same materials or may consist of or may include different materials such as semiconductor oxides, e.g. silicon oxide, silicon nitride, alumina, and hafnium oxide, by way of example. According to an embodiment, at least one of the first and second insulator layers 516, 526 has a layered structure including one or more different dielectric materials, A thickness of the first and second insulator layers may be between 30 nm and 200 nm, e.g, in the range between 80 nm and 120 nm. The second cell trench structure 520 may include a capping dielectric 210 between the first surface 101 and the second buried electrode 525. The first cell trench structure 510 may or may not include a structure corresponding to the capping dielectric 210.

[0031] The first and second buried electrodes 515, 525 may be electrically connected to each other. According to the illustrated embodiment the first and second buried electrodes 515, 525 are electrically separated from each other and can be connected to different signals or potentials. A potential applied to the second buried electrodes 525 may control the charge carrier distribution in the adjoining body zones 115 such that along the second insulator layers 526 a conductive channel may be formed when the potential applied to the second buried electrodes 525 exceeds a predefined threshold voltage. Sections of the second insulator layers 526 adjoining the body zones 115 are effective as gate dielectrics.

[0032] A capping layer 220 is provided on the first surface 101 and covers the first and second cell trench structures 510, 520 as well as the semiconductor mesas 150. The capping layer 220 includes one or more dielectric layers, each layer provided, for example, from deposited semiconductor oxide, for example a silicon oxide generated by using TEOS (tetraethyl orthosilicate) as precursor material, other silicon oxides, silicon nitride, or silicon oxynitride. The thickness of the capping layer 220 may be approximately uniform and may range from about 100 nm to 1  $\mu$ m, by way of example.

[0033] A photo resist layer is deposited on the capping layer 220 and patterned by photolithographic techniques to form an etch mask 410.

[0034] FIG. 1A shows the capping layer 220 covering the first and second cell trench structures 510, 520 and the semiconductor mesas 150 between the first and second cell trench structures 510, 520. Mask openings 405 in the etch mask 410 expose portions of the capping layer 220 in the vertical projection of first vertical sections of the first insulator layers 516, wherein the first vertical sections adjoin such semiconductor mesas 150 that separate first and second cell trench structures 510, 520. The mask openings 405 also expose portions of the capping layer 220 in the vertical projection of portions of the semiconductor mesas 150 directly adjoining the concerned sections of the first insulator layers 516 as well as portions of the capping layer 220 in the vertical projection of a portion of the first buried electrode 515 directly adjoining the concerned sections of the first insulator layer 516.

[0035] The etch mask 410 covers portions of the capping layer 220 in the vertical projection of the second cell trench

structures 520 as well as portions of the capping layer 220 in the vertical projection of second vertical sections of the first insulator layers 516 adjoining semiconductor mesas 150 between first cell trench structures 510. Using the etch mask 410, a predominantly anisotropic etch recesses the exposed portions of the capping layer 220. The etch removes the material of the capping layer 220 at a higher rate than the single crystalline semiconductor material of the semiconductor mesas 150 and the material of the first buried electrodes 515. The etch process may include an endpoint detection sensitive to reaching at least one of the semiconductor mesas 150, the first vertical sections of the first insulator layer 516, and the first buried electrode 515.

[0036] FIG. 1B shows openings 305x in the capping layer 220 after the etching has reached the first surface 101. The openings 305x expose the first vertical sections of the first insulator layers 516, portions of the first buried electrodes 515 directly adjoining the concerned sections of the first insulator layers 516 and portions of semiconductor mesas 150 directly adjoining the concerned sections of the first insulator layers 516.

[0037] After detecting the endpoint, an in-situ over etch may be performed for a predefined time to recess the exposed first vertical sections of the first insulator layers 516. The recess etch removes exposed portions of the first insulator layers 516 up to a second distance to the first surface 101, which is greater than a first distance between the first surface 101 and the interface between the source and body zones 110, 115 and which is smaller than a third distance between the first surface 101 and the interface between the body zones 115 and the drift layer 120. The second distance may be at least 200 tun and at most 1  $\mu m$ , e.g. between 400  $\mu m$  and 600  $\mu m$ . The material of the first insulator layer 516 is recessed at a removal rate that may be at least five times the removal rate for the semiconductor material and/or the material of the first buried electrode 515.

[0038] FIG. 1C shows the resulting recesses 305y between the concerned first buried electrodes 515 and the concerned semiconductor mesas 150. Due to the selectivity of the etch of the insulator layer 516, the recesses are self-aligned within the openings 305x to the first cell trench structures 510 and the concerned semiconductor mesas 150. In the layout, the width of the semiconductor mesas 150 may be further reduced, e.g. to below 400 nm.

[0039] Whereas conventional approaches provide a first etch process through the material of a capping layer and a second etch process for providing contact grooves in the semiconductor materials of semiconductor mesas and buried electrodes, the present embodiment provides one combined etch for openings in the capping layer and recesses along the semiconductor mesas 150. The combined etch may be performed as one in-situ process at the same tool.

[0040] One or more conductive materials are deposited to form a first electrode structure 310 on the side of the semiconductor substrate 500a defined by the first surface 101 as well as contact structures 305 electrically connecting the first electrode structure 310 with the first buried electrodes 515, the body zones 115 and the source zones 110 of the semiconductor mesas 150 that separate first and second cell trench structures 510, 520. Providing the first electrode structure 310 may include successive deposition of one or more conductive materials.

[0041] According to an embodiment, a barrier layer 311 having a uniform thickness in the range of 5 nm to 100 nm

may be deposited. The barrier layer may bar metal atoms from diffusing into the semiconductor substrate **500***a* and may be a layer of titanium nitride TiN, tantalum nitride TaN, titanium tungstenide TiW, titanium Ti or tantalum Ta, or may include these materials.

[0042] A main layer 312 may he deposited on the barrier layer 311. The main layer 312 may consist of or contain tungsten or tungsten based metals such as titanium tungstenide TiW, heavily doped polysilicon, carbon C, aluminum Al, copper Cu or alloys of aluminum and copper, such as AlCu or AlSiCu. At least one of the layers may be provided with a porous structure or may be deposited in a way to form voids or small cavities within the recesses 305y and/or the openings 305x. Voids and cavities in the recesses 305y, and openings 305x reduce mechanical stress.

[0043] FIG. 1D shows the first electrode structure 310 including the barrier layer 311 and the main layer 312. The thickness of the barrier layer 311 may he less than a half of the width of the recess 305y in FIG. 1C. According to another embodiment, the barrier layer 311 fills the recess 305y completely. The materials of the main layer 312 and the barrier layer 311 may fill the openings 305x in the capping layer 220 and the recesses 305y, in the semiconductor portion 100 completely to form solid contact structures 315 as shown in FIG. 1D.

[0044] FIG. 2 is related to other embodiments with the main layer 312 leaving voids 395 in the recesses 305y and the openings 305x.

[0045] FIGS. 3A to 3C refer to an embodiment that includes a widening of the recesses 305y. In first sections of first insulator layers 516 between first buried electrodes 515 and such semiconductor mesas 150 that are formed between first and second cell trench structures 510, 520 and that are exposed by openings 305x in a capping layer 220, recesses 305y may be formed between the first buried electrodes 515 and the concerned semiconductor mesas 150. An etch selectivity at which the material of the buried first electrode 515 is removed with respect to the material o semiconductor mesa 150 may he at least 5:1. The etch mask may be removed.

[0046] FIG. 3A shows the openings 305x in the capping layer 220 and the recesses 305v between the first buried electrodes 515 and the concerned semiconductor mesas 150. Contact openings 305 include an opening 305x and a recess 305y, respectively. A first etch step forms the opening 305 in the capping layer 220 and may stop at the first surface 101. A second etch step that may use the same etch process over-etches the first insulator layer 316 for a predetermined time. Using a different etch process, a third etch step widens at least the openings of the recesses 305y at the expense of either the adjoining semiconductor mesas 150 or the adjoining portions of the first buried electrodes 515 or both. For example, a short isotropic silicon etch may remove polycrystalline material, which may be used for the first buried electrodes 515, at a higher etch rate than the single crystalline semiconductor material of the semiconductor mesas

[0047] According to another embodiment, a first etch process forms the openings 305 in the capping layer 220 and stops at the first surface 101. A second etch step forms wide recesses 305y by using an etch process with lower selectivity than the first etch process such that a certain amount of the first buried electrodes 515 is recessed contemporaneously with the material of the first insulator layer 516. As a result,

the width of the semiconductor mesas 150 can be essentially maintained such that a channel portion along the second cell trench structure 520 remains unaffected from processes applied at the recesses 305y.

[0048] According to another embodiment, the etch selectivity of the process for generating the recesses 305y is gradually reduced with time such that the sidewall angles of the recess 305y become less steep. In both cases, the etch rate may be higher in the polycrystalline silicon material, which may be used for the first buried electrodes 515, than in the single crystalline semiconductor material of the semiconductor mesas 150. Processes widening the recesses 305y ease the later filling of the recesses 305y with the one or more contact materials without significantly reducing the dimensions of the semiconductor mesas 150.

[0049] According to an embodiment, an implant may be performed through the sidewalls of the recesses 305y to reduce a contact resistance to the body zones 115 and the risk of latch-up effects. For example, a BF2 implant may be performed. The implant may be activated through an RTA (rapid thermal anneal) to form heavily doped contact zones 117 along the sidewall portions of the semiconductor mesas 150 exposed by the widened recesses 305y. The contact zones 117 have the second conductivity type and do not reach the second cell trench structures 520 such that a variation of a threshold voltage due to impurities of the BF2 implant reaching the channel along the second insulator layer 526 can be avoided.

[0050] According to another embodiment, a plasma implant may be performed through the sidewalls of the widened recesses 305v to form conformal contact zones 117. Since the plasma implant counter-dopes portions of the source zones 110, the source zones 110 are provided with a sufficient high net impurity concentration.

[0051] FIG. 3B shows an angled implant 380 for introducing impurities of the second conductivity type into exposed sidewall portions of the semiconductor mesas 150 and the heavily doped contact zones 117 of the second conductivity type emerging from the angled implant 380 after anneal. In the case of tapered recesses 305y, the implant 380 may be an orthogonal implant perpendicular to the first surface 101. Otherwise, the implant angle with respect to the normal may he greater 0 degrees.

[0052] A barrier layer 311 may be deposited on the capping layer 220, wherein the barrier layer 311 lines the combined contact openings 305. A main layer 312 is deposited that may fill the contact openings 305 completely or that may leave voids in the contact openings 305.

[0053] FIG. 3C shows the first electrode structure 310 and the contact structures 315 formed in the contact openings 305. A slope of the contact openings 305 at a side oriented to the concerned semiconductor mesa 150 is steeper than a slope at the opposing side oriented to the concerned first buried electrode 515.

[0054] FIGS. 4A to 4D illustrate a semiconductor device 500 obtained from one of a plurality of identical semiconductor dies processed as a portion of the semiconductor substrate 500a of FIGS. 1A to 1D. The semiconductor device 500 may be a power switching device, e.g. an IGBT (insulated gate bipolar transistor) e.g. a PT-IGBT (punch through IGBT) or an IGFET.

[0055] The semiconductor device 500 includes a semiconductor portion 100 with a first surface 101 and a second surface 102 parallel to the first surface 101. The semicon-

ductor portion 100 is provided from a single-crystalline semiconductor material, for example silicon Si, silicon carbide SiC, germanium Ge, a silicon germanium crystal SiGe, gallium nitride GaN or gallium arsenide GaAs. A minimum distance between the first and second surfaces 101, 102 is selected to achieve a specified voltage blocking capability of the drift zone 120, for example 90 to 110  $\mu$ m for a 1200 V blocking IGBT. Other embodiments related to higher blocking devices or PT-IGBT device approaches may provide semiconductor portions 100 with a thickness of several 100  $\mu$ m distances between 101 and 102. Low voltage IGFETs may be thinner, e.g. at least some 10  $\mu$ m.

[0056] The semiconductor portion 100 may have a rectangular shape with an edge length in the range of several millimeters. The normal to the first and second surfaces 101, 102 defines a vertical direction and directions orthogonal to the normal direction are lateral directions.

[0057] First and second cell trench structures 510, 520 extend from the first surface 101 into the semiconductor portion 100. The first and second cell trench structures 510, 520 may have the same vertical dimensions and the same lateral dimensions. According to other embodiments, the lateral and/or vertical dimensions of the first and second cell trench structures 510, 520 differ from each other. The vertical extension may be in the range from 500 nm to 20  $\mu m$ , e.g. from 2  $\mu m$  to 7  $\mu m$ . The lateral width may be less than 2  $\mu m$ , e.g. less than 1.2  $\mu m$ .

[0058] The first cell trench structures 510 comprise first buried electrodes 515 and first insulator layers 516 separating the first buried electrodes 515 from the semiconductor material outside the first and second cell trench structures 510, 520. The first insulator layers 516 may have a uniform thickness in a range from 50 nm to 150 nm, e.g. between 80 nm and 120 nm, by way of example. The first cell trench structures 510 may or may not include further conductive structures, e.g. a further electrode dielectrically insulated from the first buried electrodes 515.

[0059] The second cell trench structures 520 include second buried electrodes 525 and second insulator layers 526 dielectrically insulating the second buried electrodes 525 from the semiconductor material outside the first and second cell trench structures 510, 520. The second cell trench structures 520 may include a further conductive structure, for example a further electrode dielectrically insulated from the second buried electrodes 525. The number of first and second cell trench structures 510, 520 may be equal. Other embodiments provide more first cell trench structures 510 than second cell trench structures 520. For example, at least two first cell trench structures 510 are provided between two second cell trench structures 520, respectively. The semiconductor mesas 150 between second cell trench structures 520 may or may not be connected to the source potential.

[0060] The first and second cell trench structures 510, 520 may be parallel stripes arranged in a regular pattern. According to other embodiments, the lateral cross-sectional areas of the cell trench structures 510, 520 may be circles, ellipses, ovals or rectangles, e.g. squares, with or without rounded corners, or rings. For example, two or three of the first and second cell trench structures 510, 520 may form an arrangement with two or three concentric rings, wherein the rings may be circles, ellipses, ovals, or rectangles, e.g. squares with or without rounded corners.

[0061] IGBT cells may be formed in the semiconductor portion 100 at a side oriented to the first surface 101,

wherein active areas of the IGBT cells are formed in first semiconductor mesas 150a separating one first cell trench structure 510 and one second cell trench structure 520, respectively. In the first semiconductor mesas 150a, source zones 110 of the first conductivity type may directly adjoin the first surface 101. The source zones 110 form first pn junctions with body zones 115 of the second conductivity type, wherein interfaces between the source and body zones 110, 115 run approximately parallel to the first surface 101 at a first distance d1. The body zones 115 form second pn junctions with a drift layer 120 of the first conductivity type at a third distance d3 to the first surface 101. The first and second cell trench structures 510, 520 extend through the source zones 110 and the body zones 115 into the drift layer 120

[0062] The illustrated embodiment refers to a fieldstop IGBT and the semiconductor portion 100 includes a collector layer 130 that directly adjoins the second surface 102. The collector layer 130 may be a contiguous layer of the second conductivity type. According to other embodiments related to, e.g. reverse conducting IGBTs, the collector layer 130 may include first portions of the first conductivity type and second portions of the second conductivity type, wherein the first and second portions alternate in one lateral direction or in both lateral directions. A mean net impurity concentration in the collector layer 130 may be at least  $1 \times 10^{16}$  cm<sup>-2</sup>, for example at least  $5 \times 10^{17}$  cm<sup>-3</sup>.

[0063] A second electrode structure 320 directly adjoins the second surface 102. The second electrode structure 320 is electrically connected to the collector layer 130 and may consist of or contain, as main constituent(s) aluminum Al, copper Cu, or alloys of aluminum or copper, such as AlSi, AlCu or AlSiCu. According to other embodiments, the collector electrode 320 may contain one, two, three or more sub-layers, wherein each sub-layer contains, as main constituent(s), at least one of nickel Ni, titanium Ti, silver Ag, gold. Au, tungsten W, platinum Pt and/or palladium Pd. For example, a sub-layer may contain a metal silicide, a metal nitride, or a metal alloy containing Ni, Ti, Ag, Au, W, Pt, and/or Pd. For IGBTs, the second electrode structure 320 provides a collector electrode that may provide or may be electrically connected to a collector terminal C of the semiconductor device 500.

[0064] In the drift layer 120, a field stop layer 128 may be provided between the collector layer 130 and a drift zone 121. A mean net impurity concentration in the field stop layer 128 may be between  $5 \times 10^{15}$  cm<sup>3</sup> and  $1 \times 10^{17}$  cm<sup>-3</sup>. The mean net impurity concentration in the drift zone 121 is lower than in the field stop layer 128. According to an embodiment, the mean net impurity concentration in the field stop layer 128 exceeds at least five times the mean net impurity concentration in the drift zone 121. The mean net impurity concentration in the drift zone 121 may be between  $5\times10^{12}$  cm<sup>-3</sup> and  $5\times10^{14}$  cm<sup>-</sup>, by way of example. For IGFETs, a heavily doped contact layer of the first conductivity type replaces the collector layer 130 and the second electrode structure 320 provides a drain electrode that may provide or may be electrically connected to a drain terminal of the semiconductor device 500.

[0065] The second buried electrodes 525 provide insulated gate electrodes Ga. A potential applied to the insulated gate electrodes Ga controls a minority charge carrier distribution in channel portions 115a of the body zones 115, wherein the channel portions 115a adjoin the second cell trench struc-

tures 520 between the source zones 110 and the drift layer 120. If in a forward biased mode the potential applied to the insulated gate electrodes Ga exceeds a predefined threshold voltage, inversion channels of the first conductivity type are formed in the body zones 115 along the second insulator layers 526, which are effective as gate dielectrics, and an on-state current flows between the source zones 110 and the drift layer 120. The insulated gate electrodes Ga may be electrically connected to a third electrode structure 330 that may provide or may be electrically connected or coupled to a gate terminal G of the semiconductor device 500.

[0066] Second semiconductor mesas 150b between first cell trench structures 510 may or may not include source zones 110. In the latter case, the body zones 115 may extend between the first surface 101 and the drift layer 120.

[0067] The first cell trench structures 510 provide buried source electrodes S that may be electrically connected to an emitter terminal E of the semiconductor device 500. The insulated gate electrodes Ga are insulated from the buried source electrodes S. At least the second cell trench structures 520 may include a capping dielectric 210 between the first surface 101 and the second buried electrodes 525 to reduce an overlap between the insulated gate electrodes Ga and the source zones 110. Other embodiments may provide contacts to some or all of the second semiconductor mesas 150.

[0068] A dielectric capping layer 220 may dielectrically insulate at least the second cell trench structures 520 and the second semiconductor mesas 150b from a first electrode structure 310 disposed at a side defined by the first surface 101. First contact structures 315 electrically connect the first electrode structure 310 with the first semiconductor mesas 150a and such first cell trench structures 510 that directly adjoin the first semiconductor mesas 150a. Second contact structures 316 electrically connect the first electrode structure 310 with other first cell trench structures 510 not directly adjoining the first semiconductor mesas 150a.

[0069] Each of the first contact structures 315 includes a first section 315a in an opening of the capping layer 220 and a second section 315h between a first semiconductor mesa 150a and a first cell trench structure 510 directly adjoining the first semiconductor mesa 150a. The second section 315b extends from the first surface 101 into the semiconductor portion 100. A second distance d2 between the first surface 101 and the buried edge of the second section 315b is greater than the first distance d1 and smaller than the third distance d3.

[0070] The second sections 315b of the first contact structures 315 may have approximately vertical sidewalls. According to an embodiment, the sidewalls for the second sections 315b taper with increasing distance to the first surface 101.

[0071] According to an embodiment, first sidewalls of the second sections 315b of the first contact structures 315 are tilted to the first surface 101 and directly adjoin the first semiconductor mesas 150a, Second sidewalls of the second sections 315b of the first contact structures 315 may be tilted to the first surface 101 and directly adjoin the first buried electrodes 510. The first sidewalk oriented to the first semiconductor mesas 150 and the second sidewalls oriented to the first buried electrodes 510 may have identical slope angles. The second sidewalls may deviate to a higher degree from a normal to the first surface 101 than the first sidewalls of the second sections 315b of the first contact structures 315.

[0072] The second sections 315b of the first contact structures 315 are located in the vertical projection of first sections of the first insulator layers 516. The first insulator layers 516 may have a uniform width, wherein the width of the first insulator layers 516 may be equal to or less than a width of the second sections 315h of the first contact structures 315. The first contact structures 315 are deep enough to provide a direct contact to the body zones 115, [0073] Heavily doped contact zones 117 may be formed in the body zones 115 of the first semiconductor mesas 150a along the interfaces to the first contact structures 315. The second electrode structure 310 as well as the third electrode structure 330 may include at least one barrier layer 311, 331, respectively. The barrier layer may have a uniform thickness in the range of 5 nm to 100 nm and may consist of or include a layer of titanium nitride TiN, tantalum nitride TaN, titanium tungstenide TiW, titanium Ti or tantalum Ta, by way of example. The main layers 312, 332 may consist of or contain tungsten or tungsten-based metals like titanium tungstenide TiW, heavily doped polysilicon, carbon C, aluminum Al, copper Cu or alloys of aluminum and copper, for example AlCu or AlSiCu.

[0074] The first and second contact structures 315, 316 may be solid contact structures, may include a porous layer or may have voids as shown in FIG. 2. The source zones 110 may be provided as narrow stripes and may alternate with portions of the body zones 115 in a lateral direction parallel to stripe shaped first and second cell trench structures 510, 520

[0075] Uncertainties and inequalities of different lithographic layers resulting in a misalignment between contact structures and semiconductor mesas limit a minimal mesa width conventionally at about 600 nm instead, the semiconductor device 500 of FIGS. 4A to 4D facilitates narrowing the width of the semiconductor mesas to less than 300 nm, for example less than 200 nm.

[0076] Further embodiments concern layout modifications of the first and second trench structures 510, 520 to further reduce an effective channel width for increasing short-circuit ruggedness, e.g. by segmenting the second cell trench structures 520 or by increasing locally a thickness of the second insulator layers 526.

[0077] Although specific embodiments have been illustrated and described herein, it will be appreciated by those of ordinary skill in the art that a variety of alternate and/or equivalent implementations may be substituted for the specific embodiments shown and described without departing from the scope of the present invention. This application is intended to cover any adaptations or variations of the specific embodiments discussed herein. Therefore, it is intended that this invention be limited only by the claims and the equivalents thereof.

What is claimed is:

- 1. A semiconductor device, comprising:

- a plurality of source zones of a first conductivity type formed in a semiconductor substrate;

- a plurality of body zones of a second conductivity type opposite the first conductivity type formed in the semi-conductor substrate below the plurality of source zones;

- a plurality of heavily doped contact zones formed in the body zones;

- a plurality of first stripe-shaped cell trench structures formed in the semiconductor substrate and extending lengthwise in parallel with one another, each first

- stripe-shaped cell trench structure comprising a first buried electrode and a first insulator layer between the first buried electrode and the semiconductor substrate;

- a plurality of second stripe-shaped cell trench structures formed in the semiconductor substrate and extending lengthwise in parallel with one another, each second stripe-shaped cell trench structure comprising a second buried electrode and a second insulator layer between the second buried electrode and the semiconductor substrate;

- a recess formed in the first insulator layer along a sidewall of one or more of the first stripe-shaped cell trench structures and vertically extending to the corresponding heavily doped contact zone; and

- an electrically conductive material disposed in each recess formed in the first insulator layer and contacting the corresponding first buried electrode, the corresponding source zone and the corresponding heavily doped contact zone at the sidewall,

- wherein two or more of the first stripe-shaped cell trench structures are interposed between neighboring ones of the second stripe-shaped cell trench structures,

- wherein the source zones alternate with portions of the body zones in a lateral direction parallel to the first and second stripe-shaped cell trench structures.

- 2. The semiconductor device of claim 1, wherein the sidewall of the one or more first stripe-shaped cell trench structures with the recess is tilted by less than 90 degrees with respect to a first main surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures d the plurality of second stripe-shaped cell trench structures extend.

- 3. The semiconductor device of claim 1, wherein the first insulator a n width.

- 4. The semiconductor device of claim 1, wherein the width of each recess increases with increasing proximity to a first main surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures and the plurality of second stripe-shaped cell trench structures extend.

- 5. The semiconductor device of claim 1, wherein the width of the first buried electrode in each first stripe-shaped cell trench structure with a recessed first insulator layer decreases with increasing proximity to a first main surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures and the plurality of second stripe-shaped cell trench structures extend.

- **6**. The semiconductor device of claim **5**, wherein the width of the first buried electrode in each first stripe-shaped cell trench structure with a recessed first insulator layer is generally uniform below the recess.

- 7. The semiconductor device of claim 1, further comprising a capping layer formed on a first main surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures and the plurality of second stripe-shaped cell trench structures extend, wherein the electrically conductive material disposed in each recess formed in the first insulator layer extends through openings in the capping layer to form part of an overlying contact structure.

- 8. The semiconductor device of claim 7, wherein the first buried electrode of one or more of the first stripe-shaped cell trench structures is electrically contacted by the contact

- structure through an additional opening in the capping layer which is aligned with a top side of the first buried electrode.

- 9. The semiconductor device of claim 1, wherein the first buried electrodes are electrically coupled to a source potential, and wherein the second buried electrodes are electrically coupled to a gate potential.

- 10. The semiconductor device of claim 1, wherein the semiconductor device is an IGBT.

- 11. The semiconductor device of claim 1, wherein between neighboring ones of the source zones, a body zone extends to a first main surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures and the plurality of second stripe-shaped cell trench structures extend.

- 12. The semiconductor device of claim 1, wherein interfaces between the source zones and the body zones run approximately parallel to a first surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures and the plurality of second stripe-shaped cell trench structures extend at a first distance, wherein a second distance between the first surface and an edge of the electrically conductive material at a bottom of each recess formed in the first insulator layer is greater than the first distance, wherein interfaces between the body zones and a drift layer of the first conductivity type run approximately parallel to the first surface at a third distance, and wherein the second distance is smaller than the third distance.

- 13. The semiconductor device of claim 1, wherein between first stripe-shaped cell trench structures of the plurality of first stripe-shaped cell trench structures for which the first buried electrode is contacted by the electrically conductive material through the recess formed in the corresponding first insulator layer, the buried electrode of at least one first stripe-shaped cell trench structure of the plurality of first stripe-shaped cell trench structure is contacted by the electrically conductive material only at a first main surface of the semiconductor substrate.

- **14.** A method of manufacturing a semiconductor device, the method comprising:

- forming a plurality of source zones of a first conductivity type in a semiconductor substrate;

- forming a plurality of body zones of a second conductivity type opposite the first conductivity type in the semiconductor substrate below the plurality of source zones;

- forming a plurality of heavily doped contact zones in the body zones;

- forming a plurality of first stripe-shaped cell trench structures in the semiconductor substrate and extending lengthwise in parallel with one another, wherein each first cell trench structure comprises a first buried electrode and a first insulator layer between the first buried electrode and the semiconductor substrate;

- forming a plurality of second stripe-shaped cell trench structures in the semiconductor substrate and extending lengthwise in parallel with one another, wherein two or more of the first stripe-shaped cell trench structures are interposed between neighboring ones of the second stripe-shaped cell trench structures, wherein each second stripe-shaped cell trench structure comprises a second buried electrode and a second insulator layer between the second buried electrode and the semiconductor substrate;

- forming a recess in the first insulator layer along a sidewall of one or more of the first stripe-shaped cell trench structures and vertically extending to the corresponding heavily doped contact zone; and

- disposing an electrically conductive material in each recess formed in the first insulator layer so as to contact the corresponding first buried electrode, the corresponding source zone and the corresponding heavily doped contact zone at the sidewall,

- wherein the source zones alternate with portions of the body zones in a lateral direction parallel to the first and second stripe-shaped cell trench structures.

- 15. The method of claim 14, wherein forming the recess in the first insulator layer along a sidewall of the one or more first stripe-shaped cell trench structures comprises tilting the sidewall of the one or more first stripe-shaped cell trench structures by less than 90 degrees with respect to a first main surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures and the plurality of second stripe-shaped cell trench structures extend.

- 16. The method of claim 15, wherein tilting the sidewall of the one or more first stripe-shaped cell trench structures by less than 90 degrees with respect to the first main surface of the semiconductor substrate comprises removing a material of the buried first electrode at an etch selectivity with respect to a material of the semiconductor substrate of at least 5:1.

- 17. The method of claim 14, wherein forming the recess in the first insulator layer along a sidewall of the one or more first stripe-shaped cell trench structures comprises decreas-

- ing the width of each recess with decreasing proximity to a first main surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures and the plurality of second stripe-shaped cell trench structures extend.

- 18. The method of claim 17, wherein the width of the first buried electrode in each first stripe-shaped cell trench structure with a recessed first insulator layer is generally uniform below the recess.

- 19. The method of claim 14, further comprising: forming a capping layer on a first main surface of the semiconductor substrate into which the plurality of first stripe-shaped cell trench structures and the plurality of second stripe-shaped cell trench structures extend, wherein the electrically conductive material disposed in each recess formed in the first insulator layer extends through openings in the capping layer to form part of an overlying contact structure.

- 20. The method of claim 19, further comprising: electrically contacting the first buried electrode of one or more of the first stripe-shaped cell trench structures by the contact structure through an additional opening in the capping layer which is aligned with a top side of the first buried electrode.

- 21. The method of claim 14, further comprising: electrically coupling the first buried electrodes to a source potential; and

- electrically coupling the second buried electrodes to a gate potential.

\* \* \* \* \*